HDMI发送器学习——SII7170

原创HDMI发送器学习——SII7170

原创(文章的主要目的还是学习记录以及学习输出,若是文中有任何描述不对的地方,欢迎大家在评论区交流指出~)

基本介绍

Sil7170是矽映电子(Silicon Image)公司下的一款iTMDS发送器,当然Silicon Image早已经被Lattice半导体公司收购。

SiI7170发送器采用iTMDS内部面板互连数字技术,可支持的显示分辨率高达WUXGA。

TMDS技术

TMDS(Transition Minimized Differential Signaling)最小化传输差分信号,是Silicon Image公司开发的一项高速数据传输技术,能够应用在DVI(Digital Video Interface数字视频接口)和HDMI(High Definition Multimedia Interface高清多媒体接口)视频接口中使用差分信号传输高数串行数据。

TMDS技术利用差分信号之间的电压差来传输信号,每一个标准的HDMI接口都包括3对用于传输数据的TMDS差分传输通道,以及1对差分TMDS时钟通道,用于源同步,保证传输时时序的统一。

SiI7170基本特性

- 完全符合TMDS/iTMDS,同时在DVI 1.0环境中完全可互操作

- 可扩展带宽范围:25-225MHz(VGA-WUXGA)标准像素输入速率,高色深支持最高225MHz

- 支持24位,30位,36位和48位色深

- SiI7170:2位像素输入支持24、30和36位的数据,1位像素输入最高可支持48位的数据

- 扩展频谱时钟接口能够显著减低EMI

- 支持长电缆:超过20m的DVI电缆

- 包含片上输入时钟抖动滤波器能够保障到达接收器端的信号足够干净

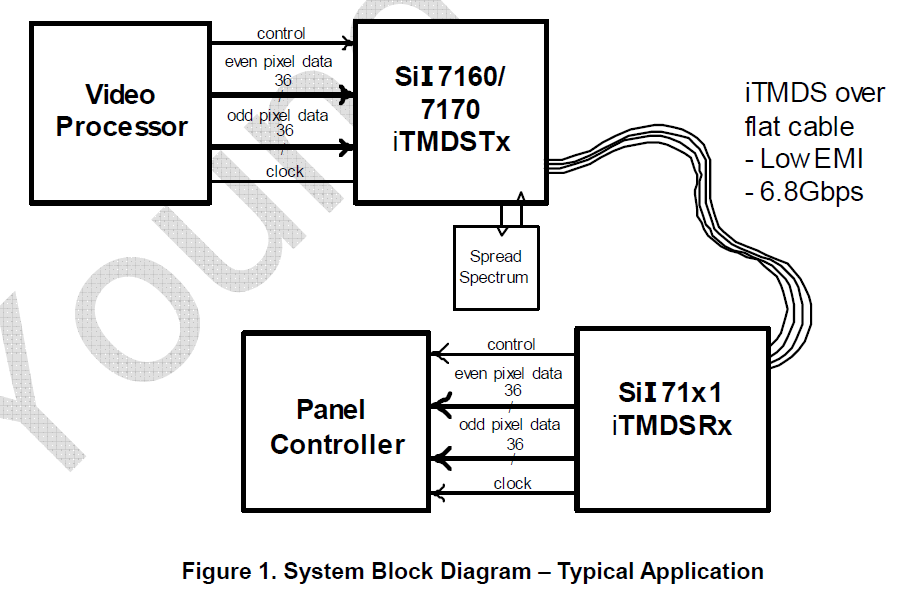

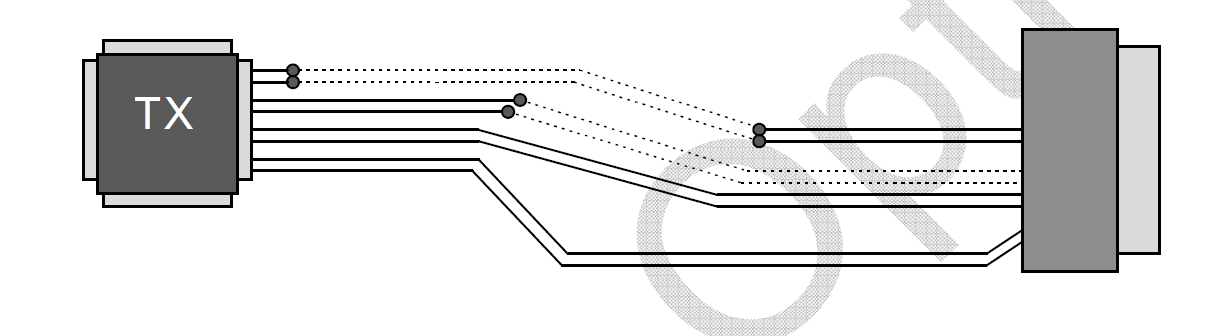

以下是视频发送和接收器的典型应用实例图。

从视频处理器通过ITMDS发送器发送数据到iTMDS接收器接收到显示器上显示

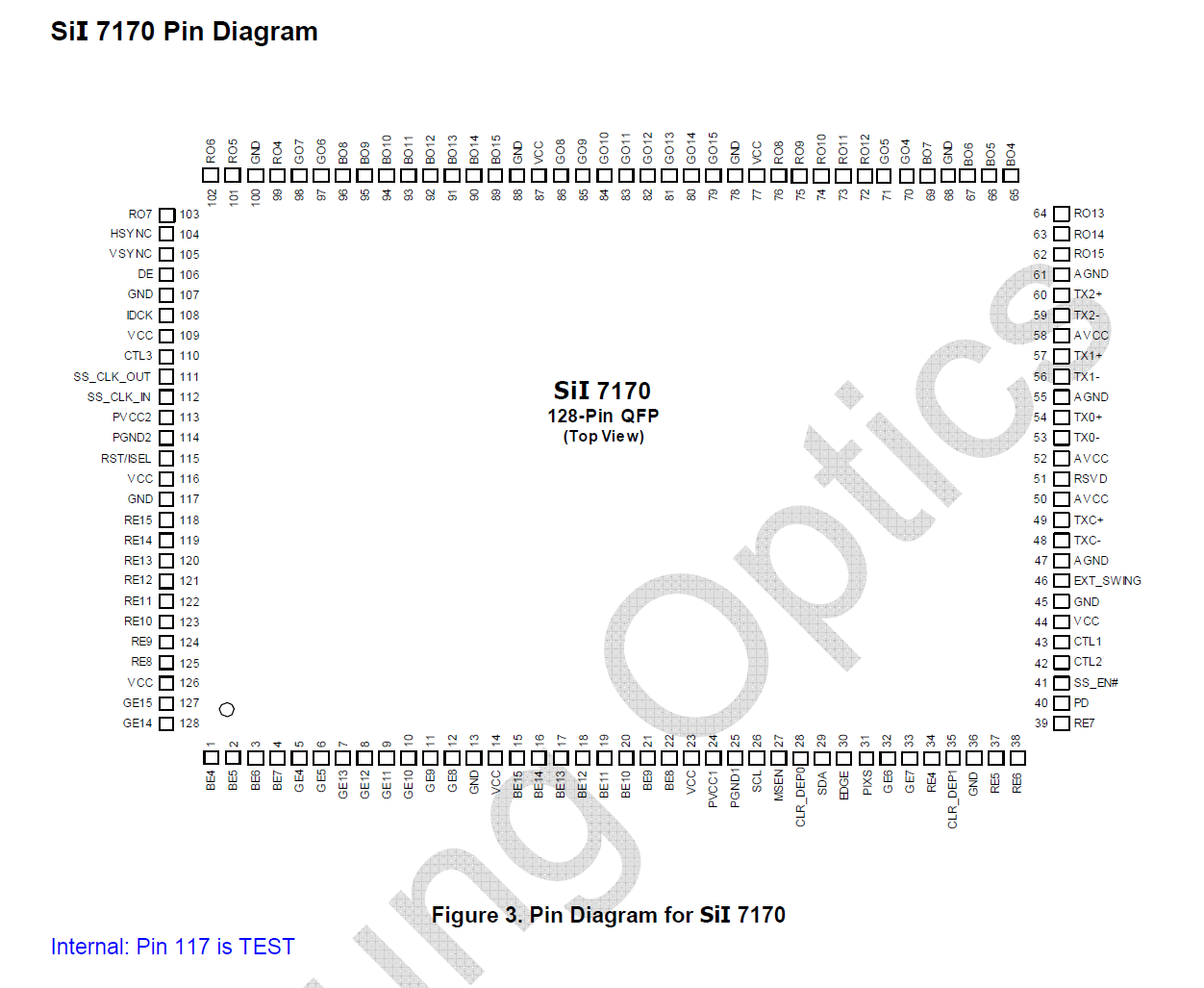

SiI7170的管脚图如下图所示。

添加图片注释,不超过 140 字(可选)

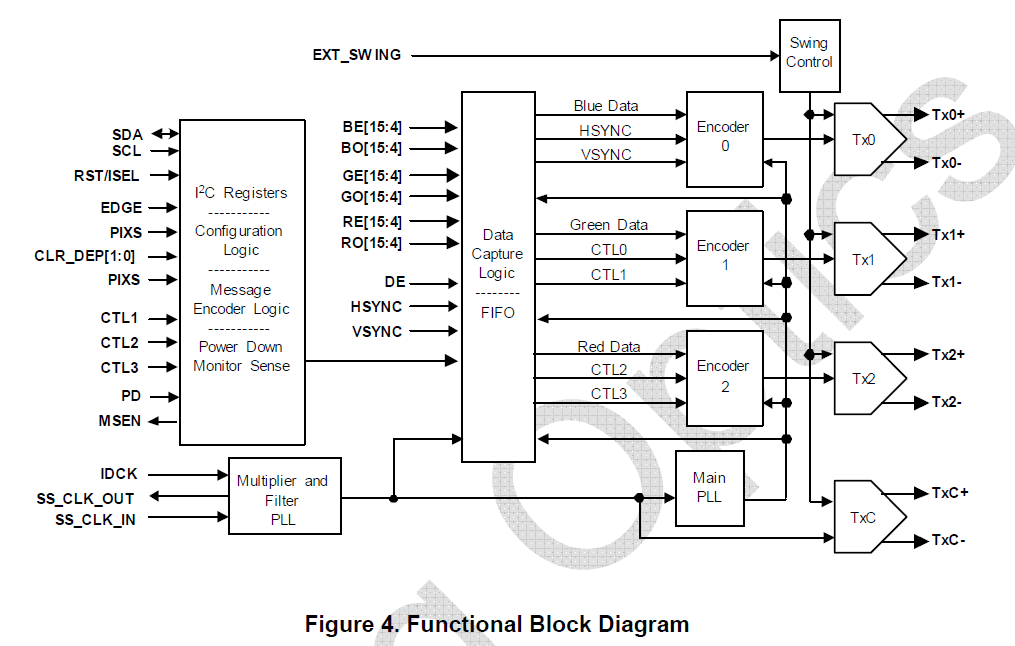

SiI7170芯片的功能框图如下图所示。

该图的具体的解释见下文

数据捕获逻辑和FIFO(Data Capture Logic and FIFO)

- 输入数据接口允许在每个时钟以1位/2位像素(单边沿/双边沿)向iTMDS编码器逻辑提供合理的数据,数据输入可接受24、30、36或48位的配置。

- 从数据输入到编码器之间的FIFO能够支持由于时钟调制(扩频时钟)导致的扩频容差,允许多种不同格式的输入以标准iTMDS 8b/10b编码方式传输。

(当然这里的iTMDS 8b/10b编码,简单来说就是传输的10bit数据中包括8位有效数据信息,具体的编码标准有时间的话会再写一篇文章进行说明和补充)

iTMDS编码逻辑(iTMDS Encoder Logic)

- 内部面板互连iTMDS内核会将视频信息编码成3对iTMDS差分数据,并将时序和抖动信息输出在1对iTMDS时钟差分信号上,视频信息从上述的数据捕获逻辑单元输入。

- 连接在EXT_SWING信号上的电阻用于控制iTMDS的摆幅(这里我理解的是差分信号的摆幅?)

1. 该发送器可支持I2C模式或非I2C模式

- 在非I2C模式下,该芯片仅依靠外部引脚进行操作配置(Strap:应该是芯片方面相关的术语,表示启动配置电路)。

- 在I2C模式下,该芯片作为从机方,支持400kHz的通信速率;I2C寄存器配置能够覆盖外部管脚配置,同时能够提供额外的控制能力。需要注意的是该芯片的I2C管脚不支持5V,最高支持3.3V,若主机的I2C信号线电平与之不匹配需要进行电平转换。

2. 与显示设备连接上时,能够通过MSEN管脚(若是使能的话)读取到状态的跳转。

3. 器件带有断电管脚PD,复位管脚为RST/ISEL。

4. EDGE引脚用于控制时钟极性或者作为锁存数据第一像素的时钟沿。

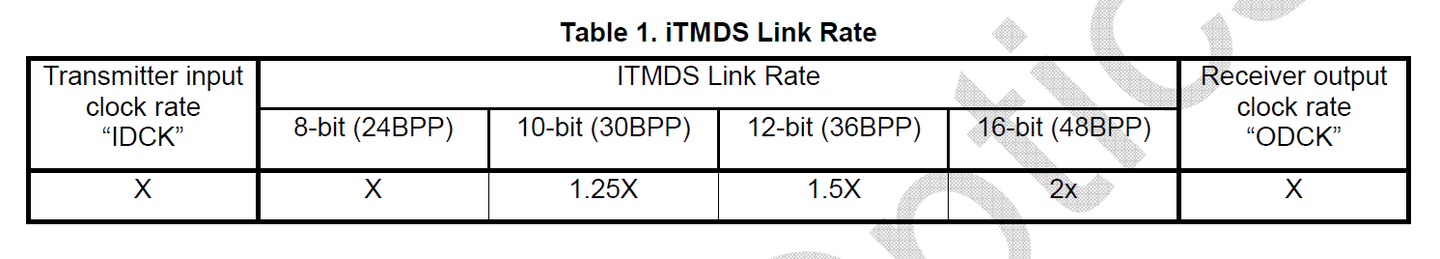

高色深(>8bit)会引起iTMDS链路速率的上升,但不会影响发送器输入时钟速率IDCK。

添加图片注释,不超过 140 字(可选)

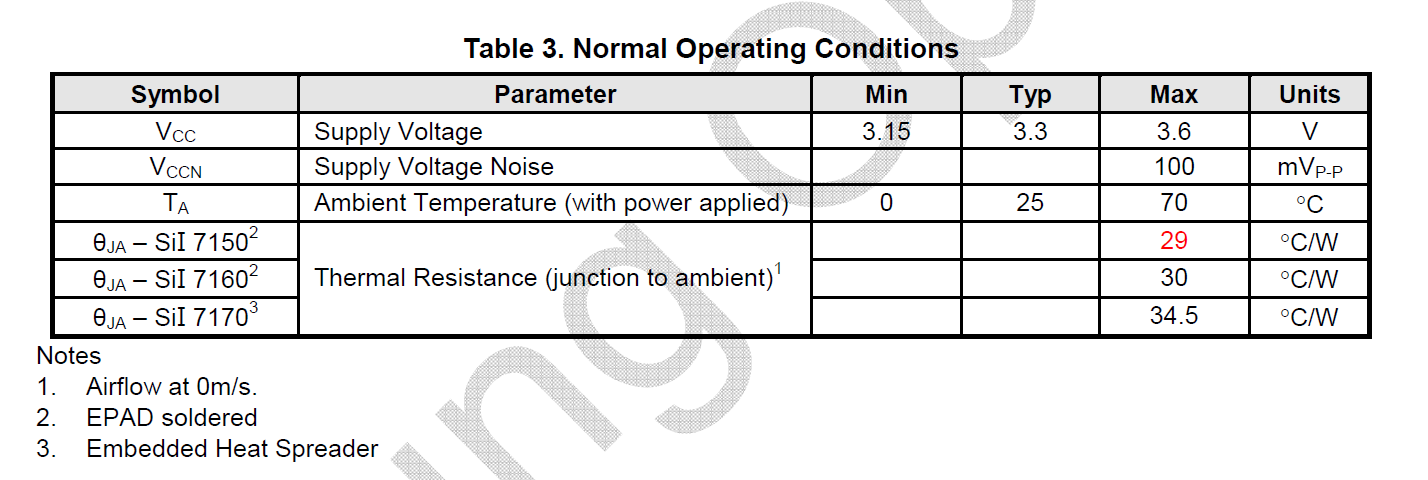

SiI7170正常操作条件

3.3V

添加图片注释,不超过 140 字(可选)

SiI7170管脚说明

输入管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

RE[15:4]GE[15:4]BE[15:4] | I | 输入偶数据在1位像素模式下表示MSB,在2位像素模式下表示第一位像素数据通过IDCK时钟信号进行源同步,当EDGE为高电平时,数据在上升沿锁存,为低电平时,数据在下降沿锁存 |

RO[15:4]GO[15:4]BO[15:4] | I | 输入奇数据在1位像素模式下表示LSB,在2位像素模式下表示第二位像素数据,当管脚未使用时接低通过IDCK时钟信号进行源同步,当EDGE为高电平时,数据在上升沿锁存,为低电平时,数据在下降沿锁存 |

CTL1 | I | 控制信号输入 |

CTL2 | I | 控制信号输入 |

CTL3 | I | 控制信号输入 |

IDCK | I | 输入数据时钟通过EDGE信号可以选择数据和控制信号在IDCK时钟信号的上升沿或者下降沿有效 |

DE | I | 输入数据使能该信号指示有效信号范围,高电平有效 |

HSYNC | I | 水平同步输入控制信号 |

VSYNC | I | 垂直同步输入控制信号 |

配置管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

EDGE | I | 数据/控制锁存沿低电平表示所有输入信号在下降沿锁存(HSYNC、VSYNC、DE和CTL[3:1]),高电平表示输入信号在上升沿锁存;当I2C接口使能时(ISEL/RST=LOW),EDGE寄存器位将取代该位管脚的功能 |

PIXS | I | 像素选择低电平指示1位像素模式(最高24位)使用输入偶数据,高电平指示2位像素模式(最高48bit)使用偶数据位作为第一位像素,奇数据作为第二位像素 |

SS_CLK_IN | I | 扩频时钟输入SS_EN#=0时使能 |

SS_CLK_OUT | O | 扩频时钟输出SS_EN#=0时使能 |

SS_EN# | I | 扩频使能低电平有效 |

CLR_DEP0 | I | 色深选择0 |

CLR_DEP1 | I | 色深选择1 |

I2C接口相关管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

RST/ISEL | I | I2C复位/I2C接口选择低电平时指示I2C接口有效,高电平时I2C接口未使能,同时能作为I2C接口的复位信号使用 |

MSEN | O | 监视器感知I2C未使能时高电平指示监测到接收器上电低电平指示未监测到接收器上带你I2C使能时该输出可通过I2C编程输出 |

SCL | I | I2C时钟需要上拉到3.3V,上拉电阻建议2-5KΩ(2.2KΩ),不支持5V |

SDA | I/O | I2C数据需要上拉到3.3V,上拉电阻建议2-5KΩ(2.2KΩ),不支持5V |

电源管理管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

PD | I | 断电/复位低电平有效,低电平时所有的输入信号都处于未使能状态,所有的输出皆处于三态,所有的内部电路除扩频时钟生成外皆断电,高电平时芯片处于正常工作状态但只有处于非I2C模式该管脚才有效,处于I2C模式时该管脚的功能被PD寄存器位取代,在I2C模式时需要被拉低。 |

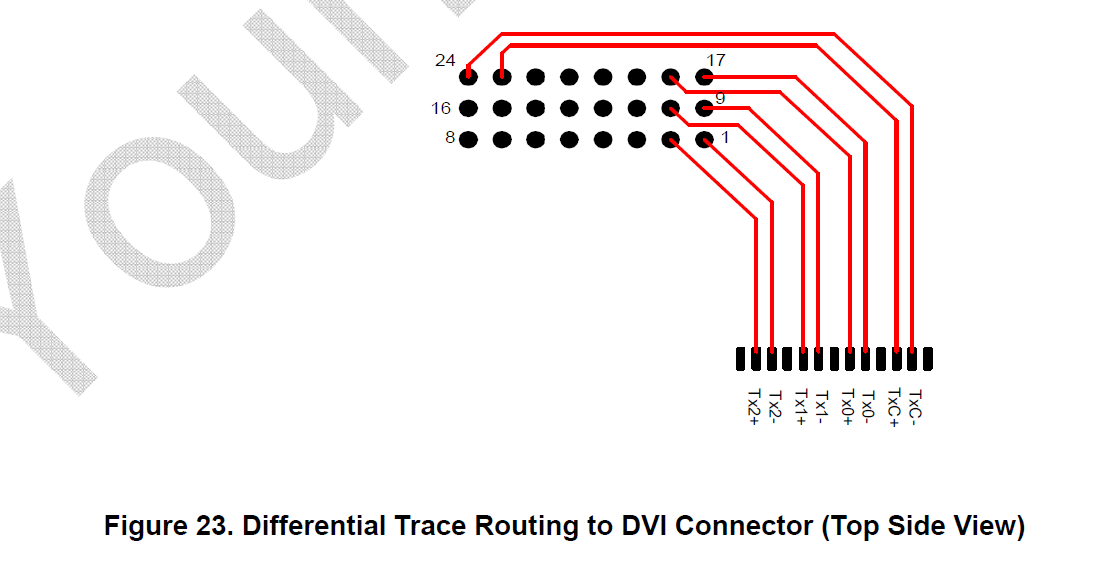

差分数据信号说明。

SiI7170Pin # | Type | Description |

|---|---|---|

TX0+TX0-TX1+TX1-TX2+TX2- | Analog | TMDS低电平差分输入数据对 |

TXC+TXC- | Analog | TMDS低电平差分输入时钟对 |

EXT_SWING | Analog | 电压摆幅调整通过与AVCC连接的电阻值决定电压的摆幅,更小的阻值将得到更大的电压摆幅,反之亦然。带源端的远距离显示推荐510Ω的电阻,无源端的显示推荐600Ω的电阻。 |

保留管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

RSVD | -- | 保留不连接 |

电源及地管脚说明。

SiI7170Pin # | Type | Description |

|---|---|---|

VCC | Power | 数字核心VCC,3.3V |

GND | Ground | 数字核心GND |

AVCC | Power | 模拟VCC,3.3V |

AGND | Ground | 模拟GND |

PVCC1 | Power | 主要的PLL模拟VCC,3.3V |

PVCC2 | Power | 滤波PLL模拟VCC,3.3V |

PGND1 | Ground | PLL模拟GND,应和PGND2分别与GND相连 |

PGND2 | Ground | PLL模拟GND,应和PGND1分别与GND相连 |

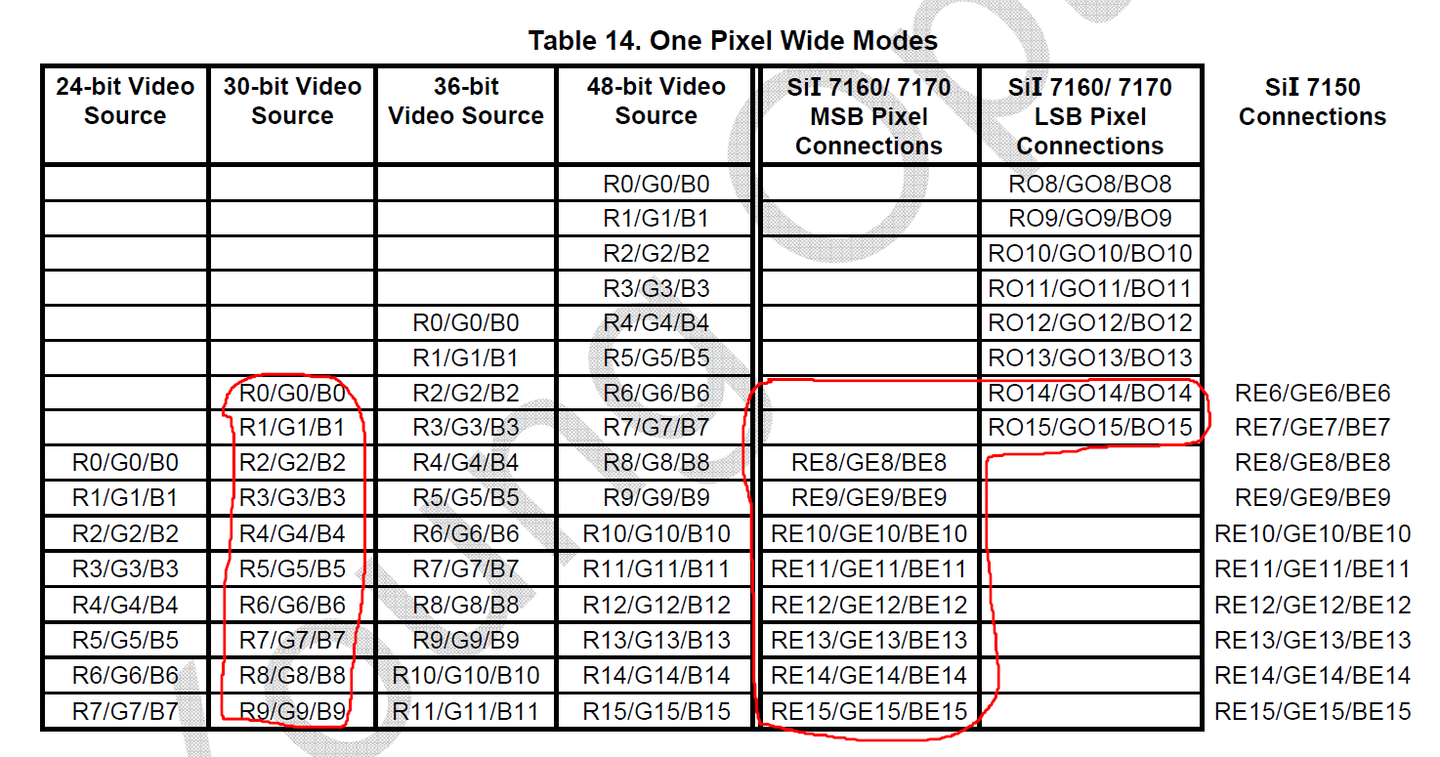

一位像素位宽模式

其中CLP_DEP[1:0]用于选择24/30/36/48色深。

处于一位像素位宽模式时,PIXS管脚应该接低。

添加图片注释,不超过 140 字(可选)

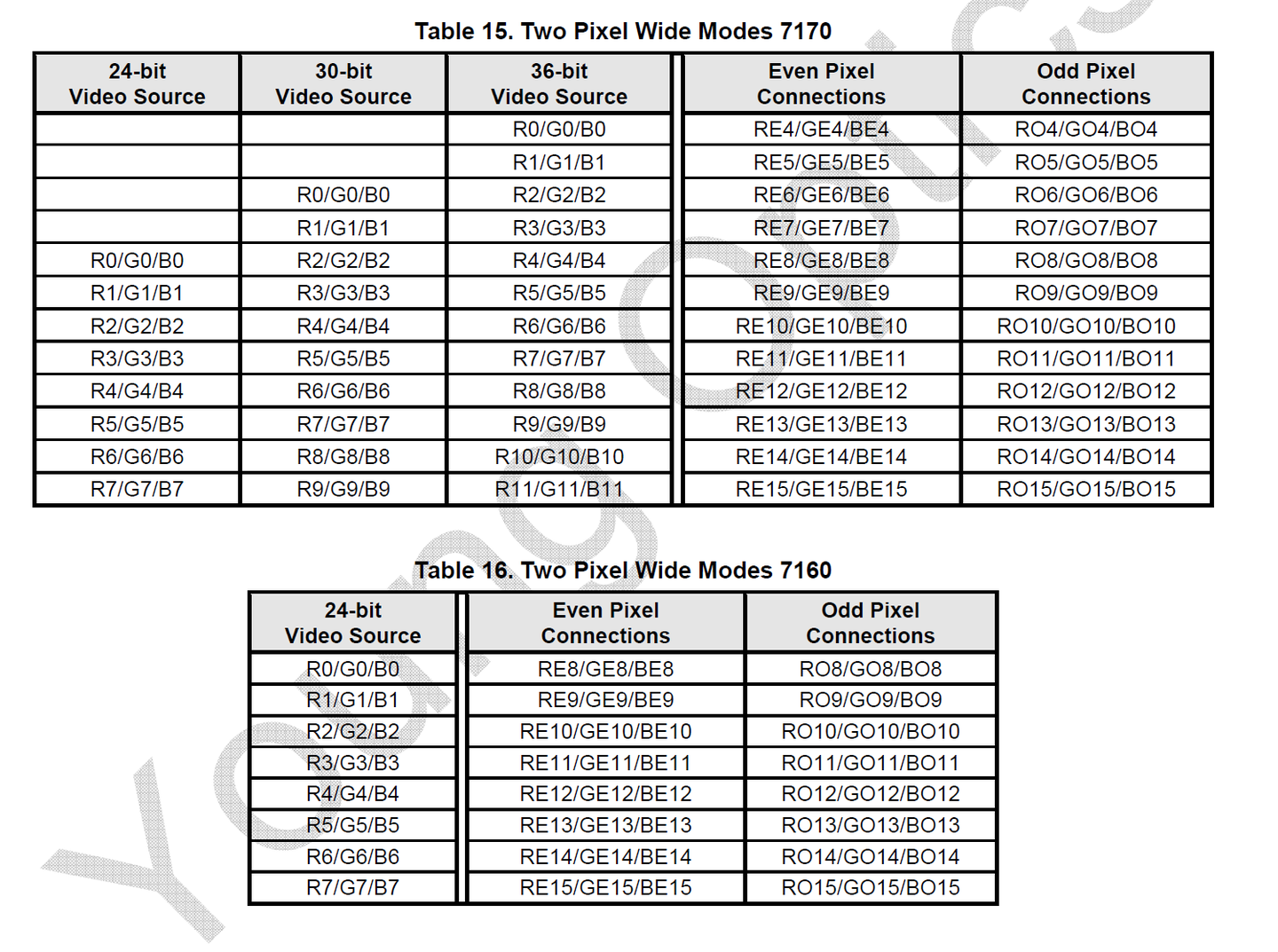

两位像素位宽模式

其中CLP_DEP[1:0]用于选择24/30/36/48色深。

处于两位像素位宽模式时,PIXS管脚应该接高。

添加图片注释,不超过 140 字(可选)

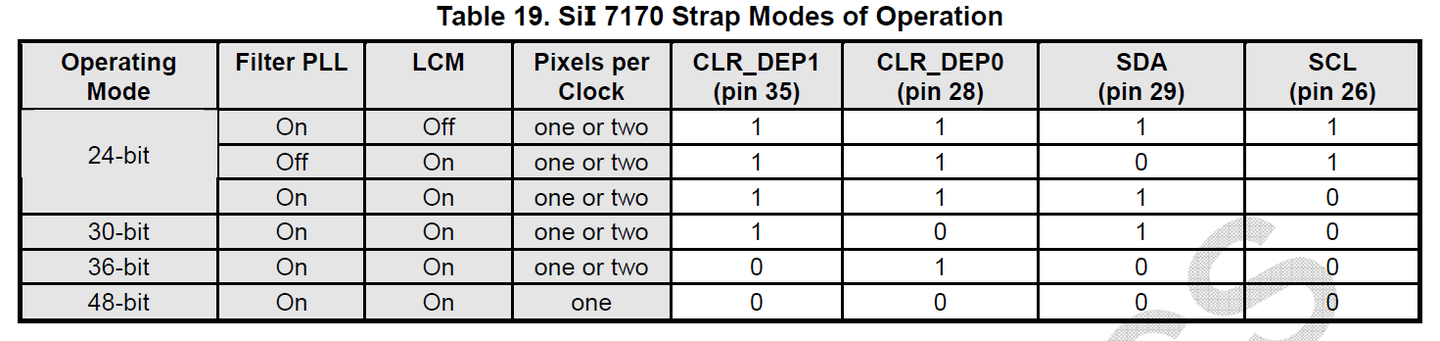

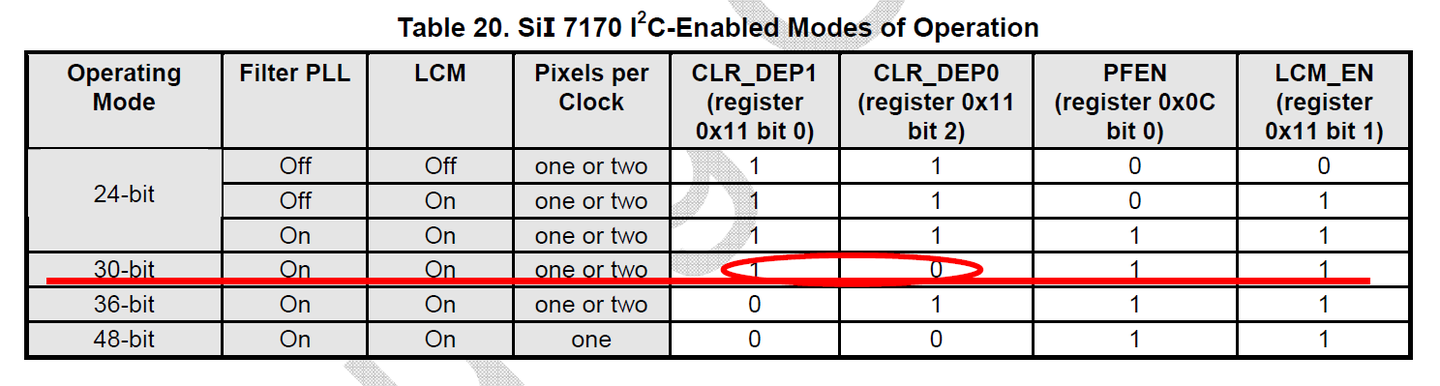

Sil7170工作模式

当Sil7170处于strap-controlled模式时,RST/ISEL管脚应该接高。

添加图片注释,不超过 140 字(可选)

当Sil7170处于I2C模式时:

- RST/ISEL管脚应该接低

- PD寄存器位(I2C寄存器地址0x8的位0)应该写1

I2C寄存器配置默认24-bit模式和LCM关闭,其他模式可配置。

添加图片注释,不超过 140 字(可选)

I2C接口

SiI7170可以通过RST/ISEL管脚选择是否使用I2C接口实现一些精密的配置操作。

仅使用SCL时钟就可以对I2C地址从0x00到0x0F的寄存器进行读写操作。

该I2C的7位地址是0x70,对I2C进行读写操作时需要先向I2C地址的bit0写入0使能写操作,写入1使能读操作。

该I2C不支持Page模式。具体的读写操作时序如下图所示。

添加图片注释,不超过 140 字(可选)

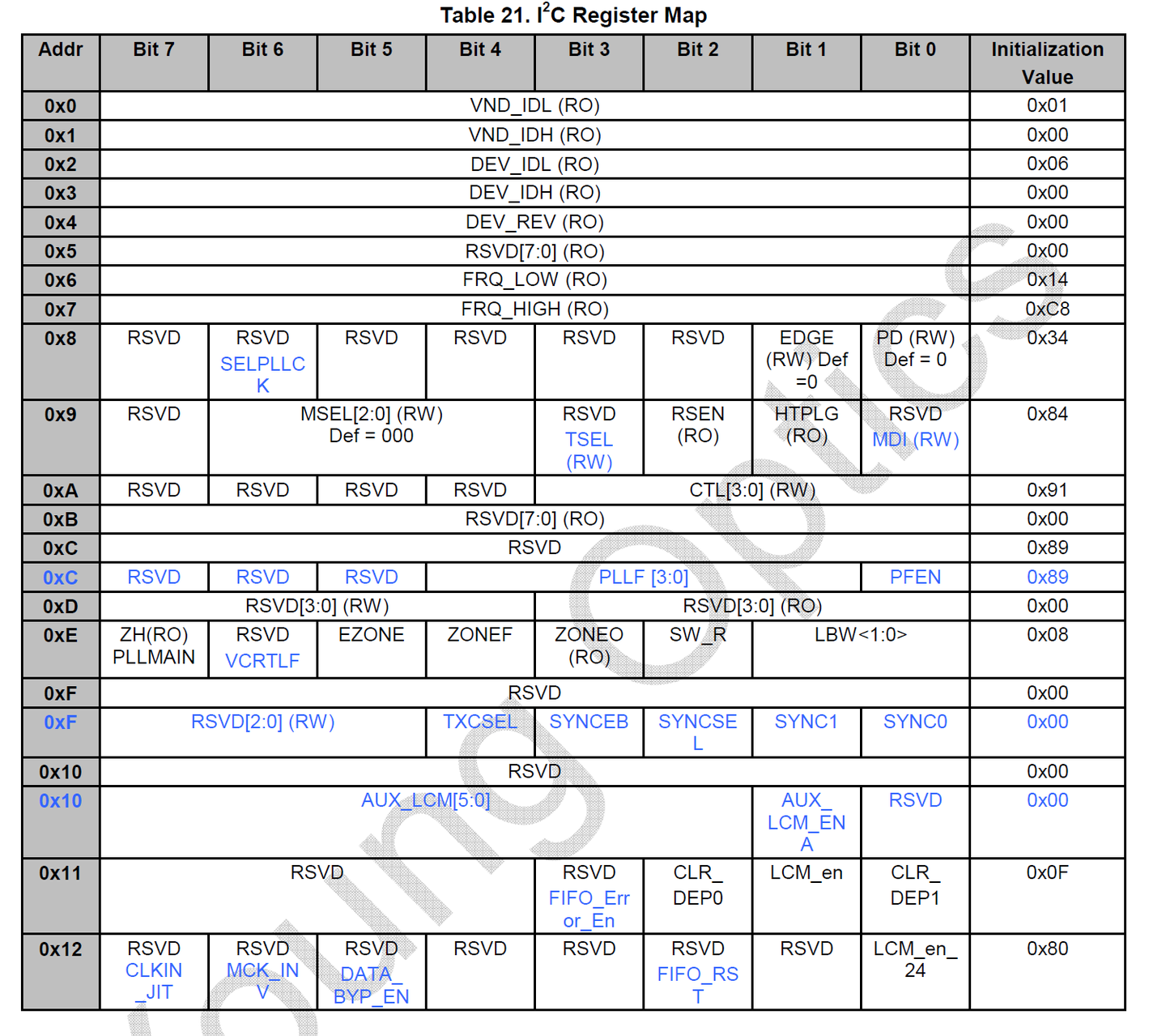

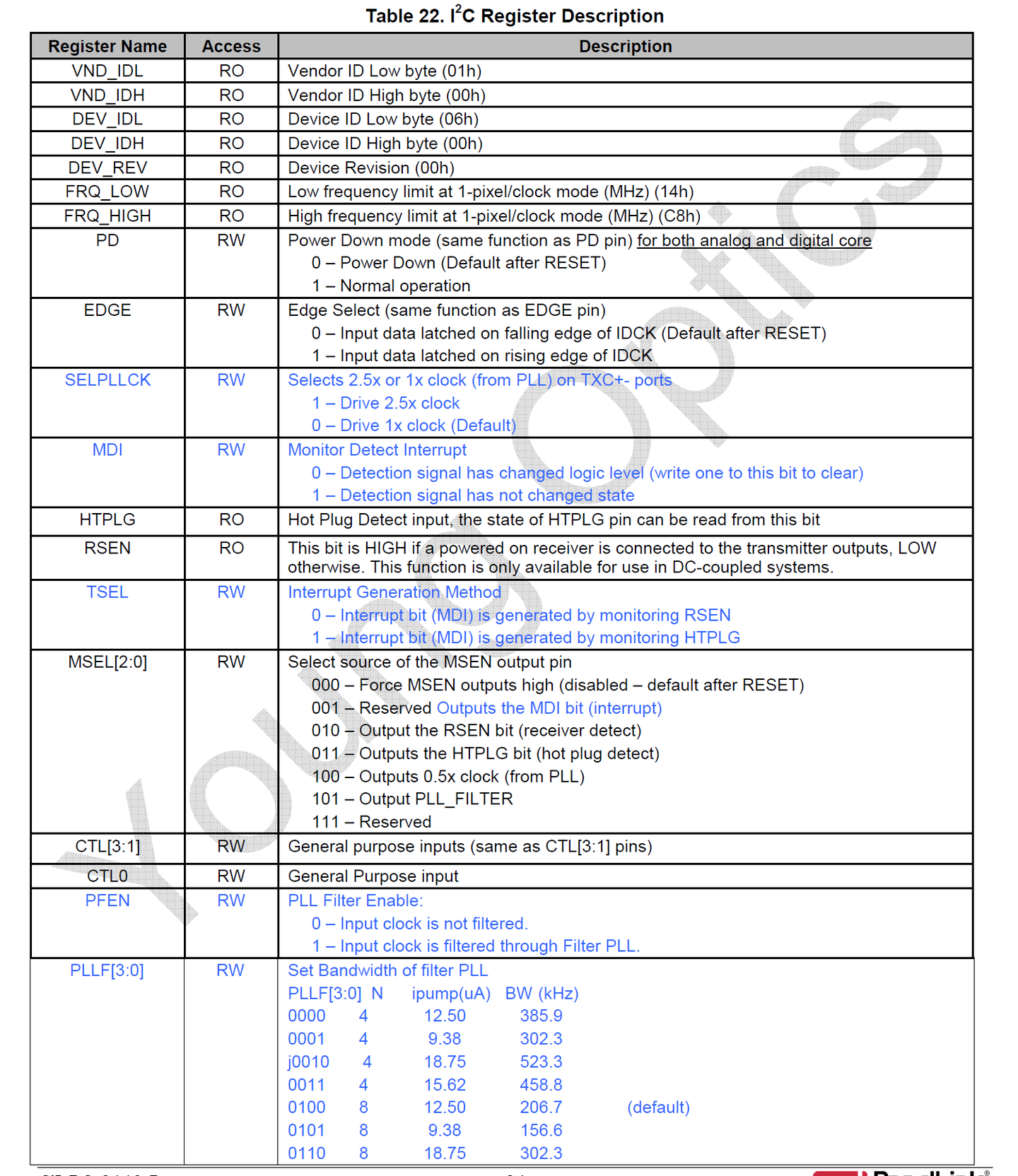

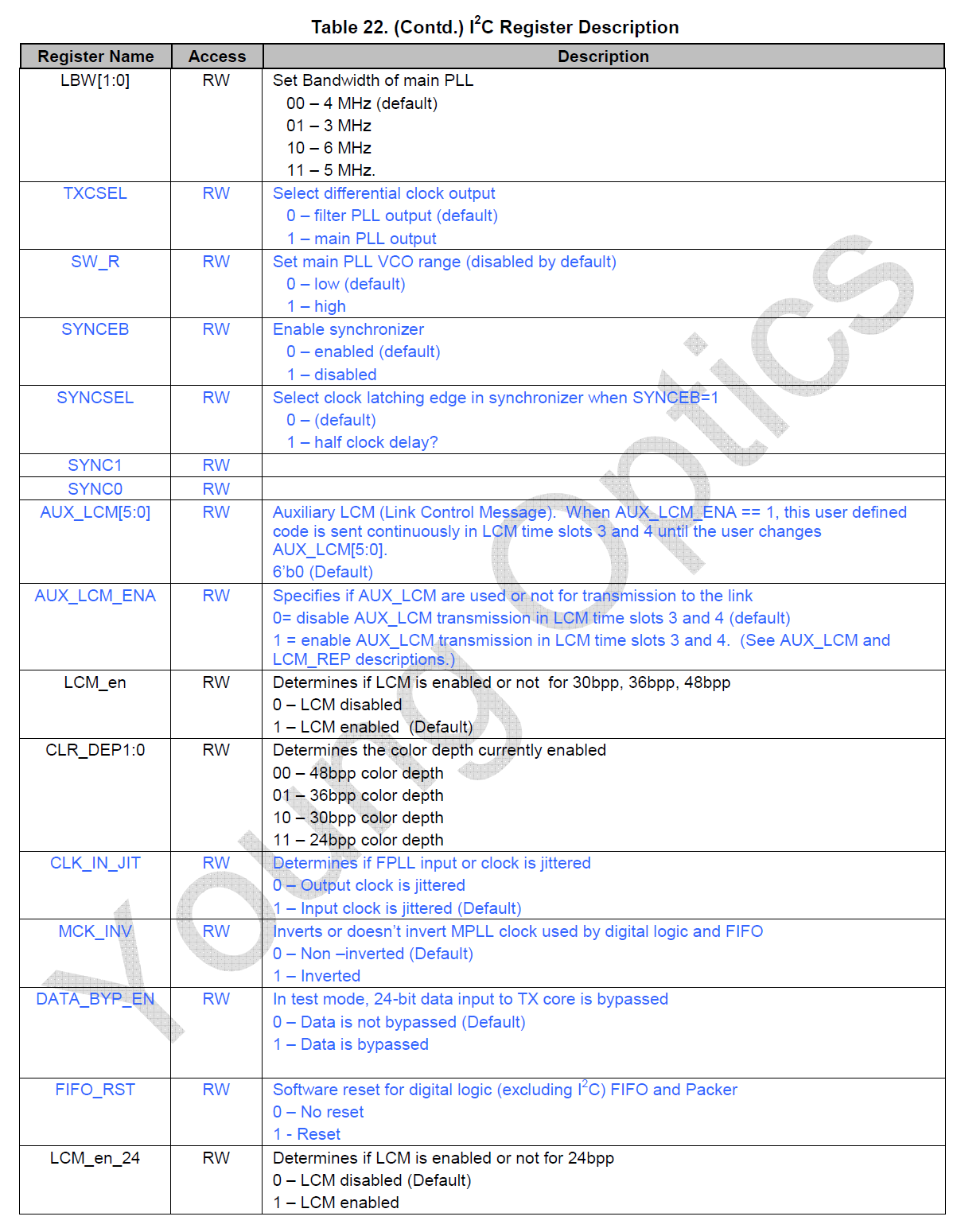

I2C寄存器说明。

- 所有值都是以MSB-LSB排序

- R/W=Read/Write可读/写寄存器,RO=Read Only只读寄存器

- RSVD=Reserved寄存器

- 粗体/斜体的值仅支持Silicon Image官方使用

- 用户应采用官方推荐的值写入可读/写或保留寄存器中

- 除了PD和MSEL之外其他所有的寄存器在复位之后都不会保留前一次的值

- 器件的正常操作需要向0xC寄存器中写入89h

寄存器基址及位分布说明。

添加图片注释,不超过 140 字(可选)

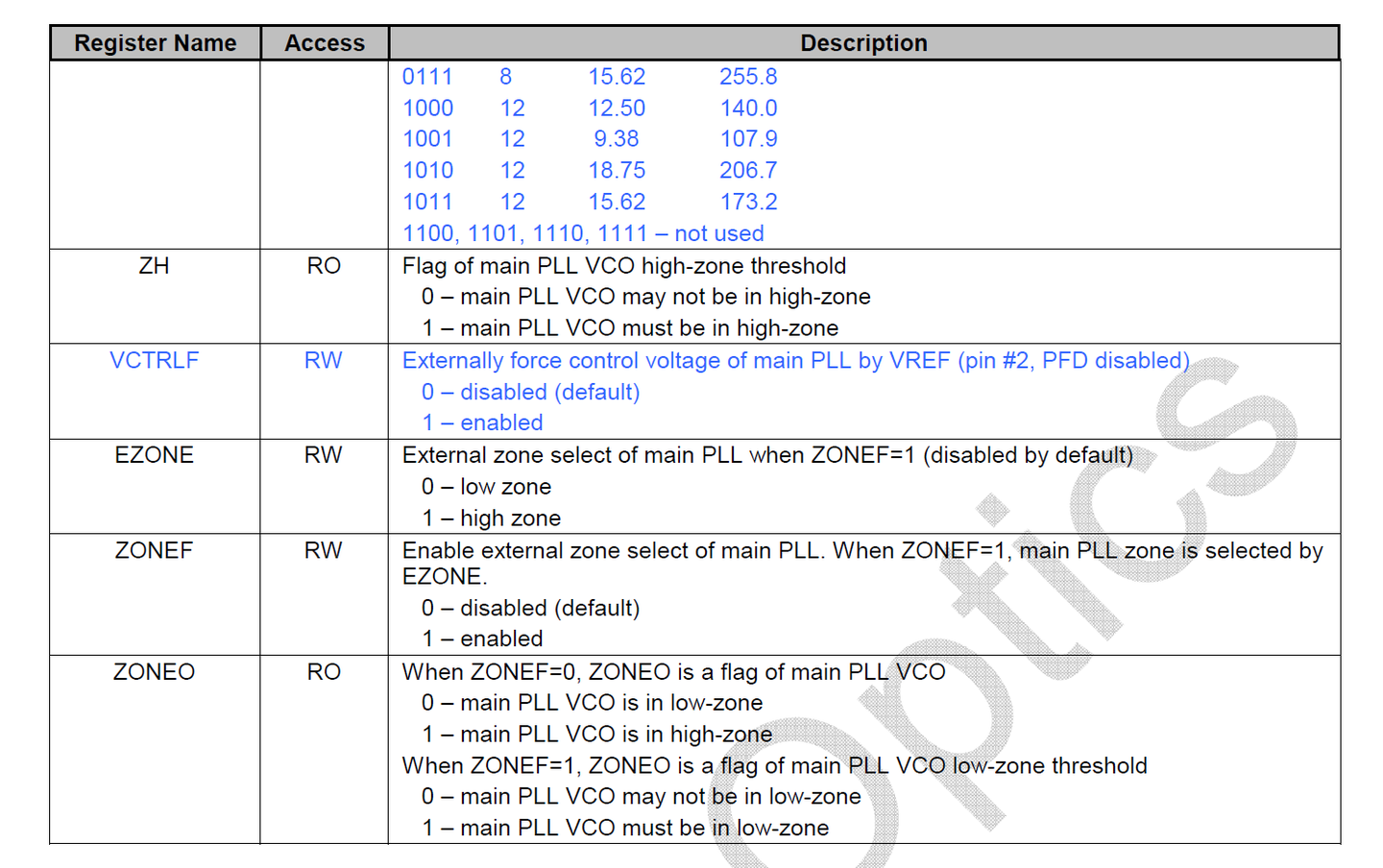

寄存器位域说明,这里就不具体的翻译解释了,大家用到时候再自己研究一下,我大概率不会使用I2C模式对这块HDMI的发送器进行配置了,应该会使用strap-controlled的方式。

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

设计建议

- EXT_SWING管脚上接的电阻推荐使用上述管脚说明中提供的吗,当然该阻值可以根据实际的应用情况做出调整

- PCB地平面建议:建议所有的地管脚都连接到同一片连续的地平面上以减小EMI

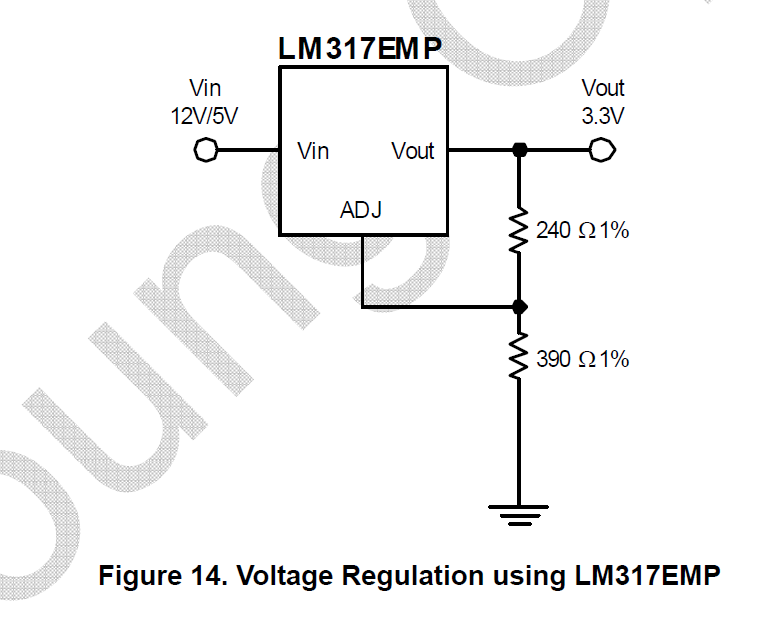

- 电压纹波调节

由于PVCC不需要太大的驱动电流,使用输出电流大于50mA的低压差电压调节器就足够,推荐电压调节器如下图所示。

添加图片注释,不超过 140 字(可选)

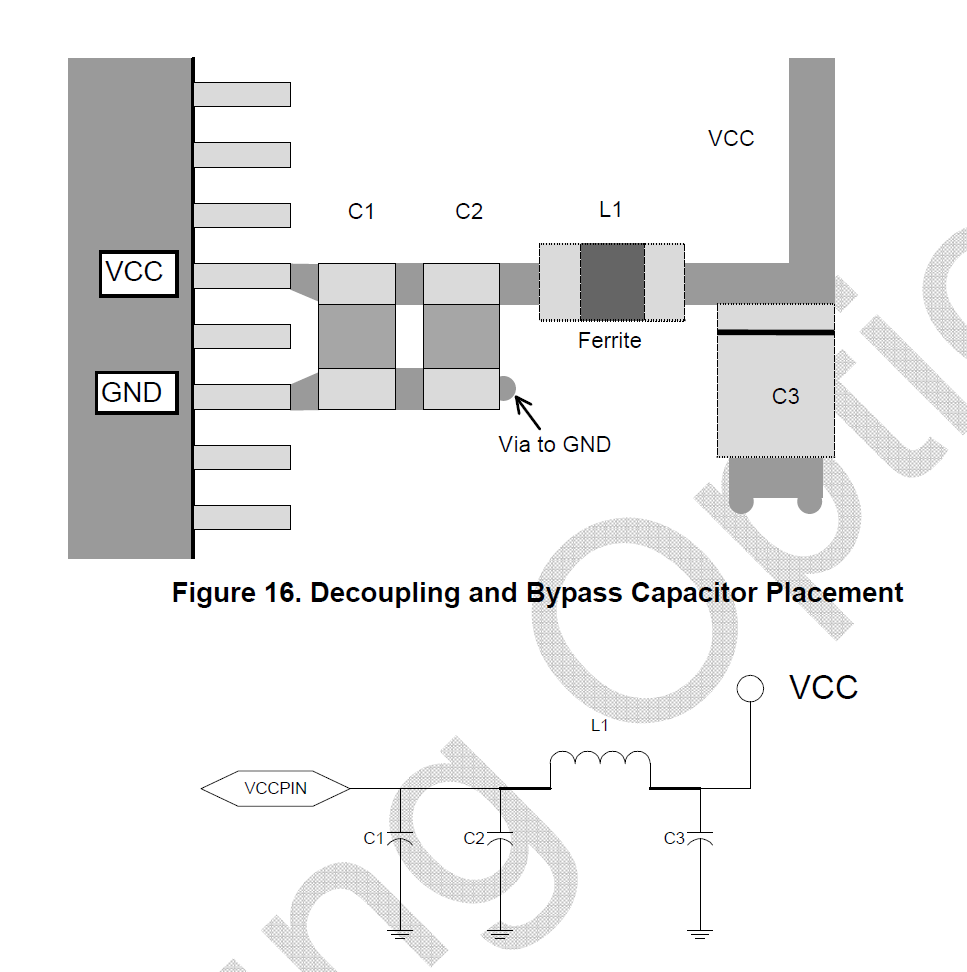

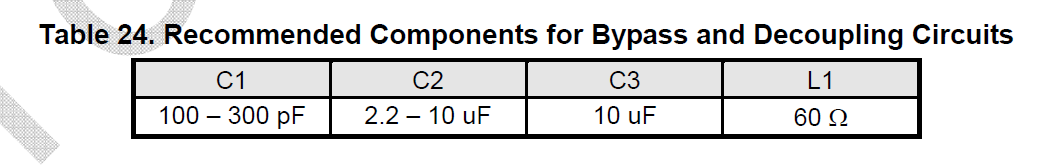

4.去耦电容

每个电源管脚都应该有旁路电容,旁路电容要尽可能的和电源管脚放的近,同时尽量不要经过过孔。

添加图片注释,不超过 140 字(可选)

推荐的旁路和去耦电路器件参数如下所示。

添加图片注释,不超过 140 字(可选)

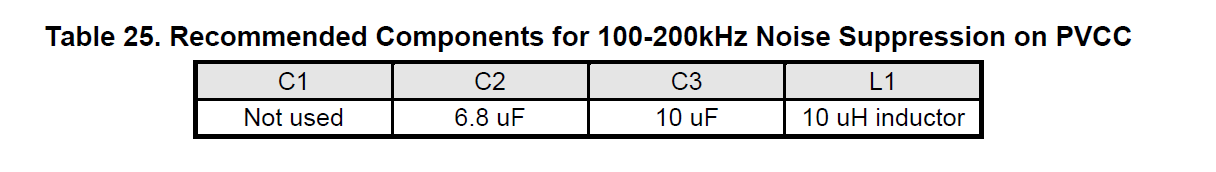

以PVCC供电的PLL电路会对100-200kHz的噪声比较敏感,如果电源易产生超过PVCCN的噪声分量,建议使用以下器件参数进行噪声抑制。

添加图片注释,不超过 140 字(可选)

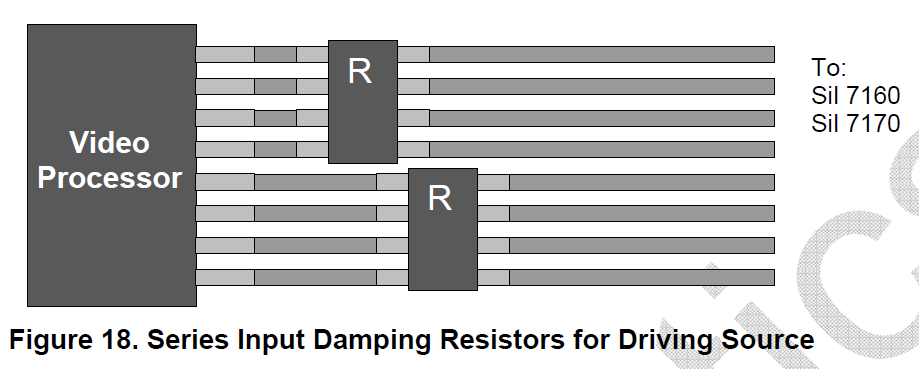

5.串联电阻

串联电阻主要是通过阻抗匹配减小反射,串联电阻应该更靠近视频处理器或图像处理芯片输出引脚端。

添加图片注释,不超过 140 字(可选)

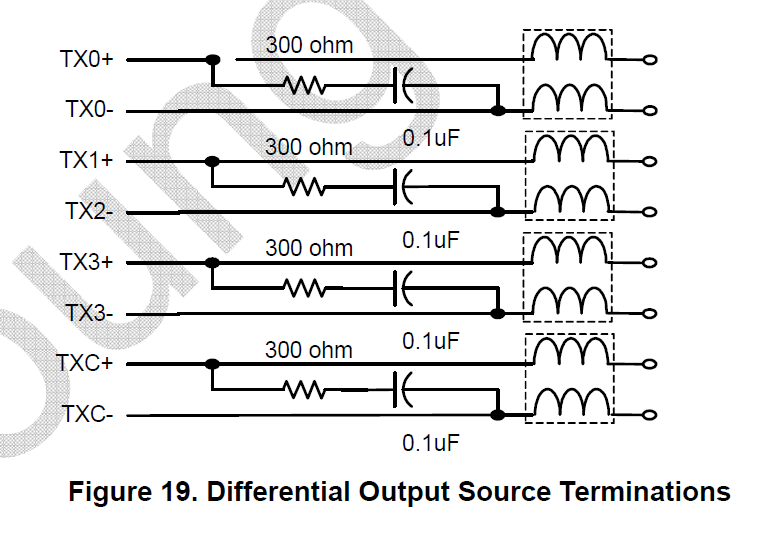

6.差分输出的源端接电阻

由一个300ohm的电阻和一个0.1uF的电容组成,能够提升信号的摆幅;另外,通过串联共模扼流圈也能够进一步提升信号如下图所示。

添加图片注释,不超过 140 字(可选)

如果该发射器需要应用在DVI环境中,产品手册中推荐使用源端接匹配。注意在该条件下,电容需要匹配DVI空闲模式下的直流偏置要求,同时注意信号抑制要求R(EXT_SWING)的值也发生相应的改变。

当使用源端接时,功耗会轻微变高。

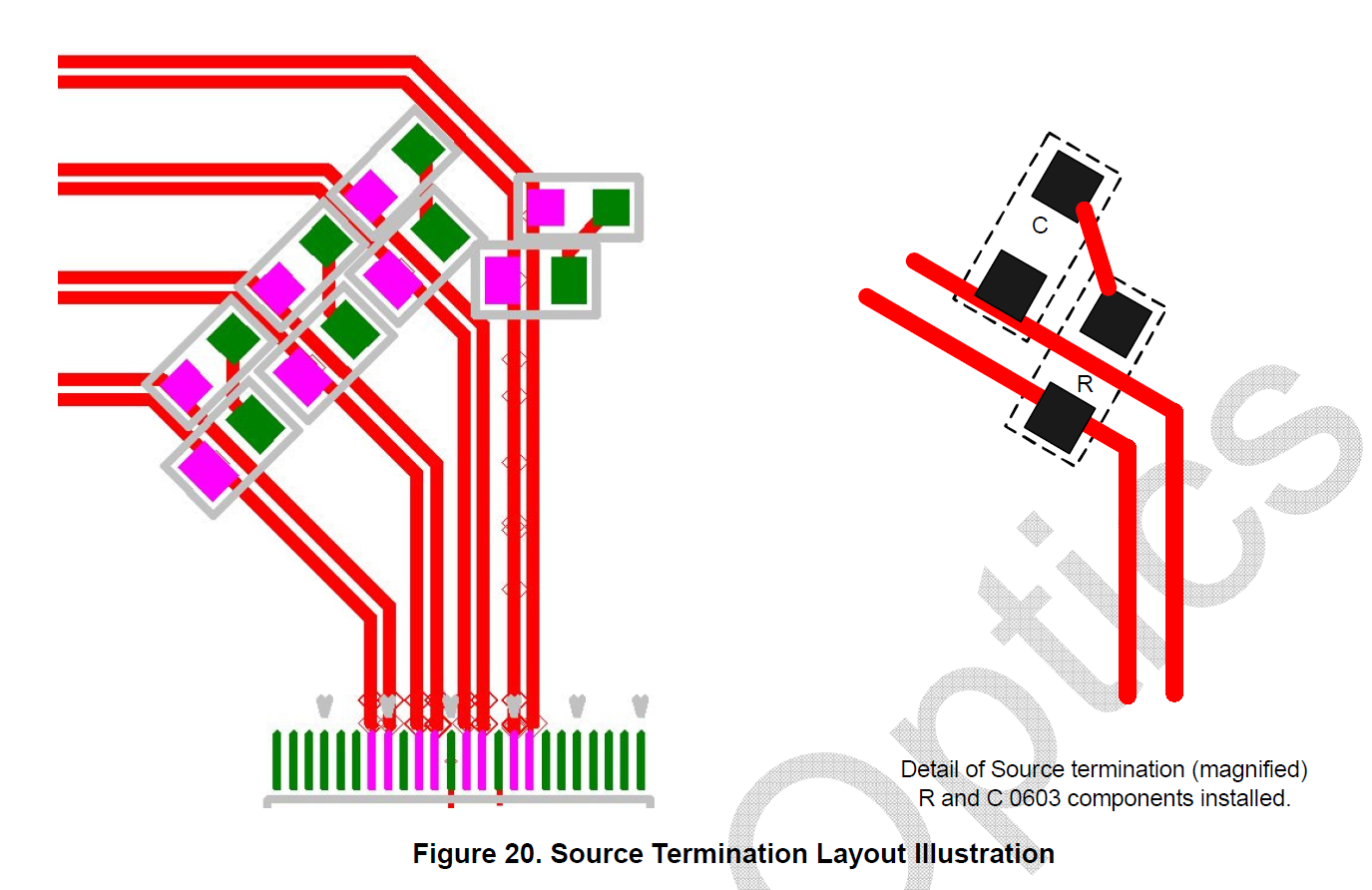

源端接推荐Layout如下图所示。

添加图片注释,不超过 140 字(可选)

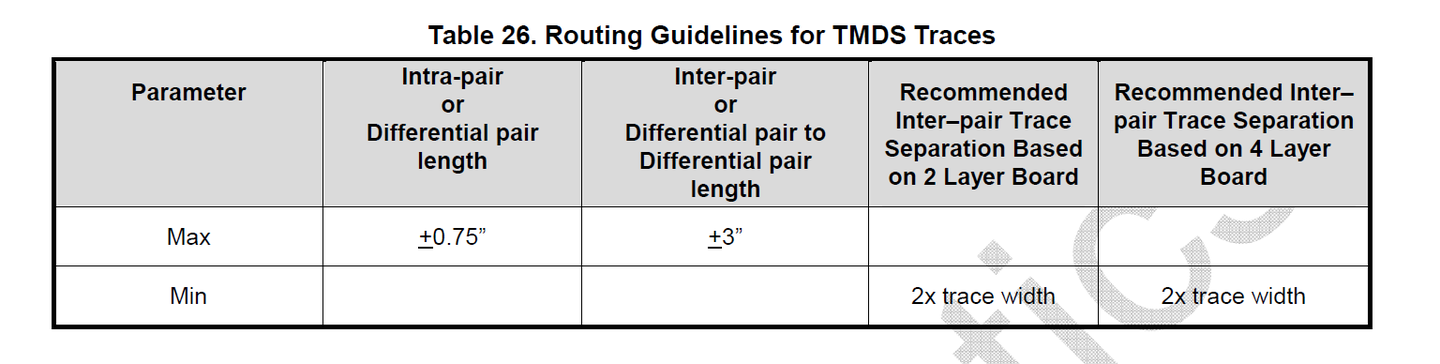

Layout注意事项:

- 发送器尽可能和输出的连接器靠近

- 差分线阻抗要求100ohm,差分走线尽可能的短,四对差分线之间要满足组内等长和组间等长要求

- 差分走线之间要尽可能的对称,同时尽量避免通过过孔或对称使用过孔

推荐的差分走线如下图所示:

正确的差分信号走线

添加图片注释,不超过 140 字(可选)

走线约束建议如下图所示。

添加图片注释,不超过 140 字(可选)

Sil7170封装

在进行硬件电路设计时,参考以下数据进行封装库的设计。

添加图片注释,不超过 140 字(可选)

第一篇文章还只是简单的照搬数据手册,说白了就是简单的翻译,希望之后能够慢慢的进行输出和总结吧,若是有幸这篇文章能够对你有帮助,那真是太好了,不过在这篇文章中我只记录了对我比较有用的部分,若是你有更全面的关于SiI7170这个器件的需求,建议直接查看官方的数据手册。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。