软硬件融合技术内幕 进阶篇 (10) —— 巨头的碰撞 (上)

软硬件融合技术内幕 进阶篇 (10) —— 巨头的碰撞 (上)

在前几期,我们论述了使用网络处理ASIC/NPU,SoC和FPGA实现SmartNIC的困难,附上链接:

基于这些考虑,业界出现了一些对SmartNIC革新的思路。

话分两头。我们在《软硬件融合技术内幕 进阶篇 (6) —— 斯大林与托洛茨基》中的最后一段提到,有一种较为冷门的网络处理芯片叫做NPU。NPU是Network Process Unit的缩写。与交换机ASIC相比,NPU具备较强的可编程能力,如10级以上的可编程处理流水线。此外,NPU还支持硬件加速的QoS和数据包分片重组等功能。一般地,NPU经常用于高端路由器、OTN(Optical Trasmittion Network)、RAN (Radio Access Network)等场景。但是,由于高端网络设备厂商往往倾向于自研NPU,商用市场的NPU产品逐渐凋零,最后一家NPU厂商EZ-Chip也在2016年被Mellanox收购。

恰好,Mellanox是SmartNIC概念的提出者之一。早在2017年,Mellanox推出的ConnectX-4系列网卡,就具备了SmartNIC的基础功能,如集成vSwitch,并实现VXLAN封装和解封装的offload等。

在Mellanox收购了EZ-Chip后,很快,吸收了EZ-Chip NPU产品的一些设计,推出了Bluefield系列的DPU。

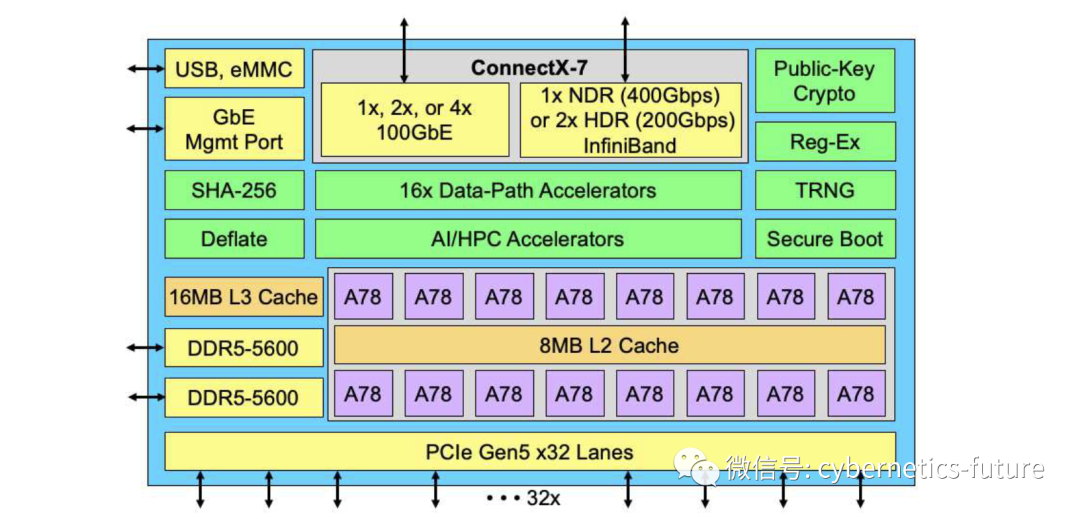

图中是Bluefield-3 DPU的设计框图。

在图中,我们发现了一个熟悉的身影——ConnectX。ConnectX是Mellanox基于可编程ASIC的智能网卡产品系列,内置了原生的100G以太网MAC核,以及一系列网络相关的处理能力。ConnectX 7 可以支持4个100GE口,并且增加了RDMA,NVMe over Fabric等高级网络特性。在Connect-X 7芯片之外,Bluefield-3还有一颗SOC芯片,内部集成了SHA-256,公钥体系(非对称)加解密算法、其他可编程数据平面加速组件。

为了满足更丰富的可编程特性,特别是Hypervisor卸载、VirtIO-blk卸载等,Bluefield-3的内部还集成了16个arm Cortex-A78核心,并可以通过DDR5标准外挂DRAM。为了提供足够的IO带宽,Bluefield-3通过32通道的PCI-E 5.0总线连接服务器主机CPU。

比较有意思的是,Bluefield-3提供了16个Data-path Accelerator。从其datasheet可以看出,这16个Data-path Accerlerator提供了256个线程,也就是一个核可以提供16个线程。

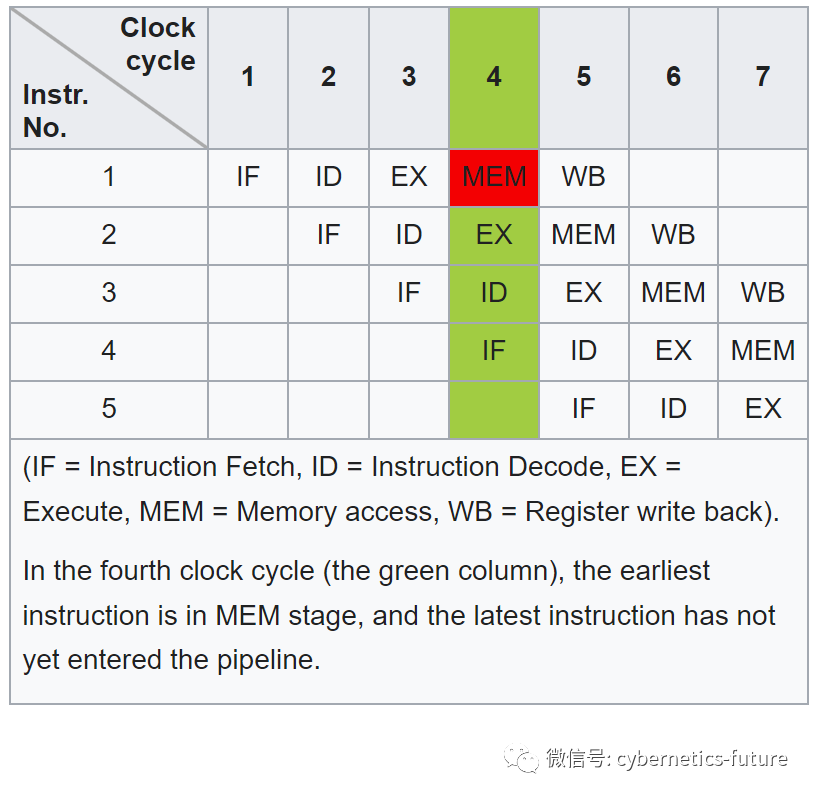

熟悉CPU超线程技术的读者应当了解,CPU的超线程,指的是一个核中有N套寄存器组 (Register File),对操作系统呈现N个CPU,而它们共用一个ALU。由于CPU的流水线特征,流水线执行的多个环节中,往往只有一个环节使用ALU,这样一来,多个超线程可以轮流使用一个ALU,让占据了芯片大部分面积和成本的ALU得以最大化利用。

一般地,在x86 CPU中,超线程数量为2,而一些MIPS处理器可以实现4倍超线程,也就是一个核有4套Register File,对操作系统呈现4个CPU。显然,这可以从一定侧面表明,4倍超线程的MIPS处理器,其大部分处理时间阻塞在IO和内存访问上,并不会使用ALU。

从这里,我们可以看出,这16个16倍超线程的Data-Path Accerlerator,处理网络与IO方面所占的时间更长,对ALU的使用更少。实际上,它们的技术就来自于EZ-Chip的NPU产品。

EZ-Chip在2016年推出C语言可编程的NPS-400后,由于CISCO为代表的一系列主流路由器设备商都没有选用,EZ-Chip经营出现困难,最终被Mellanox收购。NPS-400与前几代NPU芯片最大的区别就是,把多级可编程流水线改为执行包处理指令的类RISC核。

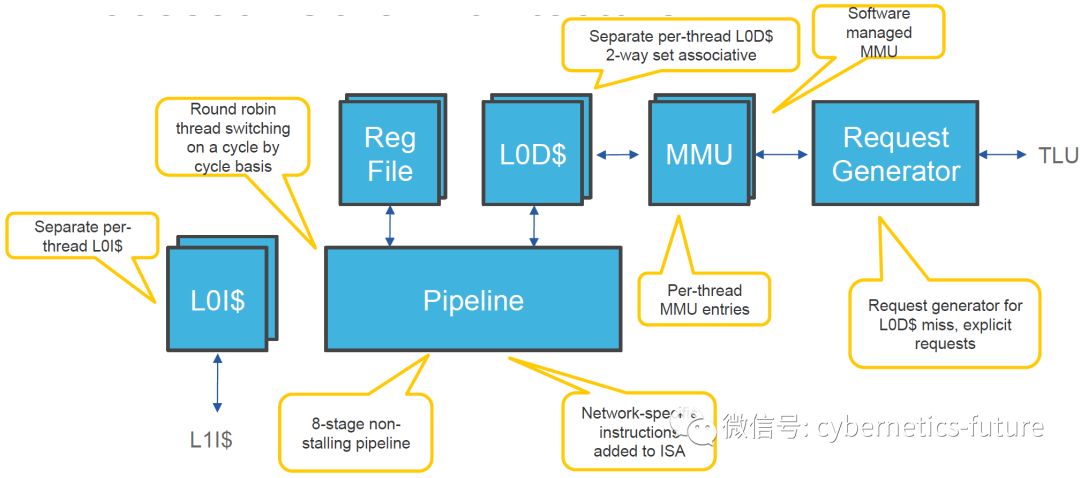

读过《网络设备硬核技术内幕 路由器篇 9 CISCO ASR9900拆解 (二)》的读者会想起来,CISCO自研的NPU LightSpeed,内部的数据包处理核心部件为Process Array,集成了672个并行的包处理器,每个包处理器内部结构如下图:

图中Pipeline可以类比为CPU中的ALU,它可以执行微码指令,对数据包提取特定字段,并进行查表、替换等操作。每个包处理器包括4个pipeline,整个芯片有2688个pipeline。

Mellanox的Bluefield就吸收了NPS-400的这一设计,通过集成16个硬件加速核,提供256个并发的线程。当然,这256个并发线程并非只能处理网络数据包,还可以处理VirtIO-Blk等offload。

原来,Bluefield的方案实际上是一种融合的方案,融合了SOC,NPU和网卡ASIC,互相取长补短。

SOC具备极强的可编程能力,短板在于硬件加速算法较为固化;

ASIC具备极强的硬件加速能力,短板在于无法灵活编程;

而NPU的硬件加速能力和可编程性,介于SOC和ASIC之间;

Bluefield就利用了这种取长补短的方法,实现了真正可商用的SmartNIC。NVidia给它起了一个新的名字——DPU(datapath process unit)。而计算机领域的另一巨头 Intel,也提出了自己的SmartNIC方案,称之为IPU。在SmartNIC领域,两家巨头发生了激烈的碰撞。

下期,我们将为大家详解Intel的IPU。