软硬件融合技术内幕 终极篇 (5) —— 中华文明的瑰宝

软硬件融合技术内幕 终极篇 (5) —— 中华文明的瑰宝

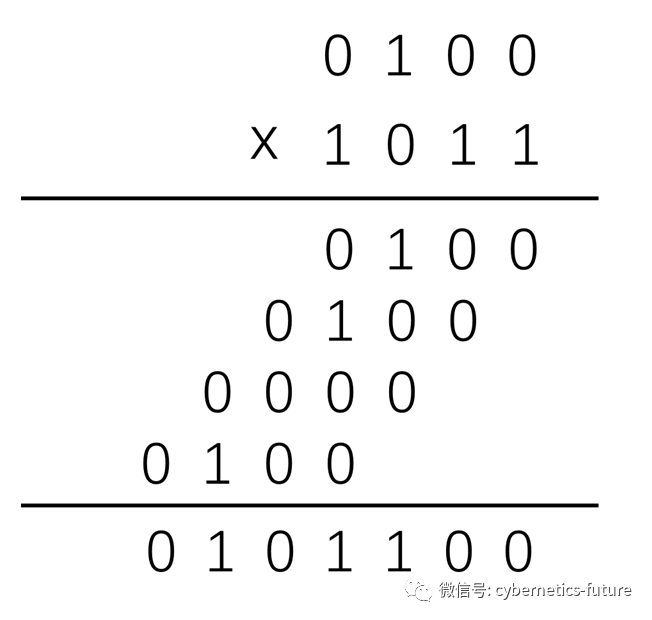

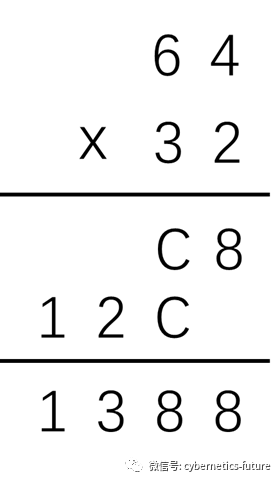

在前几期,我们介绍了计算机对加减法的预算,以及对乘法的运算也开了个头。实际上,在计算机中,对乘法的计算也是采取列竖式的方法:

那么,这样的计算在电路中是如何实现的呢?

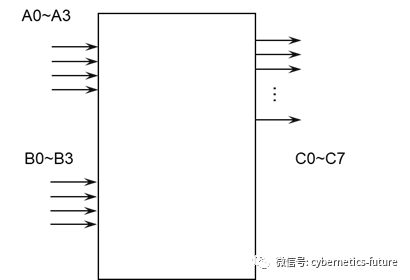

首先,我们可以看出,2个4bit的二进制数相乘,最终会得到1个8bit的二进制数。因此,4bit的乘法器的输入和输出应当像下图这样:

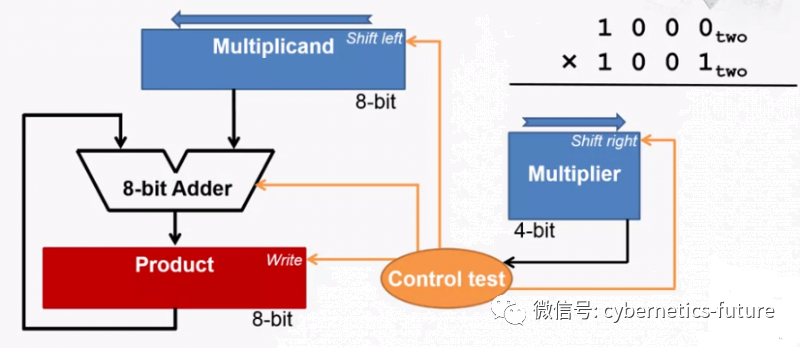

从上图的竖式看出,4bit x 4bit需要进行三次移位运算,以及三次加法运算,因此,乘法器实际上需要一个移位器,以及一个8bit的暂存器:

这里面涉及到一个问题:用什么方法来进行数据的暂存呢?

我们想到,在前面几期,我们介绍的加法器实际上是无状态的,并没有中间状态的存储。而乘法器需要中间状态的存储,也就是需要所谓的“寄存器”。这就进入了数字电路的一个新领域——时序电路。

所谓时序电路,就是在时钟信号驱动下,各部件按一定的次序工作的数字电路。它的最基本构成单元是触发器(Flip-flop)。

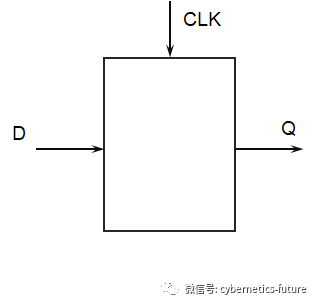

触发器中,最基本的是D-触发器。

如图,D触发器有两个输入和一个输出。输入端CLK为时钟脉冲,而D端为数字输入,Q为输出。在CLK的下降沿,Q会变得与D相同。

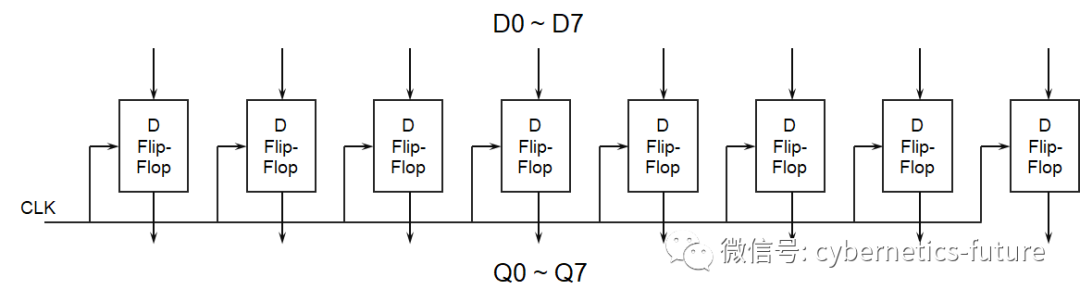

举一个例子:在CLK的下降沿时,D为0,则在下一个CLK的时钟周期内,Q会一直为0。这样一来,我们将8个D触发器并联:

如图,在CLK的下降沿,Q0到Q7会变得和D0~D7的输入完全一致,也就是说,每个D触发器内部锁存了输入状态。8位D触发器就可以构成一个暂存8 bit信息的寄存器。

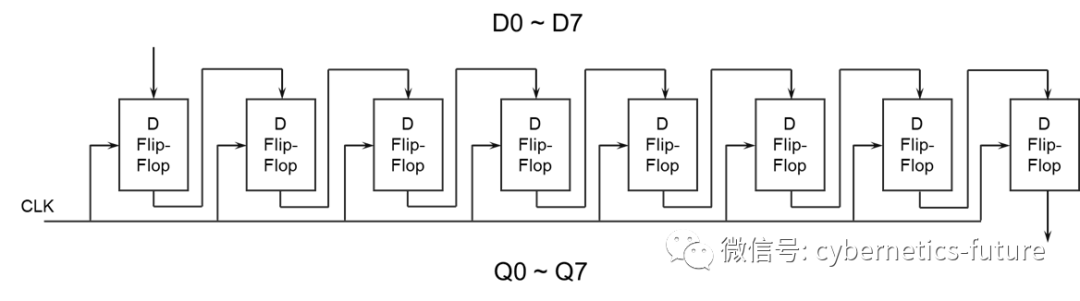

利用D触发器的这个能力,我们还可以实现移位操作:

我们把每一个D触发器的输出连接到下一个D触发器的输入端,这样,每当CLK到来时,就把上一个D触发器的值赋予了下一个D触发器的值。前面提到的乘法器中的移位器就是这样实现的。

这样一来,我们就可以实现一个乘法器了。

当然,这样的乘法器在理论上是很不错的,但在真实的工程实践中,因为每次移位都需要1个时钟周期,32bit的移位就需要32个时钟周期;同时,每次累加也需要1个时钟周期,这会导致32bit的乘法运算需要100+个时钟周期。这是无法接受的。

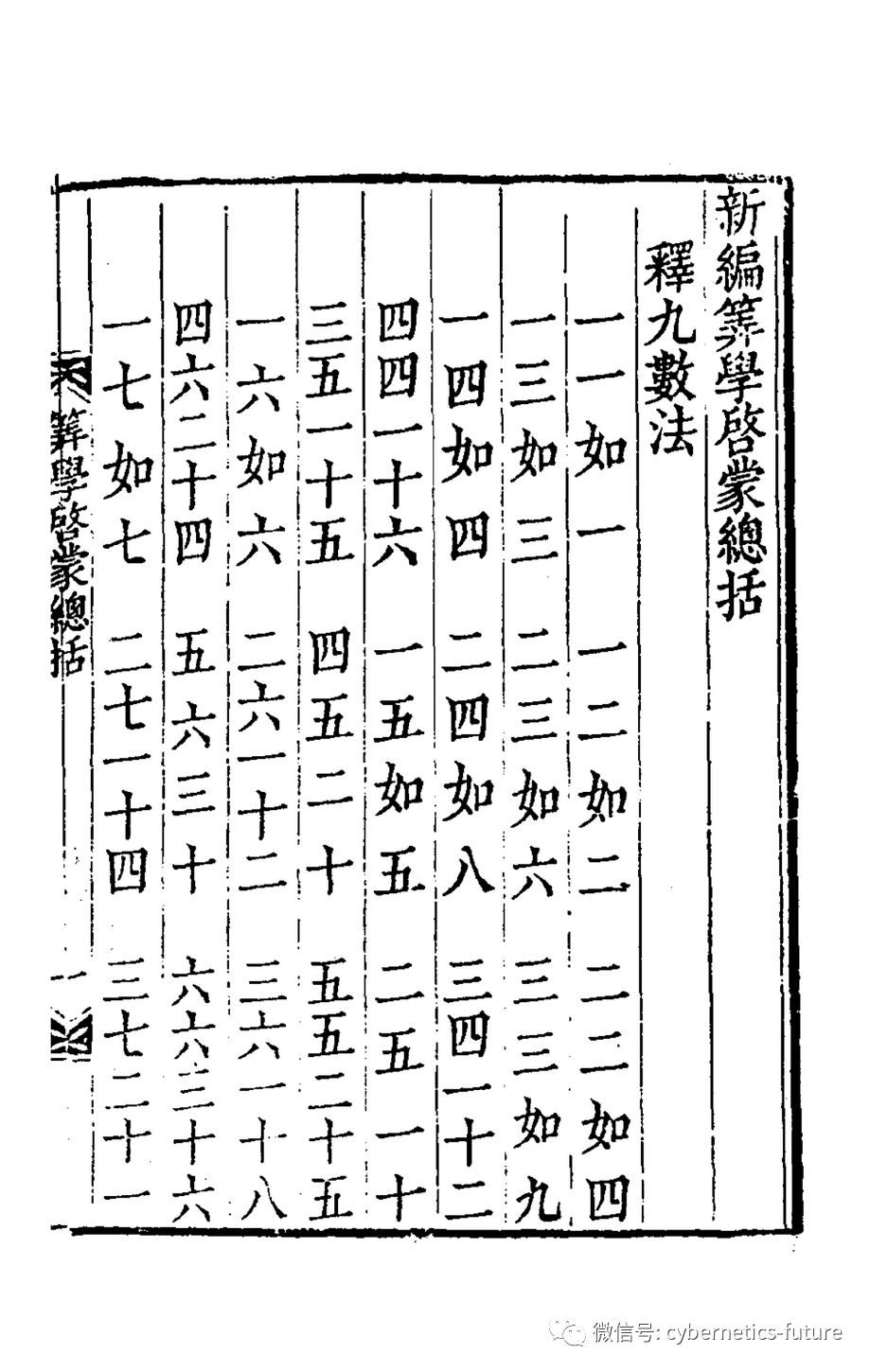

另一个思路是,从中国传统文化中汲取智慧——

每一个中国人,在还是小朋友的时候,都会被要求背诵中华人民智慧的结晶——

把九九乘法表背下来以后,相当于在人脑中植入了硬件固化的乘法加速器,大幅提升了人类进行乘法运算的效率。

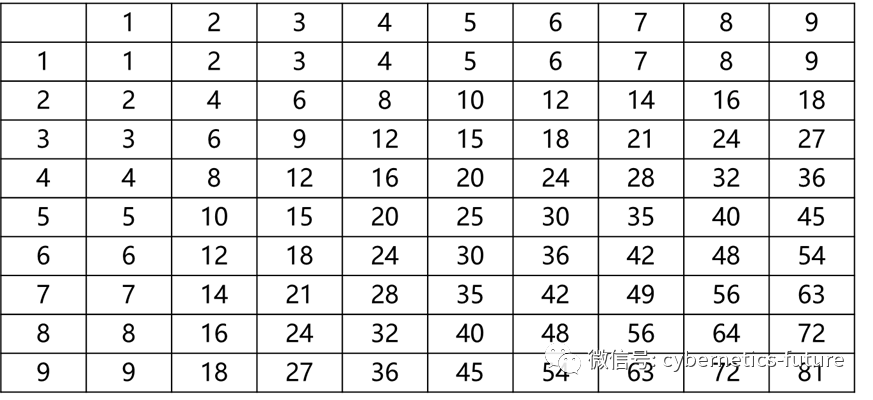

在计算机的视角看来,九九乘法表实际上可以理解为组合逻辑真值表:

我们也可以利用这种方式,将32bit乘法,拆分为8个4bit的乘法进行运算,从而通过牺牲电路面积和功耗的手段,来提升运算的效率。

如图,我们如果将4bit x 4bit的真值表,通过组合逻辑电路固化在乘法器中,就可以把8bit的乘法运算简化为4次4bit x 4bit,然后快速得出结果。

在工程实践中,对乘法器的优化是CPU设计的深水区。如Intel的386计算16bit数的乘法需要约150个指令周期,而486只需要30个指令周期。

在计算机ALU,最为复杂的运算单元是除法器。

计算机计算除法的方式和人类差不多,以16bit除以8bit为例,需要以下步骤:

- 从高位开始试商并计算该轮余数;

- 余数左移一位,与被除数随后一位组合,循环回步骤1,重复8次循环;

因此,计算除法需要1个乘法器(试商),1个加法器(计算余数)以及额外的16位锁存器。

有过程序开发经验的同学可能会想到一个问题:

既然计算机具备了计算各种算术运算和逻辑运算的能力,我们如何让它知道应当执行什么运算呢?

这就涉及到计算机处理器对指令的解析。

请看下期。