place和routing流程

过程概述

place和routing(P&R)过程是电子设计自动化(EDA)流程的关键阶段,它塑造了集成电路(IC)和印刷电路板(PCB)的最终性能和功能。这个错综复杂的过程包括一系列步骤,将高级电路设计转化为准备制造的物理表现形式。关键阶段包括前端设计、逻辑综合、网表生成、时序分析、物理实施以及place和routing的核心活动。每个步骤都遵循严格的准则,以满足电气和物理限制,确保电路符合所有操作规格。

前端电路设计

在从概念到有形产品的旅程中,前端电路设计是蓝图。工程师阐明功能要求,定义架构,并选择适当的组件和互连范式。它们涉及塑造时钟分配、信号完整性和电源管理的基本决策。这个设计阶段通过与高级工艺节点和复杂封装设计风格的复杂设计考虑保持一致,为成功的P&R奠定了基础。

逻辑综合

遵循前端设计,逻辑综合将抽象电路描述转换为网表表示。这个阶段使用复杂的算法来优化电路的面积、时序和功耗,同时遵守定义的设计标准。由此产生的优化后逻辑是理论电路功能和实际实现之间的桥梁,确保初始设计目标与制造保持一致。

网表生成

Netlist生成是一个变革性步骤,将综合成的逻辑转换为电子元件(如晶体管、电阻、电容器)及其精确互连的列表,称为netlist。网表是后续物理设计阶段的基础,是确保时序、功耗和面积目标在物理实现层面上可行的关键来源。

时序分析

时序分析根据其时序要求严格评估电路,确保信号在可接受的时间内传播,从而避免潜在的竞争或setup和hold时间违规。

物理实现

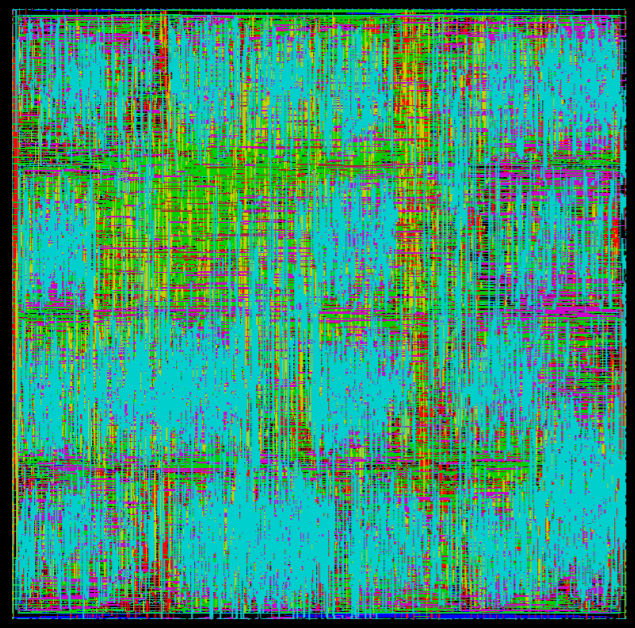

物理实现将网表和时序数据转换为硅片中电路元素的空间配置。它涉及单个组件的合理place和routing,以最大限度地减少延迟和最大限度地提高电路效率。复杂的EDA算法考虑了所需工艺的独特挑战,在遵守严格的散热和供电要求的同时,管理高密度集成。

Layout and Placement

Layout and Placement需要将组件合理地组织到IC或PCB上,平衡最佳空间利用与功能和信号完整性要求。确保电力分配无缝集成,设计工具巧妙地驾驭最小化面积的需求,同时优化性能和可制造性。该过程涉及多次的迭代,过程中的Review确保在整个阶段符合无数的设计标准。

Routing

P&R过程的最后阶段,即routing,建立了组件相互连接的复杂电气轨道网络。routing工具利用高级算法为每个连接找到最佳路径,同时减少串扰并遵守时序和电气要求。

Place and Route上的挑战

设计集成电路(IC)和印刷电路板(PCB)不是一件小事,Place and Route阶段通常会带来关键挑战,这些挑战从由于日益增加的设计复杂性,到必须满足的严格功耗和时序要求。

一个紧迫的挑战是管理大量Route资源,而不会遇到区域拥塞或Route限制等限制,这些限制在高级工艺节点上加剧。设计师必须利用各种技术来完成Route,同时保持信号完整性,避免紧密封装的Route之间的串扰。此外,推动更小的几何形状以及使用新颖的材料和三维(3D)结构增加了实现理想设计的复杂性。随着模拟和数字组件的集成,在数字噪声中保持模拟信号的完整性的任务就出现了,这一挑战可以决定整个place策略。

时钟源分布也构成了一个重大障碍,特别是随着设计变得越来越复杂,时钟必须可靠且不倾斜地到达许多组件。

时序要求

要求IC内的所有信号必须正确同步,以保持电路的完整性和功能。必须评估每个信号路径的延迟,确保数据以正确的顺序在指定的时间范围内到达,避免违反setup和hold时间。随着设计变得更加复杂,特别是在高级工艺节点上,满足时序要求成为相当大的一部分;这就是时序分析工具在P&R流程中不可或缺的地方。

为了符合这些要求,可以添加buffer和其他时序控制机制,这可能会增加设计复杂性,并影响功耗和面积。此外,必须考虑制造工艺和环境条件的变化,因为它们会显著影响时序。

设计收敛挑战

设计收敛代表在综合后完成设计,以满足所有设置的约束,由于设计规模和复杂性的增长,这越来越具有挑战性。在合理的时间范围内实现设计收敛通常需要多次迭代,因为需要解决与时序、面积、功耗和可制造性限制有关的问题。新的独特的设计要求可能会加剧重大的设计收敛挑战,例如需要有效地集成多个不同的IP块。

此外,对低功耗设备日益增长的需求,特别是在移动和物联网领域,挑战也增加了一层。设计师必须经常找到创新的解决方案来降低功耗,同时仍然满足所有其他性能标准,在达到预期结果之前,经常多次重新Review设计。

设计迭代和性能目标

在实现目标和实际设计结果之间是一个动态过程,通常需要多次设计迭代。每次迭代都希望解决与初始性能目标的差异,这些差异可能包括运行速度、功耗和面积等。随着新数据和制约因素的更新,目标也可能在开发过程中变化,这可能会导致进一步的迭代。

例如,预计以特定时钟速率运行的CPU设计可能需要进行一些布局调整,以优化路径延迟并满足目标。同样,模拟设计组件可能需要多次重新place,以确保尽可能干净的信号路径。迭代过程一直持续到达到理想设计;满足标准而不过度延长设计收敛时间或增加设计成本。

供电和管理

有效的供电和管理在place和routing阶段至关重要,因为电子设计的性能和可靠性在很大程度上取决于稳定和高效的电力输送。电源完整性分析确保整个IC或PCB的电压水平保持不变,减少IR drop, electromigration和ground bounce.

不规则的电源供应可能导致高电流密度区域,这可能会损害设备的寿命和功能。设计师必须巧妙地路由power网络,以确保均匀分布,并战略性地结合解耦电容器,以稳定电源电压。管理动态功耗,特别是在CPU和高性能设计中,需要复杂的技术来最大限度地减少开关电流并减少泄漏,随着芯片上晶体管数量的持续增加,这可能特别具有挑战性。

先进工艺节点

半导体工艺的进步将我们带入了先进的工艺节点时代,晶体管比以往任何时候都更密集,能够提高面积效率,同时提高功能。然而,这些好处在place&routing阶段都有自己的一系列挑战。高级工艺节点引入了工艺变化、对制程变化更敏感性以及可能影响设备性能的物理影响等问题。

设计师必须浏览与光刻、应力效应和电迁移等相关的约束。随着新材料、FinFET晶体管和新颖的3D集成技术的引入,管理这些挑战的复杂性越来越大,所有这些都需要高度准确的建模和仿真工具来预测和缓解潜在问题。

时钟域交叉

时钟域交叉(CDC)是需要考虑到的部分,特别是在具有多个时钟源的复杂IC中。必须仔细处理不同时钟域之间的数据传输,以降低亚稳态的风险,这可能会导致数据损坏或系统故障。

设计师结合同步电路,在域之间安全地传递信号,但确定这些电路的最佳place&routing可能具有挑战性。有必要进行充分的buffer和仔细控制serup和hold时间,以避免违反timing。随着IC复杂性的增加,时钟域的数量和交叉频率也增加,问题的可能性成倍增加。因此,时钟网络的合理设计和严格的CDC验证是寻求高效、无错误设计的关键组成部分。

工具和技术

在错综复杂的电子设计世界中,工具和技术在实现成功的P&R方面发挥着关键作用。利用正确的工具可以加快设计过程,提高准确性,并帮助设计师满足严格的timing要求和其他性能指标。现代电子产品从这些EDA工具中受益匪浅,使尖端设备的设计能够突破硅可扩展性和复杂性的极限。

电子设计自动化(EDA)工具

电子设计自动化(EDA)工具是软件平台,使设计师能够在构建半导体芯片和系统之前管理设计、分析和仿真半导体芯片和系统。这些工具是物理实现阶段的支柱,指导从前端电路设计到最终验证步骤的一切。

EDA软件的领先提供商包括Cadence Design Systems、Synopsysys和Mentor Graphics,每家都根据P&R和其他设计挑战的具体需求提供量身定制的强大套件。

自动与手动place方法

为P&R的place部分选择的方法在很大程度上会影响设计结果和效率。自动布局工具利用算法根据预定义的约束和设计规则来确定组件的最佳PR。这种方法可以大大加快设计过程,并且有利于需要快速设计迭代的高密度电路。

相比之下,手动布局方法使设计人员能够完全控制PR过程,通常导致高度优化的设计,充分利用设计师的专业知识,特别是在模拟和自定义IC设计方面。然而,这种对细节的细致关注可能很耗时,可能并不总是转化为更快的设计开发收敛时间。

在实践中,通常采用混合方法,结合了自动化和手动方法的好处。EDA工具可用于快速进行设计,使用手动调整来最终确定设计细节,特别是在涉及自定义或性能关键元素的情况下。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-07-06,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录