Chiplets 中的UCIe 创新

全文概览

本文档由Alphawave Semi公司提供,主要介绍了其在高性能计算和人工智能(AI)应用领域采用的创新技术与解决方案。

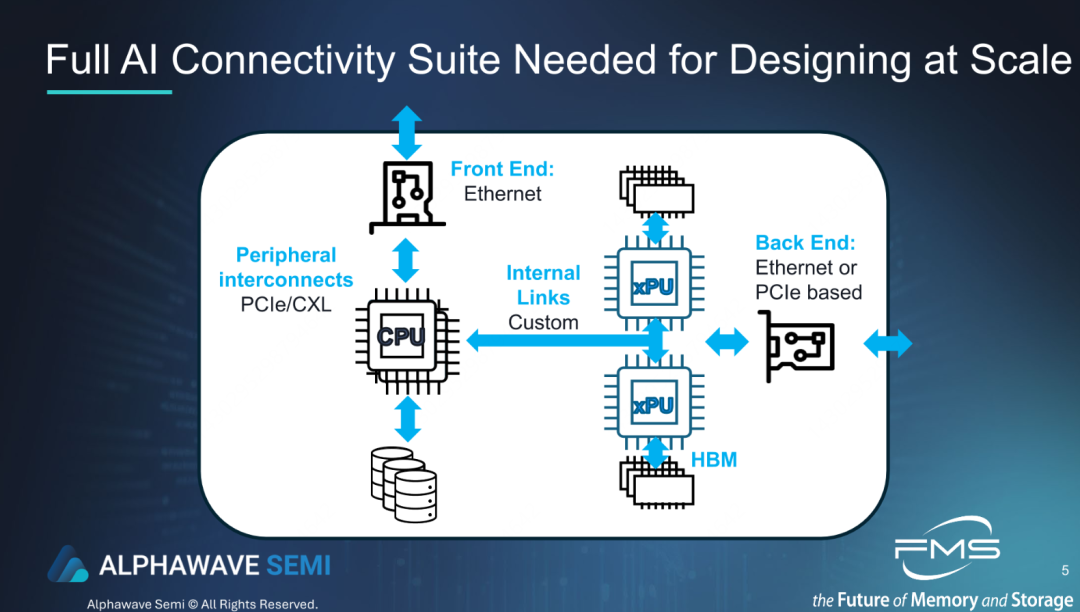

首先,文中强调了基于UCIe接口的芯片组和Chiplets 的重要性,这些技术能够显著提高数据中心的运算效率和连接性,支持大规模AI部署所需的高带宽通信。

其次,详细讨论了Chiplets如何通过减少设计时间和风险、提升可组合性,加速硬件升级的采纳。接着,阐述了为满足大规模设计需求而开发的全AI连接套件,包括前端的以太网和后端的PCIe或CXL以及内部链接和定制化的高速内存解决方案。此外,还介绍了一种革命性的多协议输入输出(I/O)Chiplets——AlphaCHIP1600-IO,它集成了多种高速SerDes技术和安全IP,实现了高达1.6T的吞吐量。

最后,通过对比分析了Chiplets与传统SoC的优势,突出了前者在缩小网络和计算规模障碍、降低功耗和NRE成本、提升生产效率方面的潜力。总体而言,该文档展示了Alphawave Semi公司如何通过其技术创新推动高性能计算的发展,并解决数据中心面临的挑战。

AI 应用给数据中心带来的挑战

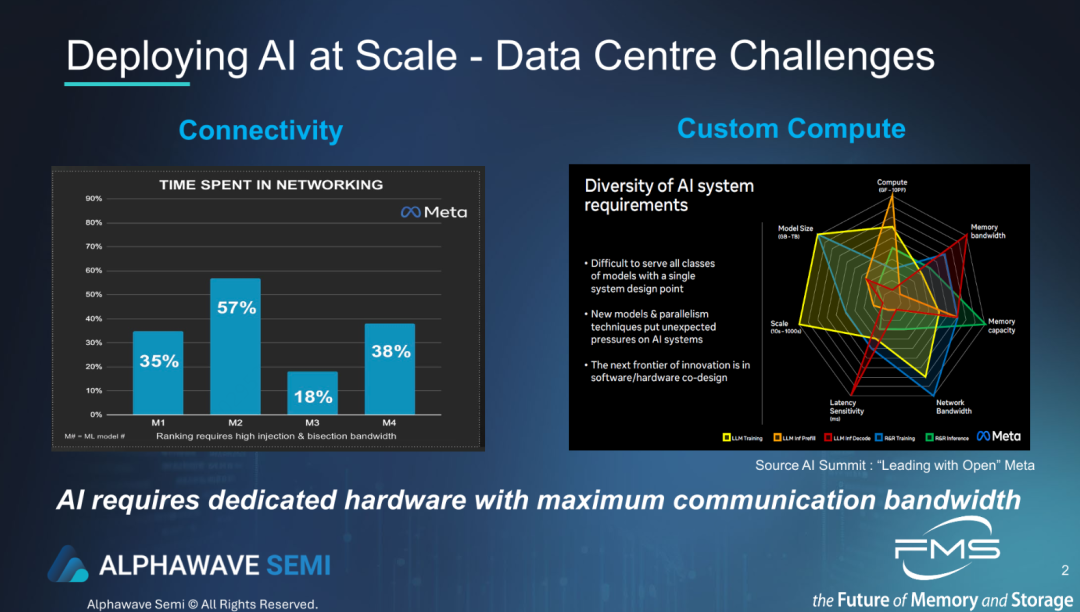

大规模部署 AI 时数据中心面临的主要挑战,包括连接性和计算需求的多样性。

- 连接性问题:

- 大量时间耗费在网络操作中,尤其是排序任务需要高注入和高带宽的支持。

- 定制计算的挑战:

- 由于模型规模、计算需求、内存、网络带宽和延迟敏感性的多样性,用单一设计满足所有模型需求变得困难。

- 创新需要软件和硬件的协同优化。

- 核心需求:

- AI 的发展需要专用硬件来提供最大通信带宽,以满足复杂系统的要求。

Note

定制计算是AI现阶段发展的最大不确定性,需要决策者有更长远的视角,否则短期的All in,将造成巨大资源浪费。从Nvidia硬件设计来看,训练和推理硬件原型已经定义的差不多,不同行业场景模型的落地过程,软硬件协同优化是更复杂的问题。云厂商是怎么看通用推理场景的呢?AWS的 Bedrock是怎么设计的?

Chiplets 片上硬件解耦与互联

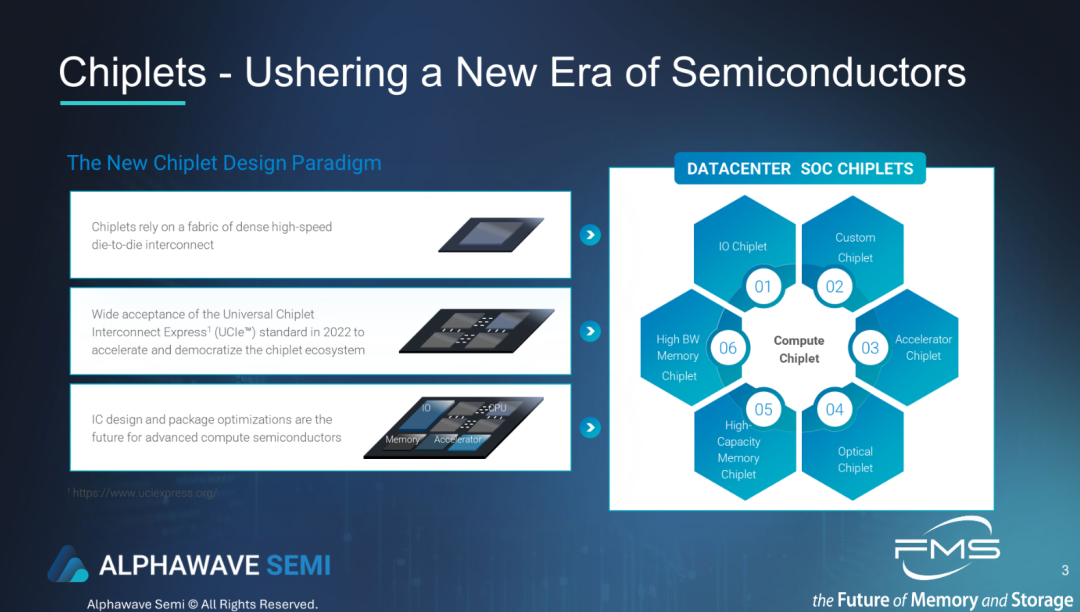

图片介绍了Chiplets技术及其对半导体行业的革命性影响:

- 设计范式:

- Chiplets通过高密度、高速的芯片间互联实现模块化设计。

- UCIe 标准的普及使Chiplets生态系统得以加速发展并更加民主化。

- 优化集成电路设计和封装是先进计算半导体技术的发展方向。

- 数据中心应用:

- Chiplets模块被划分为不同功能单元,包括 IO、加速器、光学、高带宽和高容量内存,围绕计算Chiplets构建。

- 意义:

- Chiplets的模块化设计能够提升半导体的灵活性、性能和生产效率,满足不断增长的数据中心和计算需求。

Note

Chiplets 是封装领域的创新,整体朝着解耦+堆叠方向演进,UCIe 是片上系统的互联协议。 上周一个朋友留言让关注下UCIe,找了下FMS材料,UCIe模块是放在非核心区,这样来看也属合理。SoC上存储可能也就HBM与UCIe 紧相关。

---

为什么需要 UCIe 标准?

UCIe(Universal Chiplet Interconnect Express)标准是为了解决芯粒(chiplets)生态系统中存在的一些核心问题而提出的。随着半导体工艺逐渐逼近物理极限,芯粒技术(将大型芯片分解为多个模块化的小型芯粒)被认为是未来半导体设计和制造的重要方向。但在这一过程中,缺乏统一的互联标准成为阻碍芯粒技术发展的瓶颈。

UCIe 的意义和未来影响

- 加速芯粒技术的普及

- UCIe 标准的普及将推动芯粒技术从高端应用走向主流市场。

- 降低芯片设计门槛

- 统一的标准使中小厂商能够参与生态建设,带来更多创新。

- 提高半导体行业灵活性和效率

- 厂商可以通过标准化的互联协议快速推出产品,降低研发成本。

- 推动半导体行业新一轮增长

- 芯粒技术和 UCIe 标准的结合将引领下一代半导体技术的发展。

在UCIe之前,厂商在芯粒间的互联通信是怎么实现的?

在 UCIe(Universal Chiplet Interconnect Express)标准提出之前,厂商在芯粒(chiplet)间的互联通信主要依赖定制化的互联方案和技术。由于缺乏统一的行业标准,不同厂商使用的技术通常是专有的,例如:

- Intel 使用 EMIB(嵌入式多芯片互联桥,Embedded Multi-die Interconnect Bridge)技术在芯粒之间进行互联。

- AMD 使用 Infinity Fabric 技术互联其芯粒。

- NVIDIA 使用 NVLink 在 GPU 和其他芯片间实现高速通信。

为什么这些方案不够?

- 定制方案的问题:

- 无法支持跨厂商芯粒的协作。

- 开发周期长,成本高,生态受限。

- 现有开放协议的问题:

- PCIe 和 CCIX 带宽和延迟不足,功耗较高,难以满足芯粒间的高性能需求。

- 缺乏针对芯粒设计的封装和通信优化。

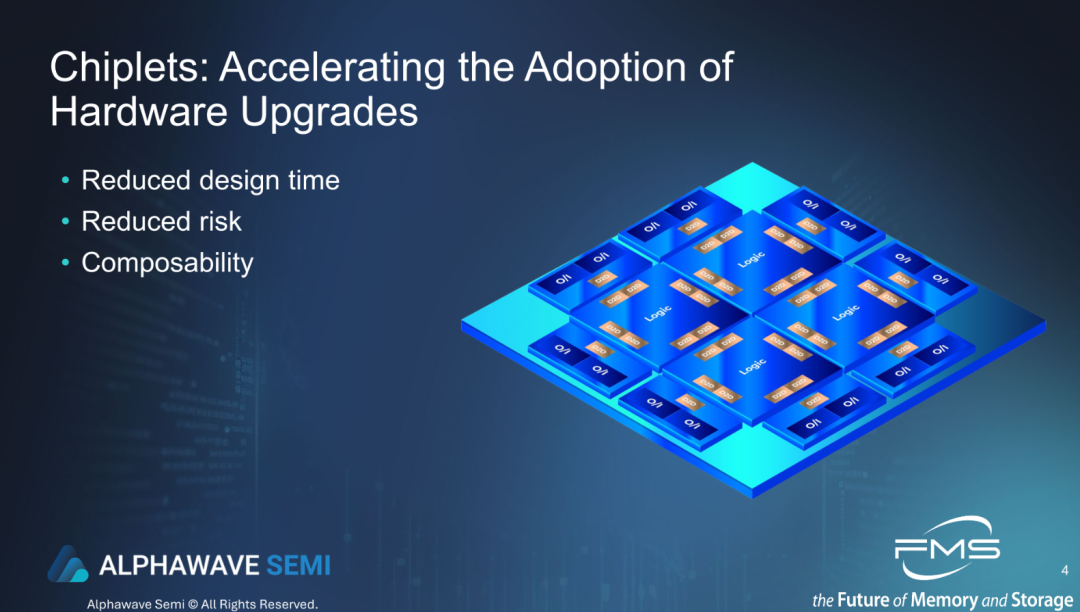

解耦后的Chiplets 加速硬件更新

芯粒技术为硬件设计和升级提供了一种快速、高效、灵活的解决方案,尤其适合需要频繁迭代和升级的场景(如数据中心、高性能计算和消费电子领域)。

图示 UCIe 的作用范围,片上系统不同芯粒间的通信互联。

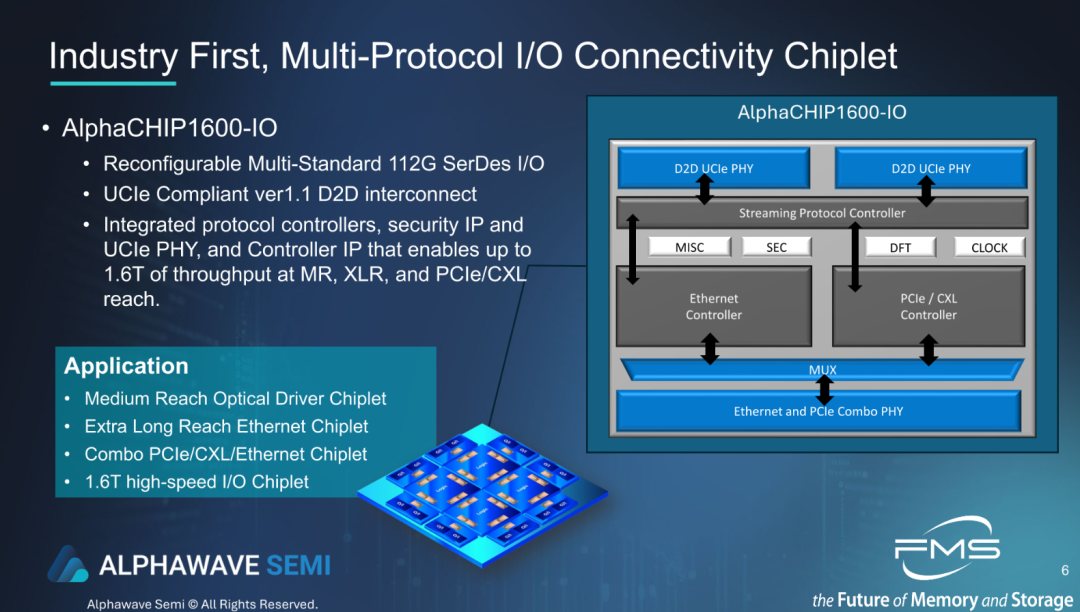

图片介绍了 AlphaCHIP1600-IO,这是一款支持多协议的 I/O 互联芯粒,专为高性能计算和数据中心设计,其特点包括:

- 多协议支持:

- 同时支持以太网、PCIe 和 CXL 等多种协议,提升了芯粒的灵活性和兼容性。

- 高吞吐量:

- 支持高达 1.6T 的数据吞吐量,满足高性能场景的需求。

- 应用范围广:

- 适用于中程光学通信、超长距离以太网、PCIe/CXL 组合芯粒,以及高速 I/O 芯粒。

- 模块化架构:

- 采用 UCIe 标准,集成了协议控制器、安全模块和物理层接口,实现高效互联。

---

要理解 AlphaCHIP1600-IO 这类支持多协议 I/O 互联芯粒(Multi-Protocol I/O Connectivity Chiplet)的意义,即使在已有 UCIe 标准 的情况下,我们需要从以下几个关键点来分析:

已经有了UCIe,如何理解多协议IO互联芯粒?

1. 什么是多协议 I/O 互联芯粒?

多协议 I/O 互联芯粒(如 AlphaCHIP1600-IO)是一种高度灵活的模块化芯粒,它在一个单元内支持多种通信协议(如 PCIe、CXL、以太网等)。这种芯粒的功能超越了传统单协议芯片,使得同一硬件能够在不同的应用场景中灵活适配。

- I/O(输入/输出)互联: 指芯粒通过物理或逻辑接口与其他芯粒、设备或系统交换数据。

- 多协议支持: 单一芯粒同时兼容多种通信协议,避免了为每种协议单独设计硬件的需求。

2. 为什么需要多协议 I/O 互联芯粒?

尽管 UCIe 作为通用芯粒互联标准已经提供了高效的芯粒间通信,但在实际应用中,多协议 I/O 互联芯粒仍然具有以下独特的价值:

2.1 应用场景多样化

- 数据中心需求: 数据中心中不同组件(如存储、加速器、网络设备)之间通常使用多种协议进行通信。比如:

- PCIe/CXL: 用于连接 CPU、内存和加速器。

- 以太网: 用于长距离或分布式系统中的网络通信。

- 光学通信: 用于超高带宽、远程互联需求。 多协议 I/O 互联芯粒能够在同一个硬件中支持所有这些协议,适配多样化的场景。

- 未来扩展性: 不同协议有不同的应用优点,随着硬件升级或场景变化,采用多协议芯粒可以减少硬件替换的复杂性,保护投资。

2.2 UCIe 的局限性

虽然 UCIe 解决了芯粒之间的芯粒间通信(die-to-die)问题,但 UCIe 更侧重芯粒生态中的内部连接(例如计算芯粒与内存芯粒之间)。对于芯片到外部设备(如存储设备或网络)的通信,仍需支持其他标准协议,例如 PCIe、CXL 和以太网。多协议 I/O 芯粒正是为此补充。

2.3 提升模块化灵活性

多协议 I/O 芯粒为芯片设计者提供了一种“即插即用”的灵活解决方案:

- 不同芯片之间可以共享相同的 I/O 互联芯粒,无需为每个应用场景定制。

- 提高生产效率,降低开发周期。

3. AlphaCHIP1600-IO 的多协议支持有哪些实际价值?

3.1 跨协议的无缝支持

- AlphaCHIP1600-IO 提供了 PCIe/CXL/以太网 的组合支持,涵盖了从高性能计算到网络互联的全栈需求。

- 通过内置的多协议控制器(Ethernet Controller、PCIe/CXL Controller),能够动态选择所需的通信协议并高效切换。

3.2 高性能吞吐量

- 芯粒支持 高达 1.6T 的吞吐量,能够满足超高带宽应用的需求,例如:

- 数据中心中高性能计算(HPC)节点的互联。

- 超大规模 AI 模型训练中的加速器数据交换。

- 高速存储阵列的网络连接。

3.3 应用场景的多样化

- 它可以应用于 中程光学通信、超长距离以太网通信 和 PCIe/CXL 组合场景,甚至是需要高速 I/O 的数据处理任务。这种通用性使得芯片在多种场景下都能发挥作用。

4. 与 UCIe 的关系

UCIe 和多协议 I/O 互联芯粒并不是互相取代的,而是互补的关系:

UCIe 的角色:

- 专注于芯粒间通信(Die-to-Die Communication),提供高性能、低延迟的内部通信标准,帮助不同芯粒之间的模块化协作。

多协议 I/O 芯粒的角色:

- 专注于芯粒到外部设备或网络的通信(Chiplet-to-System Communication),为整个系统提供兼容多协议的 I/O 解决方案。

通过结合 UCIe 和多协议 I/O 芯粒,设计者可以构建既支持内部模块化协作,又能适配外部通信的完整芯粒生态系统。

小结

多协议 I/O 互联芯粒(如 AlphaCHIP1600-IO)在芯片设计中扮演着承上启下的关键角色:

- 承上: 在 UCIe 标准下,与芯粒间通信生态无缝结合。

- 启下: 提供灵活的外部通信支持,适配多协议应用场景。

相比传统的单一协议解决方案,多协议 I/O 芯粒能够提升设计的灵活性、扩展性和兼容性,是构建下一代模块化、高性能计算系统的基础。即使在 UCIe 统一的芯粒生态下,它依然不可或缺,特别是在需要多种外部通信协议的复杂场景中。

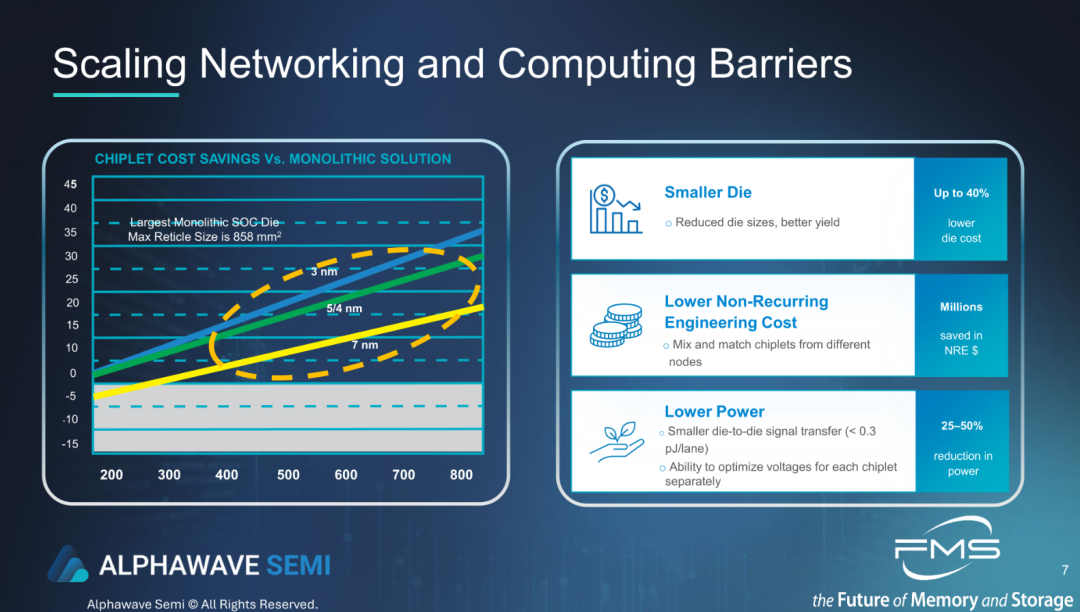

芯粒解决方案与单片解决方案的成本节约对比

图表说明:

- 横轴:芯片面积(平方毫米),最大光罩尺寸为 858 mm²。

- 纵轴:相对于单片 SoC(单片系统级芯片)的成本变化(百分比)。

- 曲线代表不同制程节点的芯片:

- 3 nm(绿色曲线):最高节约接近 40%。

- 5/4 nm(蓝色曲线):节约显著。

- 7 nm(黄色曲线):节约相对较少,但仍优于单片解决方案。

图表总结: 随着芯片面积的增加,芯粒设计在成本上的节约效益显著提升,特别是在更先进的制程节点上。

芯粒设计的核心优势

- Smaller Die(更小的芯片面积)

- 更小的芯片面积带来更高的制造良率。

- 最多可减少 40% 的芯片成本。

- 优势:

- Lower Non-Recurring Engineering Cost(更低的非经常性工程成本)

- 可以混合和匹配来自不同工艺节点的芯粒。

- 在 NRE(非经常性工程)成本上节省数百万美元。

- 优势:

- Lower Power(更低功耗)

- 更小的芯粒间信号传输功耗(每通道小于 0.3 皮焦耳)。

- 可以为每个芯粒独立优化电压,减少 25% 至 50% 的功耗。

- 优势:

芯粒技术通过成本节约、功耗降低和设计灵活性的提升,不仅为当前复杂的芯片设计带来了新方案,还为先进制程技术的广泛应用铺平了道路。它为突破网络和计算扩展的限制提供了强有力的支持,是未来芯片设计的重要方向。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-12-22,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录