Cerebras:存储系统系统与新兴存储机遇

Cerebras:存储系统系统与新兴存储机遇

数据存储前沿技术

发布于 2026-03-09 16:13:20

发布于 2026-03-09 16:13:20

全文概览

在AI大模型参数从亿级向万亿级跃迁的今天,一个根本性矛盾日益凸显:算力可以堆叠,但存储带宽却始终是那个拖后腿的"木桶短板"。传统冯·诺依曼架构下,数据在计算单元与存储单元之间的来回搬运,不仅产生了惊人的延迟,更消耗了系统超过70%的能量。这就是困扰行业多年的"存储墙"危机。

面对这一物理极限,NVIDIA选择用HBM内存尽可能靠近GPU核心,而Cerebras Systems则走了一条更为激进的路——把整个晶圆做成一颗芯片。WSE-3这颗人类制造的最大芯片,集成了90万个计算核心和44GB分布式SRAM,实现了21 PB/s的惊人聚合带宽。更关键的是,它通过"权重流"架构将模型参数存储外置,彻底打破了"容量与速度不可兼得"的行业共识。

那么,这种晶圆级集成方案真的是AI计算的未来方向吗?它又为MRAM、ReRAM等新兴存储器带来了怎样的产业机遇?

阅读收获

- 深入理解分布式片上SRAM架构的设计哲学,掌握单周期访问延迟与海量聚合带宽的实现原理,对比HBM与DDR的架构差异与性能边界

- 领悟"权重流"技术如何通过存算解耦突破传统模型并行的通信瓶颈,实现近乎线性的横向扩展能力,为大模型训练架构选型提供新思路

- 识别新兴非易失性存储技术在AI基础设施中的真实切入点,区分核心计算层与辅助存储层的差异化需求,避免对技术机遇的过度乐观判断

- 获取存储行业投资与技术布局的战略视角,理解架构范式转移背后的商业逻辑与产业影响

👉 划线高亮 观点批注

1. 引言:AI计算中的“存储墙”危机与架构范式转移

在人工智能(AI),特别是大语言模型(LLM)和生成式AI飞速发展的当下,半导体行业正面临着物理与架构的双重极限。随着模型参数量从数十亿这一量级向数万亿(Trillions)迈进,传统的冯·诺依曼架构(Von Neumann Architecture)暴露出了其最致命的弱点:存算分离。在这种经典架构中,计算单元(CPU或GPU核心)与存储单元(DRAM或HBM)在物理上是分离的,数据必须通过有限的带宽通道在两者之间频繁穿梭。这种数据移动不仅产生了巨大的延迟(Latency),更消耗了系统绝大部分的能量。根据斯坦福大学Mark Horowitz教授的经典分析,从片外DRAM读取数据的能耗是执行一次浮点运算(FLOP)能耗的数百倍 1。这就是著名的“存储墙”(Memory Wall)危机。

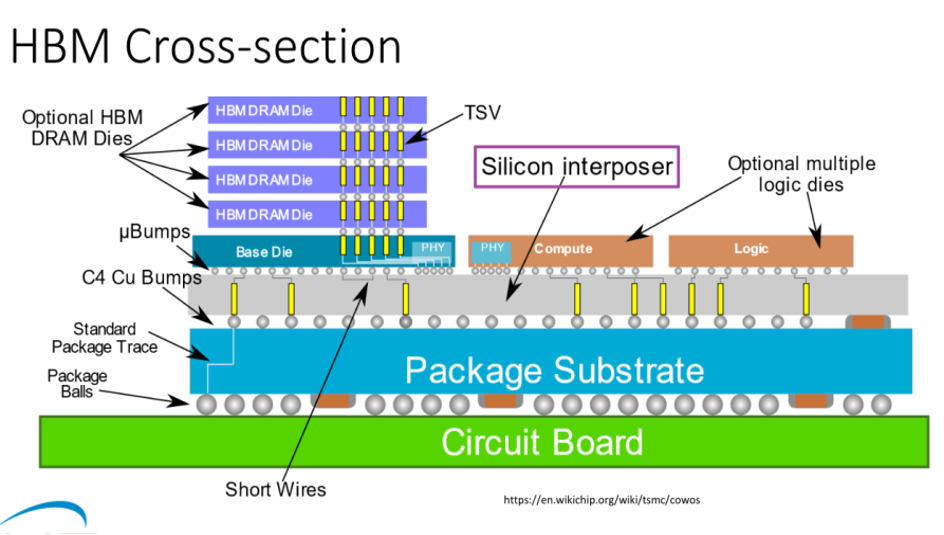

为了应对这一危机,以NVIDIA为代表的GPU厂商采取了“2.5D封装+HBM”的渐进式改良路线,通过硅中介层(Interposer)将高带宽存储器(HBM)尽可能拉近计算核心。然而,这种物理距离的缩短仍然受限于封装尺寸和I/O物理接口,无法从根本上消除数据搬运的开销。相比之下,Cerebras Systems选择了一条更为激进的“晶圆级集成”(Wafer-Scale Integration, WSI)路线。通过将整个晶圆制造为单一芯片(WSE-3),Cerebras实现了计算与存储的原子级融合,彻底打破了传统芯片设计的边界 2。

HBM的架构示意图

HBM的架构示意图

本报告将深入剖析Cerebras加速卡(以CS-3系统及WSE-3芯片为核心)的存储系统设计,详细对比其与GPU HBM及CPU DRAM的架构差异,阐述其如何通过“权重流”(Weight Streaming)技术解决吞吐量瓶颈,并审慎评估这种新型架构是否为MRAM(磁阻随机存取存储器)和ReRAM(阻变存储器)等新兴非易失性存储技术开辟了新的商业与技术增长空间。

2. Cerebras晶圆级引擎(WSE)的存储系统设计解构

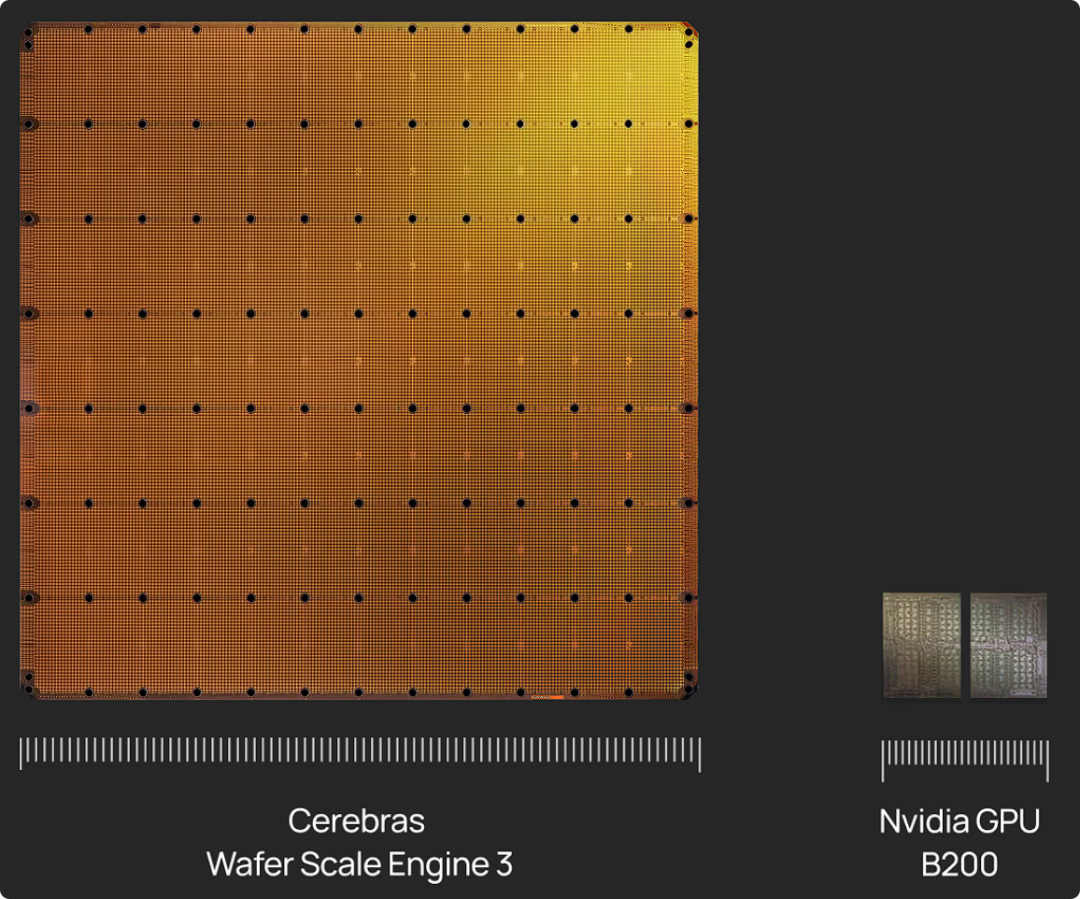

Cerebras WSE-3不仅是世界上最大的芯片,更是一个设计理念完全不同于传统处理器的存储-计算混合体。其核心设计哲学可以概括为:“存储即计算,互联即总线”。在WSE-3高达46,225平方毫米的硅面积上,集成了4万亿个晶体管和90万个AI优化核心 2。然而,其最引人注目的并非算力,而是其独特的存储子系统设计。

WSE-3 样片

WSE-3 样片

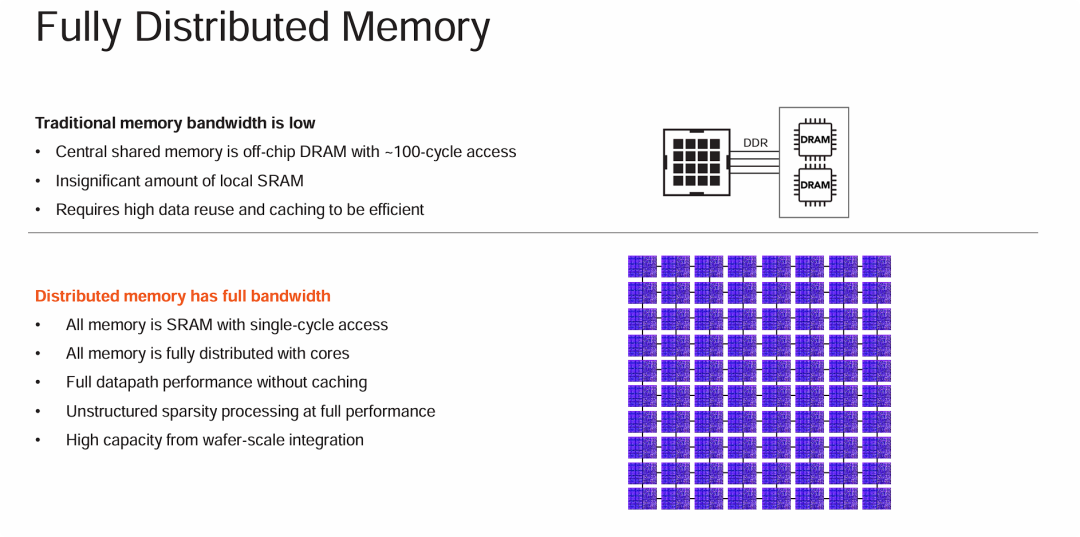

2.1 分布式片上SRAM架构:极致的局部性

与CPU采用的多级缓存(L1/L2/L3)或GPU采用的共享显存(HBM)不同,Cerebras WSE采用了完全分布式的单级存储架构。

完全分布式内存设计

完全分布式内存设计

物理布局与容量:

WSE-3集成了高达44GB的片上SRAM 4。这44GB并非集中在晶圆的某一个区域,而是被精细地打散,均匀分布在90万个计算核心(Sparse Linear Algebra Cores, SLAC)旁边。每个核心大约拥有48KB的专用本地SRAM 6。这种设计使得每个算术逻辑单元(ALU)与其所需的数据之间的物理距离仅为微米级,甚至是纳米级。

访问延迟与确定性:

这种极端的物理邻近性带来了单时钟周期(Single-Cycle) 的访问延迟 6。在传统架构中,如果数据不在L1缓存中,处理器可能需要等待数十甚至数百个周期去L2、L3或主存中抓取数据,导致流水线停顿。而在WSE中,由于内存是软件管理的(Software-Managed Scratchpad Memory),编译器可以精确控制数据的位置,消除了缓存未命中(Cache Miss)带来的不确定性。对于深度学习这种计算模式高度可预测的负载,这种确定性延迟是巨大的性能优势。

聚合带宽的物理学胜利:

分布式设计的最大红利在于带宽。由于90万个核心可以同时以单周期速度读写各自的本地SRAM,WSE-3实现了惊人的21 PB/s(拍字节每秒)的内存带宽 4。这是一个天文数字,为了直观理解:NVIDIA H100配备的HBM3带宽为3.35 TB/s 8。这意味着,一块WSE-3的内部数据吞吐能力相当于6,000多块H100 GPU的总和。这种带宽的爆发式增长,本质上是利用了晶圆级集成的面积优势,将“存储墙”转化为“存储平原”。

2.2 Swarm互联架构:以硅代线

在分布式存储系统中,核心之间的数据交换(通信)往往成为新的瓶颈。Cerebras为此设计了名为Swarm的片上互联网络。

2D Mesh拓扑:

Swarm结构是一个覆盖全晶圆的2D网格,连接所有90万个核心。每个核心配备一个路由器,拥有5个端口(连接东西南北四个邻居及本地核心)6。

极低延迟与高带宽:

该互联架构提供了214 Pb/s(拍比特每秒) 的片上通信带宽 9。由于所有互联线路都在硅片内部蚀刻,而非通过PCB板上的铜线或光纤,信号传输的物理距离极短,且不需要经过复杂的SerDes(串行器/解串器)转换,从而实现了极低的通信延迟和极高的能效比。与GPU集群中依靠InfiniBand或NVLink连接相比,WSE内部的通信能耗降低了几个数量级 10。

硬件级稀疏性支持:

Swarm架构不仅仅是数据传输通道,它还深度集成了稀疏性(Sparsity)处理逻辑。数据以微小的数据包(Wavelets)形式传输,只有非零数据会触发传输和计算 6。如果神经网络中的权重或激活值为零,它们根本不会占用带宽或消耗计算周期。这种“数据流”(Dataflow)触发机制,使得WSE在处理稀疏模型时,性能可以随着稀疏度的增加而线性提升,这是传统SIMD(单指令多数据)架构的GPU难以做到的。

2.3 冗余设计与良率挑战

制造一片完美的12英寸晶圆在半导体工艺中几乎是不可能的,缺陷不可避免。Cerebras通过在硬件层面预留冗余核心(约1%的冗余度)解决了这一问题 11。如果某个区域的SRAM或核心存在制造缺陷,硬件路由引擎会自动绕过该坏点,将逻辑连接重映射到备用的冗余核心上。这使得上层软件看到的永远是一个完美的、完整的矩形计算阵列,无需处理物理层面的瑕疵。

3. 架构对比:WSE SRAM vs. GPU HBM vs. CPU DRAM

为了深入理解Cerebras设计的颠覆性,我们需要将其与当前主流的GPU和CPU存储架构进行多维度的技术对比。

3.1 物理结构与层级差异

特性维度 | CPU (DDR5) | GPU (HBM3/HBM3e) | Cerebras WSE-3 (SRAM) |

|---|---|---|---|

存储介质 | 动态随机存取存储器 (DRAM) | 3D堆叠DRAM (HBM) | 静态随机存取存储器 (SRAM) |

物理位置 | 板级离散 (Off-Chip) | 封装级集成 (On-Package) | 片上集成 (On-Die) |

单芯片/卡容量 | 极高 (TB级) | 中等 (80GB - 192GB) | 较低 (44GB) |

总线位宽 | 窄 (64-bit per DIMM) | 极宽 (1024-bit per stack) | 分布式全互联 (等效无限宽) |

峰值带宽 | 低 (~800 GB/s, 双路) | 高 (3.35 - 8 TB/s) 12 | 极高 (21,000 TB/s) 4 |

访问延迟 | 高 (~70-100 ns) | 中 (~30-50 ns) | 超低 (< 1 ns) |

主要功耗来源 | 接口I/O与长距离传输 | TSV与PHY接口 | 漏电流 (Leakage) |

3.2 GPU上的HBM:带宽与容量的妥协

以NVIDIA H100为例,其采用的HBM3技术代表了DRAM工艺的巅峰。通过硅通孔(TSV)技术将多个DRAM裸片垂直堆叠,HBM极大地提升了位宽和密度 13。然而,HBM本质上仍然是DRAM,需要定期刷新(Refresh),且位于计算核心之外(Off-Chip)。这意味着数据必须穿过物理接口(PHY),跨越硅中介层,这不仅引入了延迟,还消耗了大量能量(约为3.5-7 pJ/bit)15。

更为关键的是,HBM的容量扩展受到物理空间的严格限制。在GPU封装内,能够容纳的HBM堆栈数量是有限的(通常为6-8个),限制了单卡的显存容量(目前最高约141GB-192GB)17。对于参数量达数万亿的LLM,这迫使模型必须被切分到成百上千张GPU上,引发了复杂的分布式训练难题。

3.3 CPU上的DRAM:容量虽大,带宽不足

CPU使用的DDR5内存虽然在容量上具有压倒性优势(单服务器可达数TB),且成本较低,但其带宽对于AI训练来说简直是杯水车薪 18。DDR5的设计初衷是通用计算,强调容量扩展性和模块化,而非极致的并行吞吐。因此,在现代AI栈中,CPU主要负责数据预处理和任务调度,而非核心的张量计算。

3.4 Cerebras的SRAM:速度与容量的权衡

SRAM采用6晶体管(6T)结构,相比DRAM的1T1C结构,其密度较低,即单位容量占用的硅面积更大 20。这就是为什么WSE-3在拥有整个晶圆面积的情况下,仅集成了44GB内存,而面积小得多的H100加上HBM却能拥有80GB以上。

然而,Cerebras的设计哲学是:对于计算核心正在处理的数据,必须以最快速度获取。 44GB虽然存不下整个大模型,但足以容纳超大Batch的中间激活值(Activations)。至于模型参数(Weights),Cerebras通过架构创新将其移除到了片外,我们将在下一节详细阐述。

4. 突破瓶颈:权重流(Weight Streaming)架构如何解决吞吐难题

面对数万亿参数的模型(需要TB级甚至PB级存储),仅有44GB的片上SRAM显然是不够的。传统的GPU方案是“模型并行”(Model Parallelism),即将模型切分,一部分放在GPU A,一部分放在GPU B。这导致了巨大的GPU间通信开销(“通信墙”)。

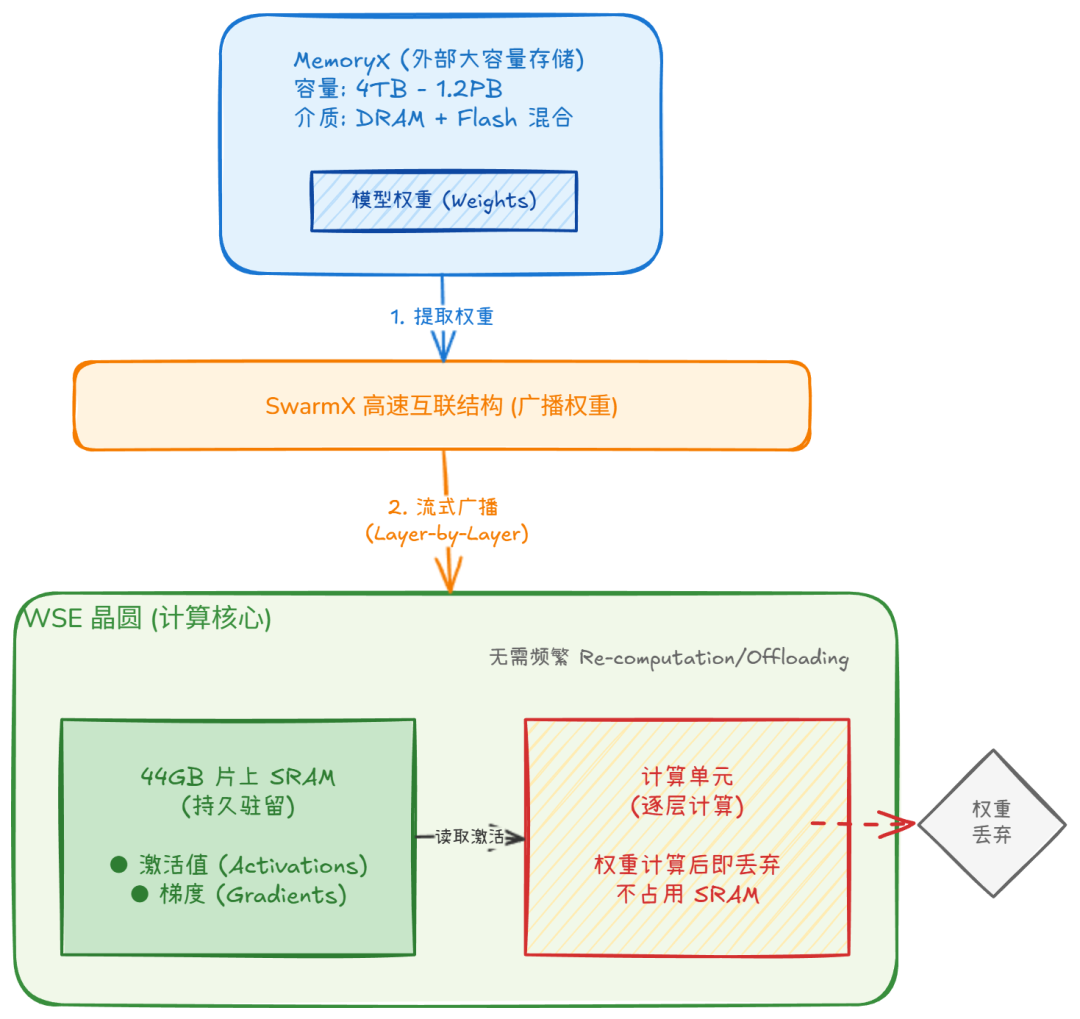

Cerebras通过一种名为 “权重流”(Weight Streaming) 的执行模式,创造性地解决了这一矛盾,实现了计算与存储的彻底解耦 11。

4.1 存算解耦机制

在Cerebras的架构中,模型参数(Weights)并不持久存储在WSE晶圆上,而是存储在名为MemoryX的外部大容量存储设备中。MemoryX支持从4TB到1.2PB的容量配置,足以容纳目前及未来数年内最大的AI模型 5。

工作流程解析:

WSE 存算分离的工作流设计

WSE 存算分离的工作流设计

- 存储: 模型的所有权重存储在MemoryX中(通常由DRAM和Flash混合组成)。

- 流式传输: 训练过程中,权重按层(Layer-by-Layer)流式传输到WSE晶圆上。

- 驻留激活值: WSE晶圆上的44GB SRAM不存权重,而是专门用于存储激活值(Activations) 和梯度。由于WSE足够大,它可以容纳极大Batch Size的激活值,无需像GPU那样频繁地将激活值换出到主存(Re-computation或Offloading)。

- 广播与计算: SwarmX互联结构将权重从MemoryX广播到所有WSE系统。计算完成后,权重即被丢弃(或在反向传播时重新加载),而不需要占用宝贵的片上SRAM 23。

4.2 消除通信瓶颈

这种架构巧妙地将带宽需求进行了转换:

- 计算带宽: 由片上SRAM提供的21 PB/s带宽支持核心进行高强度的矩阵乘法运算。

- 模型加载带宽: 外部MemoryX只需以足够快的速度流式传输权重即可。由于模型计算的算术强度(Arithmetic Intensity)通常很高(即每字节数据需要进行多次运算),外部接口的带宽压力相对较小。Cerebras为此配备了多达12个100GbE光纤接口(总计1.2 Tbps)来连接MemoryX 9,这在流式加载场景下是绰绰有余的。

4.3 线性扩展性

在GPU集群中,随着GPU数量增加,通信开销呈非线性增长,导致性能收益递减。而在Cerebras架构中,增加WSE系统(例如从1台扩展到4台)纯粹是数据并行(Data Parallelism) 的扩展。权重由MemoryX广播,所有WSE执行相同的层计算,只是处理不同的数据分片。梯度在SwarmX交换机中进行规约(Reduce)后再传回MemoryX 21。这种设计使得系统性能几乎可以随节点数量线性增长,极大地简化了大规模集群的部署难度。

5. 新兴存储器(MRAM/ReRAM)的增长机遇分析

Cerebras的架构革新是否为MRAM(磁性存储器)和ReRAM(阻变存储器)等新兴非易失性存储技术(NVM)带来了机会?深入分析表明,这种机会并非存在于WSE核心计算芯片内部,而是存在于其配套的MemoryX系统及边缘端衍生产品中。

5.1 核心计算区:MRAM难以替代SRAM

在WSE芯片内部,SRAM的统治地位在短期内难以撼动。

- 速度差距: AI训练对延迟极度敏感。SRAM可以实现亚纳秒级(<1ns)的读写。目前的STT-MRAM读取速度虽然接近SRAM(5-10ns),但写入速度较慢(10-30ns)且功耗较高 25。对于WSE这种高频翻转的寄存器级应用,MRAM的写延迟是不可接受的。

- 耐久性(Endurance): AI计算中的中间状态(激活值)需要极其频繁的擦写。SRAM拥有无限的耐久性。MRAM虽然比Flash耐用得多(可达10^12次甚至更高),但在作为核心一级缓存使用时,仍可能面临寿命耗尽的风险 27。

- 工艺兼容性: 虽然TSMC已在22nm、16nm甚至尝试在5nm工艺中嵌入MRAM 28,但要在WSE这样超大规模的芯片上保证数十亿个MRAM单元的良率和一致性,其难度远高于SRAM。

5.2 真正的机遇:MemoryX与Checkpointing(断点续训)

MRAM和ReRAM在Cerebras架构中的最佳切入点是MemoryX——那个容量高达PB级的外部参数服务器。

- 极速断点保护(Instant Checkpointing):

在大模型训练中,硬件故障是常态。为了防止进度丢失,系统必须定期将模型状态(Checkpoints)写入硬盘,这通常需要暂停训练数分钟甚至更久,浪费宝贵的计算时间。

- MRAM优势: 作为非易失性内存,MRAM写入速度远快于SSD,且掉电不丢失数据。如果MemoryX采用高密度MRAM(或SCM级内存)构建,可以实现毫秒级的“瞬间存档” 30。这对于拥有数万亿参数的模型来说,意味着巨大的效率提升和风险降低。

- 降低静态功耗:

MemoryX目前主要依赖DRAM来保证流式传输的速度。然而,维持PB级别的DRAM数据需要消耗惊人的刷新功耗(Refresh Power)。

- MRAM优势: MRAM没有静态漏电流,不需要刷新。将MemoryX中的DRAM替换为MRAM(或作为DRAM的持久化层),可以在待机状态下节省大量能源,显著降低数据中心的TCO(总拥有成本)32。

- 边缘推理由此受益:

虽然WSE面向数据中心,但其“权重流”和存算一体理念对边缘AI芯片有深远影响。在边缘端(如汽车、机器人),电池续航是关键。

- eMRAM机遇: 采用嵌入式MRAM(eMRAM)的推理芯片可以将模型权重直接固化在芯片内。设备可以完全断电休眠,唤醒时无需从外部Flash加载模型到SRAM,实现“即时开启”(Instant-on)和零待机功耗 34。Cerebras的成功验证了存算紧密耦合的价值,这将间接推动eMRAM在边缘AI加速卡中的普及。

5.3 模拟计算(Analog Computing)的潜在结合

ReRAM具有独特的模拟特性,可以通过物理定律(基尔霍夫定律)直接在存储阵列中进行矩阵乘法(Compute-in-Memory, CIM)36。虽然Cerebras目前采用的是全数字逻辑,但未来如果追求极致的能效比(TOPS/W),存算一体架构可能会从数字SRAM向模拟ReRAM演进,尽管这需要彻底的架构重写。

6. 数据与规格深度对比表

为了更直观地展示各技术路径的差异,以下表格总结了关键技术指标。

表1:主流AI存储技术规格对比

技术指标 | Cerebras WSE-3 (SRAM) | HBM3e (如H200/B200) | DDR5 DRAM (服务器级) | STT-MRAM (新兴技术) |

|---|---|---|---|---|

单点带宽 | 21 PB/s (聚合) | 4.8 - 8 TB/s | ~0.8 TB/s (双路) | 视接口而定 (通常低于DRAM) |

访问延迟 | < 1 ns (单周期) | ~30-50 ns | ~70-100 ns | 读 ~10ns / 写 ~30ns |

能效 (pJ/bit) | 极低 (无需搬运) | ~3.5 - 4 pJ/bit 16 | >10 pJ/bit 1 | 读低 / 写中等 |

位密度 | 低 (~0.02 µm²/bit) 38 | 极高 (3D堆叠) | 高 (2D平面) | 较高 (1T1MTJ) |

非易失性 | 否 (易失) | 否 (易失) | 否 (易失) | 是 (非易失) |

主要应用场景 | 核心计算、激活值缓存 | 权重存储、显存 | 海量数据缓冲 | Checkpoints、边缘AI权重 |

表2:大规模模型训练扩展性对比

扩展维度 | NVIDIA GPU 集群 | Cerebras WSE + MemoryX |

|---|---|---|

并行策略 | 复杂的混合并行 (数据+张量+流水线) | 简单的纯数据并行 + 权重流 |

通信瓶颈 | GPU间互联 (NVLink/IB),延迟随节点数增加 | 外部存储带宽 (MemoryX Link),内部通信极快 |

内存限制 | 单卡HBM容量 (需切分模型) | 外部MemoryX容量 (最高1.2PB,无需切分) |

开发难度 | 高 (需精细管理模型切分与通信) | 低 (编译器自动映射,单一逻辑设备) |

7. 结论

Cerebras的存储系统设计是对半导体物理限制的一次暴力突围。通过在单一晶圆上集成44GB的分布式SRAM,它构建了一个带宽高达21 PB/s的“数据高速公路”,在物理层面消除了计算核心等待数据的延迟。结合“权重流”技术,这种架构成功地将“容量”与“速度”这两个在传统架构中相互掣肘的因素解耦:WSE负责极致的速度,MemoryX负责无限的容量。

对于GPU而言,HBM是通往高性能的必经之路,但受限于封装和物理距离,它始终是一种妥协。对于MRAM和ReRAM等新兴存储器而言,Cerebras架构并没有提供直接替代其核心SRAM的机会,因为后者在速度和无限耐久性上依然不可替代。然而,Cerebras所倡导的存算解耦与海量参数流式传输的理念,为新兴存储器在辅助存储层(MemoryX)和边缘端存算一体芯片中找到了极具价值的落地场景。特别是在解决超大模型训练的断点保护(Checkpointing)和能耗问题上,非易失性存储技术展现出了不可替代的潜力。

未来,随着光互联(Optical Interconnects)技术的成熟(如CPO),我们有望看到光I/O直接引入WSE晶圆 39,这将进一步拓宽外部存储(可能是基于MRAM的MemoryX)与晶圆引擎之间的通道,从而在更大的尺度上重塑AI计算的存储层级。

参考资料

- The role of AI processor architecture in power consumption efficiency - EDN Network, accessed on January 16, 2026, https://www.edn.com/the-role-of-processor-architectures-in-power-consumption-efficiency/

- Product - Chip - Cerebras, accessed on January 16, 2026, https://www.cerebras.ai/chip

- Revolutionary Breakthrough in Wafer-Scale Artificial Intelligence Chips: An Analysis of Cerebras WSE Technology - Oreate AI Blog, accessed on January 16, 2026, https://www.oreateai.com/blog/revolutionary-breakthrough-in-waferscale-artificial-intelligence-chips-an-analysis-of-cerebras-wse-technology/de30fe2de17dfc977acbf17e3e3a60bf

- A Comparison of the Cerebras Wafer-Scale Integration Technology with Nvidia GPU-based Systems for Artificial Intelligence - arXiv, accessed on January 16, 2026, https://arxiv.org/html/2503.11698v1

- Cerebras Systems Unveils World's Fastest AI Chip with Whopping 4 Trillion Transistors, accessed on January 16, 2026, https://www.cerebras.ai/press-release/cerebras-announces-third-generation-wafer-scale-engine

- Cerebras Architecture Deep Dive - Hot Chips 34, accessed on January 16, 2026, https://hc34.hotchips.org/assets/program/conference/day2/Machine%20Learning/HC2022_Cerebras_Final_v02.pdf

- Cerebras Wafer-Scale Engine Overview - Emergent Mind, accessed on January 16, 2026, https://www.emergentmind.com/topics/cerebras-wafer-scale-engine

- NVIDIA H100: Price, Specs, Benchmarks & Decision Guide - Clarifai, accessed on January 16, 2026, https://www.clarifai.com/blog/nvidia-h100

- Cerebras Wafer-Scale Cluster, accessed on January 16, 2026, https://8968533.fs1.hubspotusercontent-na1.net/hubfs/8968533/Cerebras%20Wafer%20Scale%20Cluster%20datasheet%20-%20final.pdf

- MICRO 2021 Cerebras Keynote, accessed on January 16, 2026, https://microarch.org/micro54/media/lie-keynote.pdf

- Whitepapers - Cerebras, accessed on January 16, 2026, https://www.cerebras.ai/whitepapers

- NVIDIA H200 vs H100: Full Comparison for AI, LLMs, and HPC Workloads | HorizonIQ, accessed on January 16, 2026, https://www.horizoniq.com/blog/h200-vs-h100/

- HBM vs. DDR: Key Differences in Memory Technology Explained - IntuitionLabs, accessed on January 16, 2026, https://intuitionlabs.ai/articles/hbm-vs-ddr-memory-comparison

- What is High Bandwidth Memory 3 (HBM3): Complete Engineering Guide 2025 - Wevolver, accessed on January 16, 2026, https://www.wevolver.com/article/what-is-high-bandwidth-memory-3-hbm3-complete-engineering-guide-2025

- High Bandwidth Memory: Concepts, Architecture, and Applications - Wevolver, accessed on January 16, 2026, https://www.wevolver.com/article/high-bandwidth-memory

- How does the power efficiency of HBM2 and HBM3 memory impact the overall power consumption of a datacenter system? - Massed Compute, accessed on January 16, 2026, https://massedcompute.com/faq-answers/?question=How+does+the+power+efficiency+of+HBM2+and+HBM3+memory+impact+the+overall+power+consumption+of+a+datacenter+system%3F

- NVIDIA H100 vs H200: Key Differences in Performance, Specs, and AI Workloads, accessed on January 16, 2026, https://greennode.ai/blog/compare-h100-vs-h200

- DDR5 Memory Standard: An introduction to the next generation of DRAM module technology, accessed on January 16, 2026, https://www.kingston.com/en/blog/pc-performance/ddr5-overview

- DDR5 Server RAM at a Glance: Technology, Advantages & Areas of Application, accessed on January 16, 2026, https://serverando.de/en/magazine/ddr5-ram-in-profile

- SRAM's Role In Emerging Memories - Semiconductor Engineering, accessed on January 16, 2026, https://semiengineering.com/srams-role-in-emerging-memories/

- Scaling Up and Out: Training Massive Models on Cerebras Systems using Weight Streaming, accessed on January 16, 2026, https://www.cerebras.ai/blog/scaling-up-and-out-training-massive-models-on-cerebras-systems-using-weight-streaming

- Cerebras Systems Announces World's First Brain-Scale Artificial Intelligence Solution, accessed on January 16, 2026, https://www.cerebras.ai/press-release/cerebras-systems-announces-worlds-first-brain-scale-artificial-intelligence-solution

- Weight Streaming Execution - Cerebras AI, accessed on January 16, 2026, https://training-docs.cerebras.ai/rel-2.5.0/concepts/weight-streaming-execution

- Cerebras Systems: Achieving Industry Best AI Performance Through A Systems Approach, accessed on January 16, 2026, https://8968533.fs1.hubspotusercontent-na1.net/hubfs/8968533/Whitepapers/Cerebras-CS-2-Whitepaper.pdf

- Technology comparison for large last-level caches (L3Cs): Low-leakage SRAM, low write-energy STT-RAM, and refresh-optimized eDRAM - ResearchGate, accessed on January 16, 2026, https://www.researchgate.net/publication/261020510_Technology_comparison_for_large_last-level_caches_L3Cs_Low-leakage_SRAM_low_write-energy_STT-RAM_and_refresh-optimized_eDRAM

- STT-MRAM: THE NEXT MEMORY FRONTIER - Cambrian AI Research, accessed on January 16, 2026, https://cambrian-ai.com/wp-content/uploads/edd/2021/03/STT-MRAM-Research-Brief.pdf

- MRAM: Powering the Next Generation of AI Chips : r/Semiconductors - Reddit, accessed on January 16, 2026, https://www.reddit.com/r/Semiconductors/comments/1ldpvr1/mram_powering_the_next_generation_of_ai_chips/

- TSMC's Major Breakthrough: MRAM - 36氪, accessed on January 16, 2026, https://eu.36kr.com/en/p/3513986660637571

- Embedded MRAM, accessed on January 16, 2026, https://www.mram-info.com/tags/embedded-mram

- Checkpointing and Gradient Accumulation Techniques for LLM Training on Low-Memory Systems - ResearchGate, accessed on January 16, 2026, https://www.researchgate.net/publication/398655314_Checkpointing_and_Gradient_Accumulation_Techniques_for_LLM_Training_on_Low-Memory_Systems

- Data Persistence with MRAM Over CXL® | Everspin, accessed on January 16, 2026, https://www.everspin.com/data-persistence-mram-over-cxl%C2%AE

- Breaking Through Memory Bottlenecks: The Next Frontier for AI Performance - EE Times, accessed on January 16, 2026, https://www.eetimes.com/breaking-through-memory-bottlenecks-the-next-frontier-for-ai-performance/

- Traditional Memory vs. MRAM: Revolutionizing Non-Volatile Memory - Everspin Technologies, accessed on January 16, 2026, https://www.everspin.com/traditional-memory-vs-mram-revolutionizing-non-volatile-memory

- ReRAM-Powered Edge AI:A Game-Changer for Energy Efficiency, Cost, and Security, accessed on January 16, 2026, https://www.weebit-nano.com/reram-powered-edge-aia-game-changer-for-energy-efficiency-cost-and-security/

- ReRAM for Energy Efficient AI Inference at the Edge - CrossBar Inc., accessed on January 16, 2026, https://www.crossbar-inc.com/assets/white-papers/ReRAM-for-Energy-Efficient-AI-Inference-at-the-Edge.pdf

- A novel computing-in-memory array based on STT-MRAM using high on–off ratio 2T-1M bit-cell - AIP Publishing, accessed on January 16, 2026, https://pubs.aip.org/aip/adv/article/15/12/125102/3374042/A-novel-computing-in-memory-array-based-on-STT

- Samsung Demonstrates the World's First MRAM Based In-Memory Computing, accessed on January 16, 2026, https://news.samsung.com/global/samsung-demonstrates-the-worlds-first-mram-based-in-memory-computing

- ISSCC N2 and 18A has same SRAM Density. | SemiWiki, accessed on January 16, 2026, https://semiwiki.com/forum/threads/isscc-n2-and-18a-has-same-sram-density.22126/

- Cerebras looks to optical interconnect for 4000x AI boost ... - eeNews Europe, accessed on January 16, 2026, https://www.eenewseurope.com/en/optical-interconnect-boosts-ai-performance-by-4000/

---【本文完】---

👇阅读原文,搜索🔍更多历史文章。

丰子恺-护生画集-囚徒之歌

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-03,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录