Headroom in optics means headroom for innovation:Nvidia关于CPO技术从scale-out到scale-up的路线演进分析

Headroom in optics means headroom for innovation:Nvidia关于CPO技术从scale-out到scale-up的路线演进分析

光芯

发布于 2026-04-03 09:42:25

发布于 2026-04-03 09:42:25

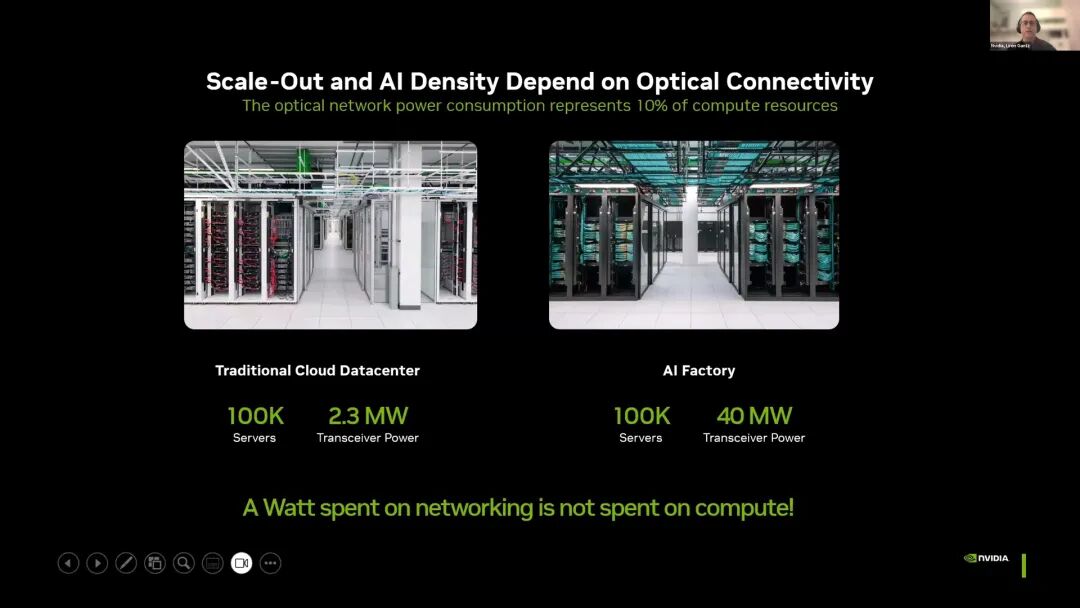

随着AI算力需求的爆发式增长,数据中心的带宽与功耗矛盾已成为制约算力规模扩张的核心瓶颈。共封装光学(CPO)作为破解数据中心互连瓶颈的核心技术,已逐渐成为行业共识,但如何实现CPO从原型到高可靠、大批量制造的规模化落地,仍是行业亟待解决的核心问题。

一、核心前提:CPO的应用场景与终极目标 在展开技术路线对比前,英伟达首先明确了CPO技术的核心应用场景与设计的第一性原则:功耗是CPO技术的核心评判标准。 数据中心的光互连可分为两大核心场景,也是CPO技术的核心发力方向:

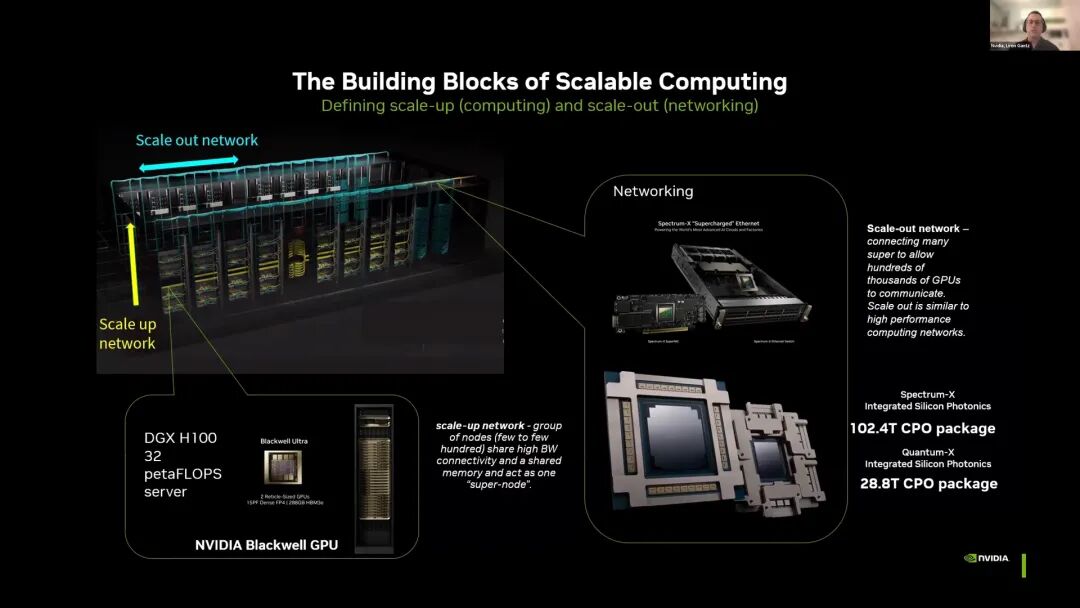

1. Scale-up纵向扩展网络:同一机架内的多GPU互联,目标是将多块GPU整合成一个超大算力单元,对带宽要求极高,目前主流方案仍为铜缆互连; 2. Scale-out横向扩展网络:跨机架、跨数据中心的多集群互联,是当前CPO技术的核心落地场景,也是行业主流方案的聚焦方向。

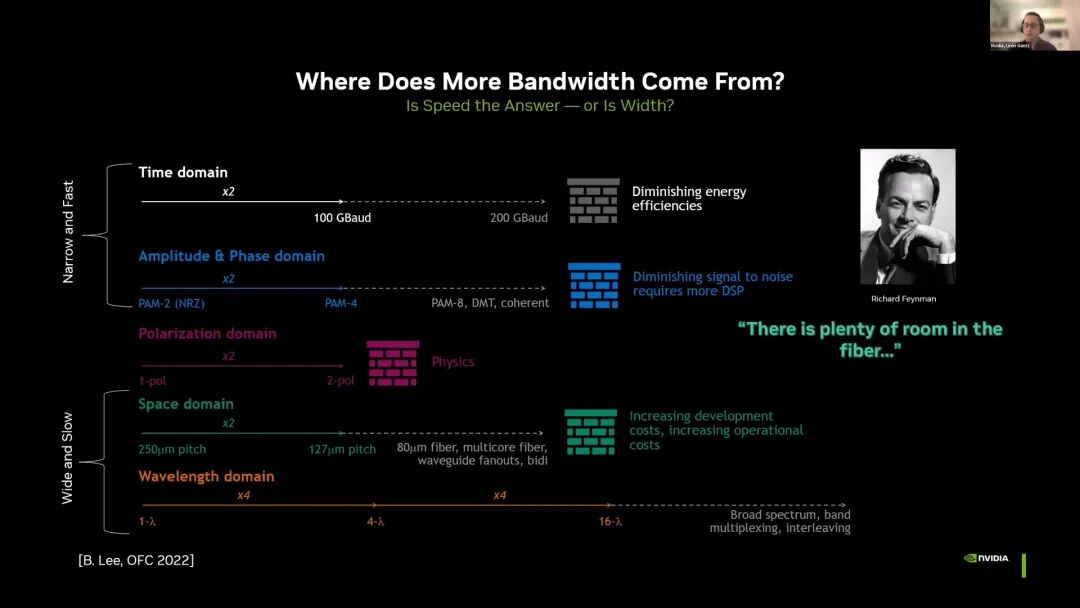

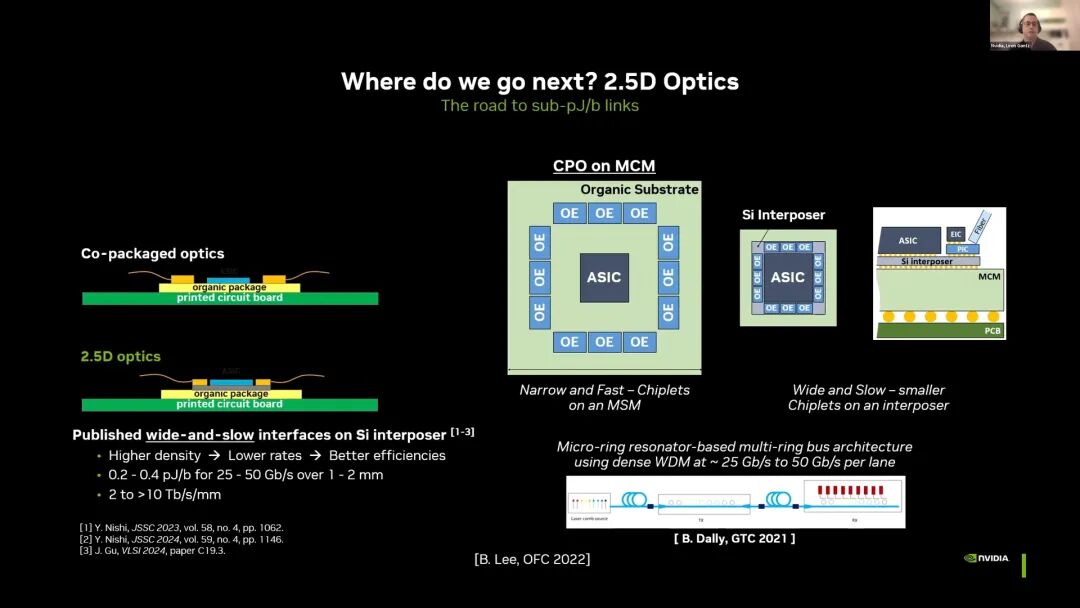

报告明确指出,CPO技术的所有设计,都必须围绕“降低互连功耗”展开——只有将互连功耗降至足够低的水平,才能让更多电力供给AI计算,同时突破铜缆互连的带宽与功耗极限,甚至实现光互连对Scale-up场景铜缆的替代。 二、路径一:窄带高速(Narrow and Fast)—— 现有架构的渐进式升级 窄带高速是当前行业主流的CPO演进路线,也是对现有架构改动最小的渐进式升级方案。 ◆ 核心技术原理

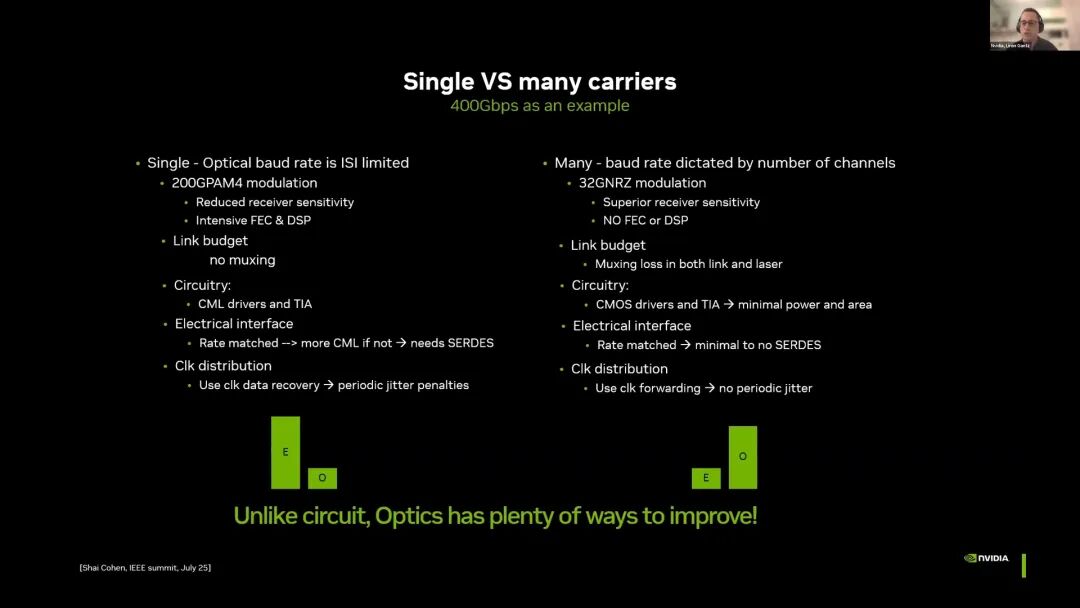

“窄带”指波长维度的窄化,即采用单波长方案;“高速”指通过提升单通道的调制速率,或采用更复杂的调制格式,实现单通道带宽的持续提升。

- 速率维度:持续推进单通道速率升级,从100G、200G向400G及更高水平迭代; - 调制维度:从传统的NRZ调制转向PAM4,未来可进一步向PAM8、相干调制演进。 ◆架构实现 窄带高速路线可完全沿用当前行业成熟的MCM(多芯片模组)架构,仅需在现有方案基础上,升级速度更快的光调制器与驱动电路,无需对封装架构做颠覆性改动,技术落地的门槛更低,供应链成熟度更高。 ◆ 核心瓶颈与挑战

英伟达明确指出,窄带高速路线的核心瓶颈,在于所有技术负担都集中在电子学领域,而非光子学领域——光子学技术已能满足高速调制的需求,但电子学的性能极限,将成为这条路线的天花板。

具体挑战包括: 1. 功耗与信噪比的双重压力:高速复杂调制会导致接收器灵敏度显著下降,必须引入高功耗的FEC(前向纠错)与DSP(数字信号处理)模块,直接推高互连功耗;同时,单通道速率越高,调制带来的信噪比衰减越明显,能效呈现边际递减,功耗无法随速率线性缩放。 2. 电路与接口的高功耗负担:高速调制需要匹配高速CML电路与强驱动级,无法采用低功耗的CMOS驱动;同时,电接口需要高强度的SerDes模块实现数据聚合,不仅带来额外功耗,还会增加互连延迟。 3. 时钟与散热的极限约束:高速时钟的分布本身会带来极高的功耗,且速率越高,电路的损耗越大,所有损耗最终都会转化为热量,导致封装的散热压力急剧加剧,进一步限制了速率的提升空间。 ◆ 供应链需求 窄带高速路线的供应链成熟度相对较高,核心需求集中在更高性能的高速调制器,包括TFLN、TFLT马赫曾德调制器等核心器件的性能升级。

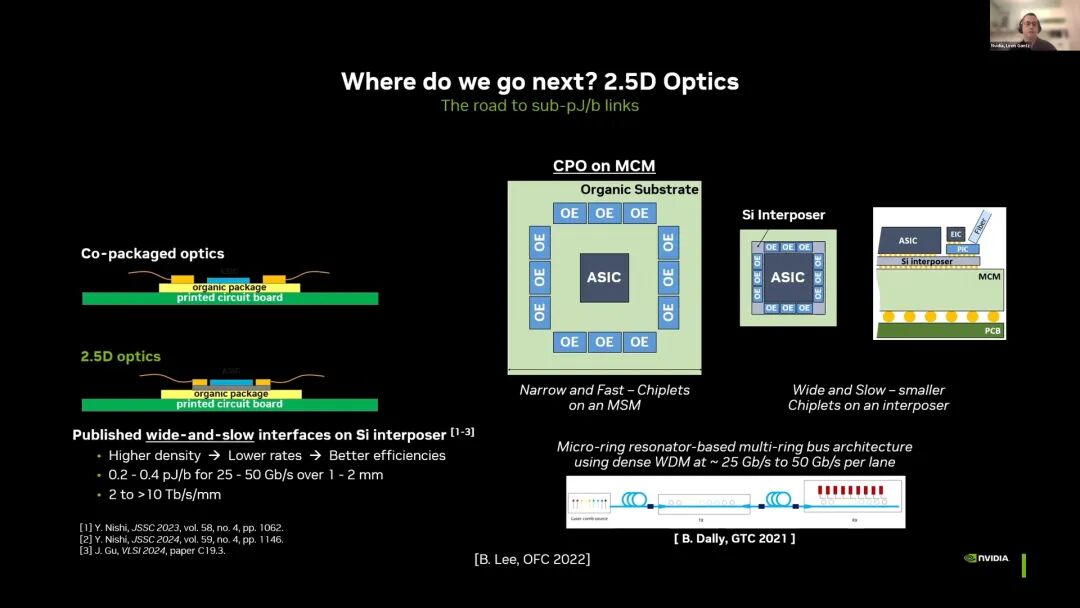

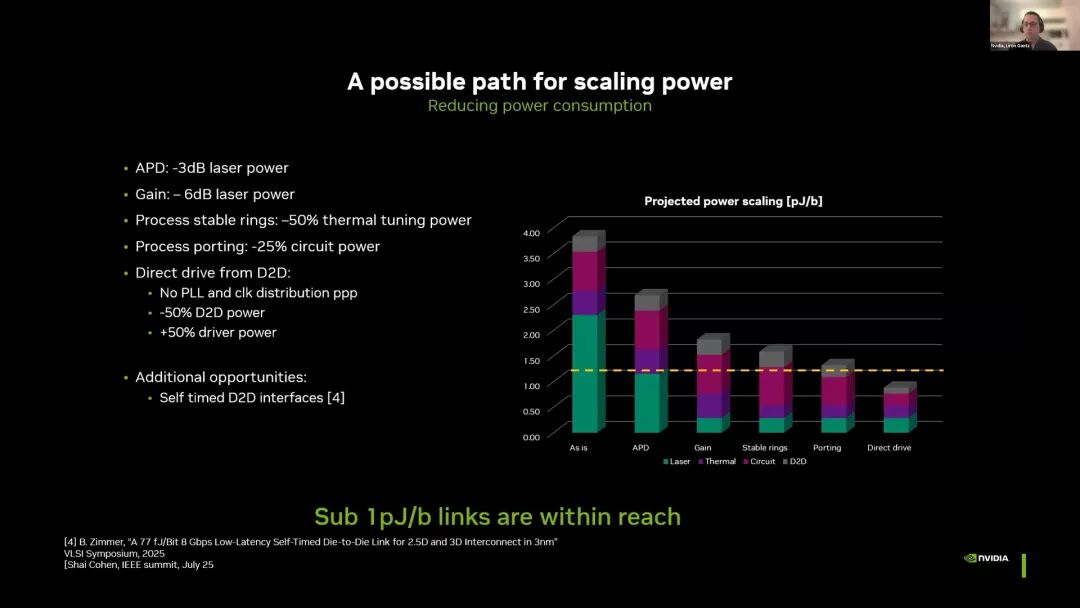

三、路径二:宽带低速(Wide and Slow)—— 面向未来的范式革新 宽而慢是英伟达研究团队重点探索的技术方向,也是其认为CPO技术长期演进的必然归宿,核心是通过维度扩展,将技术负担从电子学转移到光子学领域,从根本上破解功耗瓶颈。 ◆ 核心技术原理 “宽带”指波长与空间维度的扩展,即采用多波长、多通道的方案;“低速”指大幅降低单通道的调制速率,甚至回归成熟的32G NRZ调制,通过“多通道并行”替代“单通道高速”,实现总带宽的提升。 - 空间维度:采用多并行通道扩展带宽; - 波长维度:引入多波长方案,通过光频梳、多波长激光器实现波长域的带宽扩展。 ◆ 架构实现 与窄带高速路线不同,宽带低速路线需要对封装架构做颠覆性调整,必须引入中介层(Interposer) 实现多通道、多波长的光学与电学集成。其核心架构采用多个微环调制器与无源微环接收器,通过多波长并行传输实现带宽扩展,而电子学部分则大幅简化,无需复杂的高速电路。 ◆ 核心优势 报告指出,宽带低速路线的核心优势,是从根本上降低了互连功耗,同时打开了光子学的技术优化空间,其核心收益包括: 1. 全链路功耗大幅降低:低速率NRZ调制带来了更高的接收器灵敏度,无需高功耗的FEC与DSP模块;可采用低功耗的CMOS驱动,无需复杂的高速驱动级;可使用轻量级甚至无SerDes的电接口,同时降低了功耗与延迟;低速时钟的分布功耗也显著降低。 2. 散热压力显著缓解:没有高速电路带来的额外损耗,系统的热生成大幅减少,从根源上缓解了高密度CPO封装的散热难题。 3. 打开了更广阔的技术优化空间:这条路线的技术负担集中在光子学领域,而当前光子学技术仍处于发展初期,“仅仅是触碰到了表面”,优化空间极大。英伟达研究团队指出,可通过APD替代PD提升光增益、引入增益材料、采用工艺感知设计降低制造偏差与热调谐功耗、电子器件向更先进工艺节点升级等方式,持续优化性能,最终将互连功耗降至1pJ/bit以下。

4. 突破场景边界:当互连功耗降至1pJ/bit以下时,光互连将具备对铜缆的性价比优势,可从Scale-out场景渗透至Scale-up场景,替代当前机架内GPU互联的铜缆方案,实现数据中心全场景光互连的覆盖。 ◆ 核心瓶颈与挑战 尽管优势显著,宽带低速路线仍面临两大核心的规模化瓶颈,也是行业需要协同突破的核心方向: 1. 封装技术瓶颈:方案必须引入中介层实现集成,尽管中介层技术在3D集成领域已有应用,但在光子学领域的成熟度仍严重不足,需要台积电、格芯等头部晶圆厂的技术协同,实现光子学中介层的规模化制造。

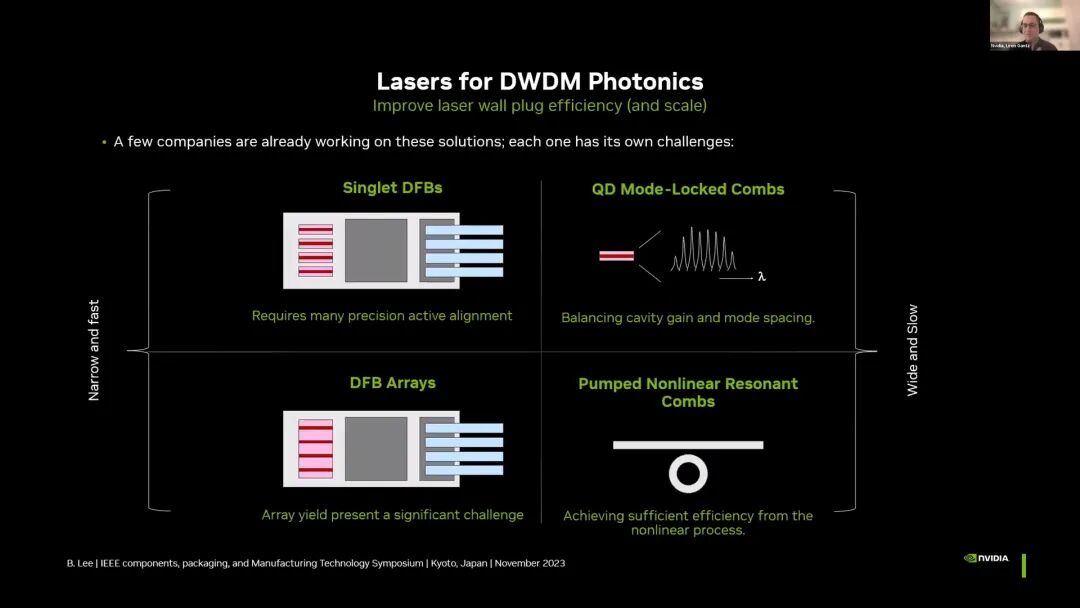

2. 光源技术瓶颈:多波长方案需要能够稳定生成大量波长的光源,核心是光频梳激光器、锁模激光器等新型光源,当前这类器件尚未实现完全的产品化,需要供应链推动其从实验室走向量产。 四、技术路线演进前景:从渐进到革新的必然迁移 针对行业最关注的路线落地周期问题,英伟达研究团队给出了明确的判断: - 短期来看,窄带高速路线仍将延续1-2代技术迭代,依托成熟的供应链实现落地;

- 长期来看,电子学的性能极限将无法支撑速率的持续提升,行业必然会向宽带低速路线迁移,二者并非完全非黑即白,未来可能出现混合过渡方案,例如4波长、8波长的中等速率PAM4方案,逐步完成技术切换。 同时,英伟达也强调,CPO技术的规模化落地,无法依靠单一企业完成,需要全产业链的协同——无论是窄带高速所需的高速调制器,还是宽带低速所需的光频梳、中介层技术,都需要设备商、晶圆厂、器件商、系统厂商的深度配合。 五、全链路共性挑战:热管理与制造协同 除了两条路线各自的瓶颈,英伟达也指出了CPO规模化面临的全行业共性挑战: 1. 热管理与波长稳定性:无论是哪条路线,高密度CPO封装的热管理都是核心难题,尤其是非冷却操作下,高光学功率的波长稳定性控制,需要微热管理、微结构散热等技术的配套升级,也是行业需要持续突破的方向。

2. 制造与测试的全流程协同:CPO技术的规模化,需要从设计、制造、封装到测试的全流程协同,需要建立标准化的设计流程、测试规范,打通光子学与半导体两大领域的技术壁垒,才能真正实现从实验室原型到高量产制造的跨越。

六、总结

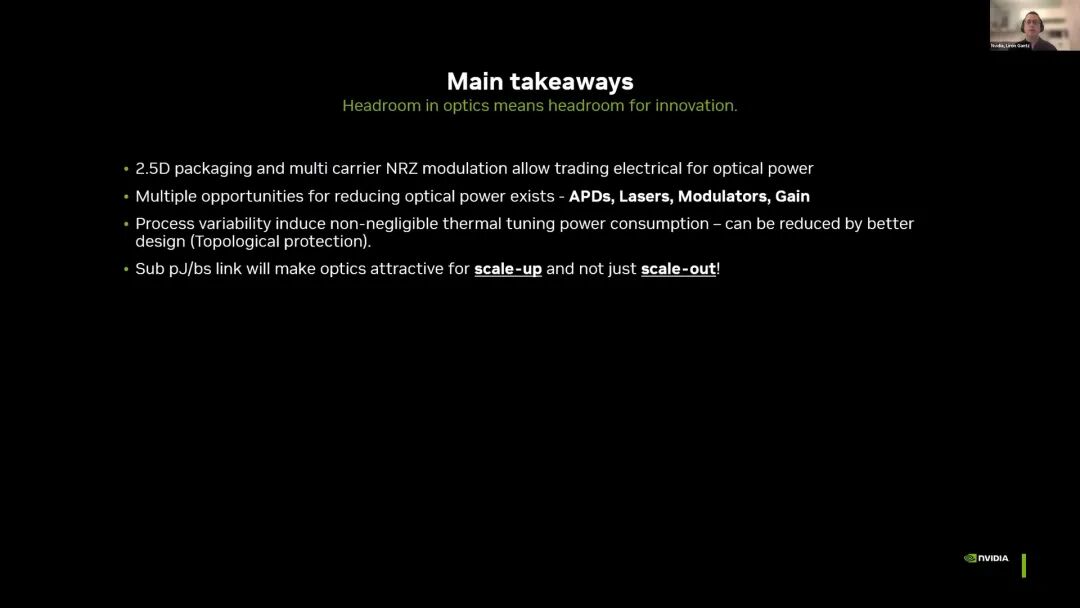

本次演讲以“光子学的发展空间,正是技术创新的潜力空间(Headroom in optics means headroom for innovation)”为核心主旨,系统总结了共封装光学(CPO)技术的核心演进方向与落地价值,核心结论可归纳为四点: 1. 2.5D封装技术搭配多载波NRZ调制方案,可实现CPO架构的功耗重构,将功耗负担从电子端转移至光学端,为能效优化开辟了新路径; 2. 光学链路仍存在充足的功耗优化空间,可通过APD光电探测器、激光器、调制器、增益材料等多维度的技术迭代,持续降低光链路功耗; 3. 制造过程中的工艺波动会带来不可忽视的热调谐功耗,而通过拓扑保护等优化设计手段,可有效降低这部分额外功耗,提升量产方案的能效表现; 4. 当光链路功耗降至亚pJ/bit级别时,光互连的应用场景将从传统的数据中心横向扩展(scale-out),进一步渗透至机架内纵向扩展(scale-up)场景,突破铜缆互连的最后壁垒,实现数据中心全场景光互连的覆盖。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-15,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读