访问std_logic_vectors的2D数组会产生意外的总线冲突。

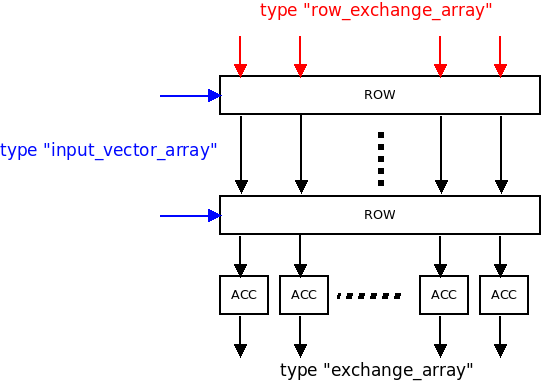

背景:,我正在研究一个通用的收缩阵列。我创建了一个名为"systolic_row“的实体来创建收缩数组的一行。使用std_logic_vectors数组(键入"row_exchange_array")将数据从一行传递到下一行。这个一维数组被打包到另一个数组中,大小为所有生成的rows+2 (输入"exchange_array")。

下面将描述+2的原因: 2D数组的第一个条目是收缩数组的顶部输入,而收缩数组总是设置为0。另一个附加条目有以下原因:收缩数组的最底层行由累加器(除了已经生成的行之外) (enitiy "ACC")组成。累加器与行在相同的2D数组结构上工作。收缩数组的总体输出是这个2d数组的最后一个条目(等于std_logic_vectors的一维数组(输入"row_exchange_array"))。

下图中使用的类型概述。蓝色是收缩阵列的左输入。红色是一维数组,它将信息从一行传递到下一行。黑色将所有红色一维数组统一为一个2D数组,该数组处理从上到下的收缩阵列的所有交换。(因此所有的黑线同时都是红线。)

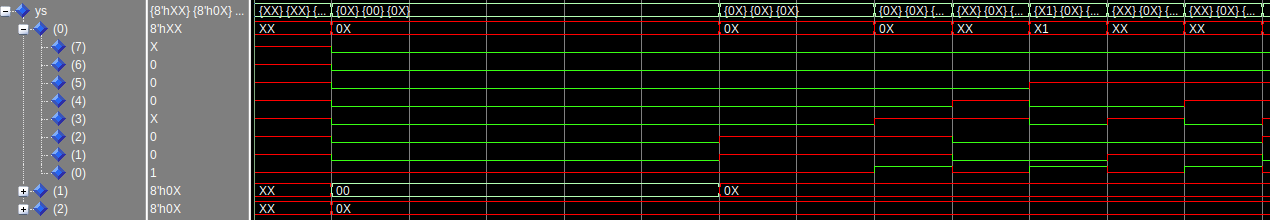

问题:在二维数组中的结果是正确计算的,但一旦我访问最后一个条目,提取出总的结果并将其交给输出,我得到总线冲突,这是我无法解释的。

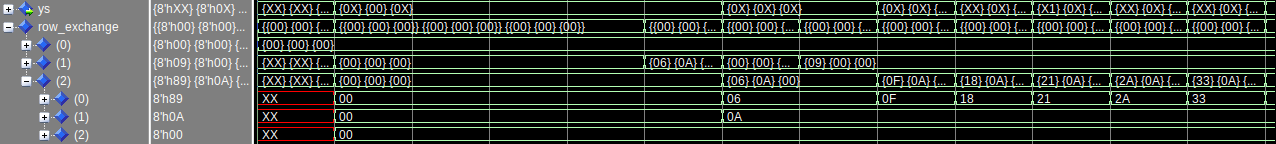

模拟的ROW_WIDTH为3,只生成一行(NUM_ROWS = 1)。

"row_exchange( 0 )“是收缩数组的顶部输入,总是设置为0。

"row_exchange(1)“是唯一生成的行的输出和对ACC的输入。

"row_exchange(2)“是ACC的输出和收缩阵列("ys")的整体输出。

这里,名为"row_exchange“的二维数组的仿真结果("ys”是输出)。在这里,结果是正确的和预期的。

访问二维阵列"row_exchange“后输出("ys")的仿真结果。突然之间,有些地方发生了冲突。

VHDL代码(只摘录一段,因为整个可复制代码都是长的):

所有泛型都在配置文件"config_pkg.vhd“中声明为常量。

-- load configuration file (Generics and data type declaration )

use work.config_pkg.all;

entity systolic_array is

port (

clk : in std_logic;

rstn : in std_logic;

-- "left side" inputs of the systolic array (arrays with size of number of rows, declared in conifguration-vhdl-file)

xs : in input_vector_array;

coeffs : in input_vector_array;

ies : in input_vector_array;

-- enable to declare then valid input data is provided

en : in std_logic;

-- output of systolic array (1D array of std_logic_vectors -> also declared in configuration file)

ys : out row_exchange_array

);

end entity;

architecture behav of systolic_array is

-- array to handle data from one row to the next

-- JUST HERE FOR BETTER UNDERSTANDING, ACCTUALLY DECLARED IN CONFIGURATION FILE BECAUSE IT IS THE SAME TYPE AS THE OUTPUT "ys"

type row_exchange_array is array (0 to ROW_WIDTH-1) of std_logic_vector(DATA_WIDTH-1 downto 0);

-- 2D array to handle all exchanges in the systolic array (from row to row, ACCs and outputs)

type exchange_array is array (0 to NUM_ROWS+1) of row_exchange_array;

signal row_exchange : exchange_array;

begin

-- first row gets all ys set to 0 as input

row_exchange(0) <= (others => (others => '0'));

-- last row is connected to output

-- THIS IS THE THE PROBLEM SEEMS TO OCCUR

ys <= row_exchange(NUM_ROWS+1);

-- generation of the rows

gen_rows : for j in 0 to NUM_ROWS-1 generate

inst_row: systolic_row

port map (

clk => clk, -- clock

i => ies(j), -- "left side" input to systolic array row

coef => coeffs(j), -- "left side" input to systolic array row

x => xs(j), -- "left side" input to systolic array row

y_in => row_exchange(j), -- "top" input to systolic array row

y_out => row_exchange(j+1) -- "bottom" output of systolic array row

);

end generate gen_rows;

-- generation of the accumulators as the last row of the systolic array

gen_accs : for j in 0 to ROW_WIDTH-1 generate

inst_acc: ACC

port map (

clk => clk, -- clock

rstn => rstn, -- reset (low active)

en => en_shift_regs(NUM_ROWS+j), -- enable for the accumulator (signal declaration not shown here, because not part of the problem, I guess)

T => row_exchange(NUM_ROWS)(j), -- input (std_logic_vector)

y => row_exchange(NUM_ROWS+1)(j) -- ouput (std_logic_vector)

);

end generate gen_accs;

end architecture;我已经尝试使用for循环单独访问/编写输出("ys")的所有std_logic_vectors,以查看问题是否是对2D数组本身的访问,但似乎并非如此。

我希望我的解释足够清楚。非常感谢您的帮助和试图理解复杂的代码。如果需要进一步的信息,我很乐意提供。

Stack Overflow用户

发布于 2022-07-06 10:33:16

我正要发布一个小玩具例子,当同样的错误发生时,我意识到了这个问题。

总线冲突的原因不是在设计文件中,而是在testbench中,为了快速编译检查,我匆忙地创建了这个测试平台。问题是,我将值推入到连接到UUT输出的信号中(参见下面的注释部分,也只是一段节选)。

-- Testbench signals to connect to UUT ports

signal clk : std_logic := '1';

signal rstn : std_logic := '0';

signal en : std_logic := '0';

signal xs : input_vector_array;

signal coeffs : input_vector_array;

signal ies : input_vector_array;

signal ys : row_exchange_array;

begin

-- ROW WIDTH AND NUMBER OF ROWS IS SET IN CONFIGURATION FILE

inst_UUT: systolic_array

generic map (

DATA_WIDTH => C_DATA_WIDTH

)

port map (

clk => clk,

rstn => rstn,

en => en,

xs => xs,

coeffs => coeffs,

ies => ies,

ys => ys

);

clk <= not clk after C_CLOCK_PERIOD/2;

-- THOSE ASSIGNMENTS WERE RESPONSIBLE FOR THE BUS CONFLICT

--ys(0) <= x"01";

--ys(1) <= x"00";

--ys(2) <= x"01";非常感谢你的帮助。

https://stackoverflow.com/questions/72857781

复制相似问题