单个组件指令的位宽是多少?

我知道现在组件支持32位结构,所以我假设,和RISCV32一样,它的基本指令集有32位宽的指令(当然,RISCV32支持16位压缩指令和48位指令)。RISC-V的指令主要被解释为左端(在位索引方面).

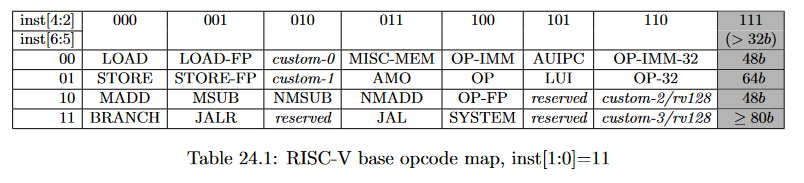

例如,在RISC中,我们可以有一个指令,比如lui (加载上立即注册),它将一个20位的即时嵌入到指令中,有一个5位的字段来编码去编译寄存器,还有一个7位的格式来指定操作码。除其他外,操作码在开头包含两个位,这意味着指令是否被压缩。这是在规范中编码的,其中lui有一个LUI操作码。

RISC-V指令也有规范中指定的各种不同的布局,例如,lui指令采用"U“格式,因此我们确切地知道20位字段的位置和5位目标寄存器在序列化中的位置:

wasm指令的位宽是多少?wasm指令的可能布局是什么?是否有用于组件的压缩指令格式,例如用于非常常见操作的16位指令?

如果组件指令是可变宽度的,那么为解释器编码的指令的宽度如何?

回答 2

Stack Overflow用户

发布于 2022-07-14 00:30:42

二进制WASM字节码有可变长度的指令,而不是固定宽度的RISC CPU.表象有一个例子。

它并不打算直接执行,而是将JITed转换为本机代码,因此,需要对大约32或64位常量执行多条指令的固定宽度格式将使JIT优化器工作更多。并且在WASM二进制格式中不太紧凑,需要解析的指令更多。

对于JIT优化器来说,更好的是知道最终目标是实现一个完整的常量,因为一些ISAs将能够在一条指令中完成这个任务,而另一些则需要将它分割成不同的部分,这取决于ISA。例如,RISC-V为20:12,ARM movw/movk或MIPS为16:16,或者如果常数仅在狭窄区域设置位,则ARM旋转的直接指令可能仍然可以使用一条指令。或者AArch64位模式直接可以在一个32位指令中实现一个常量,比如0x01010101 (或0x0101010101010101)。

TL:不要让JIT把碎片放回一起,然后再分解成为目标机器工作的asm。

一般来说,对于一个流来说,变长并不是什么大问题,因为不管怎么说,流都会被软件解析一次,而不是每次通过循环被硬件反复解码。

Stack Overflow用户

发布于 2022-09-12 10:36:00

以下是当前规范v2.0中与使用说明相关的一些引用(如规范本身所“看到的”):

一些指令也有静态的直接参数,通常是索引或类型注释,它们是指令本身的一部分。一些指令的结构是因为它们对嵌套的指令序列进行了括号。

与筑巢的关系

实现通常会对WebAssembly模块或执行的许多方面施加额外的限制。

然后,注意到的实现限制之一是:

结构化控制指令的嵌套深度

由于规范没有严格定义指令的嵌套深度,而是留给实现来选择,这意味着指令长度不受的限制,无论它们是否按照规范编码为二进制或文本。

即使我们忽略了结构化指令(我们不应该这样做),也有许多指令以向量作为参数。向量长度限制在2^32-1.如果我的记忆正确的话,就会有一个向量向量作为论据的指令。

https://stackoverflow.com/questions/72973945

复制相似问题