如何在SystemVerilog中建立可综合的指令存储器?

我正在SystemVerilog上设计一个MIPS处理器。指令存储器如下所示:

module instr_mem

#(

parameter SIZE = 7 //64

)

(

input logic rst_n,

input logic clk,

input logic [31:0] addr,

output logic [31:0] rd

);

logic [31:0] rom [0 : SIZE-1];

assign rd = rom[addr];

initial begin

rom <= {

32'h0,

32'h2408000F, // a = F

32'h240A0000, // res = 0

32'h01485021, // (*) res = res + a

32'h2508FFFF, // a = a - 1

32'h1500FFFD, // if (a != 0) goto (*)

32'hAC0A0ADD

};

end

endmodule但是这个代码并不将合成为‘黑匣子’/独立模块等等,顶层模块看起来是:“核心,数据内存,<一堆东西,而不是内置内存>”。我试着做IM组合(assign rom = {..}),但是合成也是一样的。

如何制作一个可综合的指令存储器?顺便说一句,有什么指南可以用来编写可合成的代码吗?

回答 1

Stack Overflow用户

发布于 2021-05-26 22:42:37

对于Xilinx,综合指南是Xilinx UG901。每个供应商和工具版本都会有所不同。请参阅综合工具供应商文档以获得指导。例如,我找到了这个版本的UG901。https://www.xilinx.com/support/documentation/sw_manuals/xilinx2017_1/ug901-vivado-synthesis.pdf第4章有一个叫做“ROM HDL编码技术”的章节。这提供了您所要求的指导。

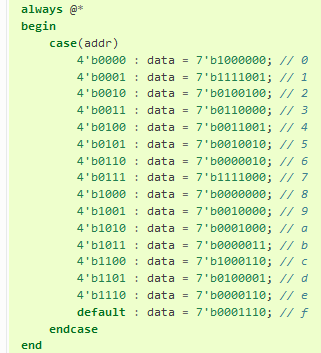

图像中显示的编码样式使用case语句,并将为4位选择变量'addr‘推断ROM。将自己的值放在=赋值的RHS上,而不是映像中列出的值。您应该在示例指定的“数据”位置指定“rom”。图像中显示的变量“数据”仅使用填充维(示例中有打包和解压缩);从“rom”的减速中删除解压维数(“0:SIZE-1”部分)。另外,将'assign = romaddr;‘行改为'assign = rom;使用default: rom = '0来定义所有情况。您可以使用always_comb而不是始终@*作为一种更多的SystemVerilog方法。这更好,因为在模拟中,always_comb总是在t=0上得到评估,而在模拟中总是@*没有。

作为制作SystemVerilog ROM的另一种方法,使用$readmh(),它将文件读入内存变量'rom‘,如SystemVerilog规范第21.4节“从文件加载内存数组数据”中所示。https://ieeexplore.ieee.org/document/8299595](https://ieeexplore.ieee.org/document/8299595%5D%5B3%5D)

这里有一个关于$readmh()的很好的教程。https://projectf.io/posts/initialize-memory-in-verilog/

这种方法(使用文件& $readmh() )可能需要在指向$readmemh()读取的文件的项目根目录上建立一个符号链接。使用此方法时,定义包含打包和解压维度的“rom”变量。这种方法更适合在ROM中存储大量数据的情况下使用。在一个案例陈述中维护数十万行是不容易的。

SystemVerilog综合的一个一般参考是: Stu Sutherland的“SystemVerilog建模与仿真与综合:使用SystemVerilog进行ASIC与FPGA设计”是对SystemVerilog的一个很好的参考,重点是综合。

https://stackoverflow.com/questions/67701135

复制相似问题