使用Systemverilog读取,然后打印二进制文件。第一个字节读取和打印确定,麻烦\w字节包含一个1的毫秒位位置遇到

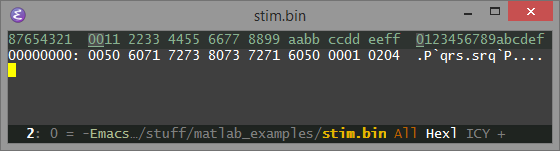

下面的Systemverilog代码是一个单一的文件测试平台,它使用$fread将二进制文件读入内存,然后打印内存内容。二进制文件是16个字节,它的视图包含在下面(这就是我期望Systemverilog代码打印的)。

输出与我所期望的前6 (0-5)字节相匹配。此时,预期的输出为0x80,但是打印的输出是以0xef开头的3个字节的序列,这些字节不在刺激文件中。在这3个字节之后,输出再次匹配刺激。似乎当二进制字节读取的第7位为1时,就会发生错误。它几乎像数据被视为签名,但它不是,它的二进制数据打印为十六进制。内存被定义为没有符号的类型逻辑。

这类似于本文中的一个问题/答案:Read binary file data in Verilog into 2D Array。但是,我的代码在$fopen语句中没有相同的问题(我使用"rb"),因此解决方案不适用于这个问题。

Systemverilog规范1800-2012在21.3.4.4节中声明,读取二进制数据可以使用$fread读取二进制文件,并继续说明如何读取二进制文件。我相信这个例子是符合该节所述的。

代码被张贴在EDA游乐场上,这样用户就可以看到并运行它。https://www.edaplayground.com/x/5wzA您需要登录才能运行并下载。登录是免费的。它为HDL模拟提供了基于云的全版本的行业标准工具的访问。

还尝试在EDA游乐场上运行3种不同的模拟器。它们都产生了相同的结果。

尝试重新排列stim.bin文件,以便0x80值出现在文件的开头而不是中间。在这种情况下,在testbench打印输出开始时也会发生错误。

也许Systemverilog代码很好,问题是二进制文件?我为它的内容提供了emacs十六进制模式显示的屏幕截图。也看到了另一个观众,它看上去也是一样的。您可以在EDA游乐场上运行时下载它,以便在另一个编辑器中检查它。二进制文件由GNU Octave生成。

希望有一个使用Systemverilog $fread的解决方案,而不是其他的解决方案来调试原始的,而不是绕过它(学习)。这将被开发成一个Systemverilog测试平台,它将从Octave/Matlab生成的二进制文件中读取的刺激应用到Systemverilog。由于文件访问速度快,更倾向于二进制fileIO。

为什么Systemverilog为mem6打印0xef而不是0x80

module tb();

// file descriptors

int read_file_descriptor;

// memory

logic [7:0] mem [15:0];

// ---------------------------------------------------------------------------

// Open the file

// ---------------------------------------------------------------------------

task open_file();

$display("Opening file");

read_file_descriptor=$fopen("stim.bin","rb");

endtask

// ---------------------------------------------------------------------------

// Read the contents of file descriptor

// ---------------------------------------------------------------------------

task readBinFile2Mem ();

int n_Temp;

n_Temp = $fread(mem, read_file_descriptor);

$display("n_Temp = %0d",n_Temp);

endtask

// ---------------------------------------------------------------------------

// Close the file

// ---------------------------------------------------------------------------

task close_file();

$display("Closing the file");

$fclose(read_file_descriptor);

endtask

// ---------------------------------------------------------------------------

// Shut down testbench

// ---------------------------------------------------------------------------

task shut_down();

$stop;

endtask

// ---------------------------------------------------------------------------

// Print memory contents

// ---------------------------------------------------------------------------

task printMem();

foreach(mem[i])

$display("mem[%0d] = %h",i,mem[i]);

endtask

// ---------------------------------------------------------------------------

// Main execution loop

// ---------------------------------------------------------------------------

initial

begin :initial_block

open_file;

readBinFile2Mem;

close_file;

printMem;

shut_down;

end :initial_block

endmodule二进制刺激文件:

实际产出:

Opening file

n_Temp = 16

Closing the file

mem[15] = 01

mem[14] = 00

mem[13] = 50

mem[12] = 60

mem[11] = 71

mem[10] = 72

mem[9] = 73

mem[8] = bd

mem[7] = bf

mem[6] = ef

mem[5] = 73

mem[4] = 72

mem[3] = 71

mem[2] = 60

mem[1] = 50

mem[0] = 00更新:运行了一个实验,以测试二进制文件在上传到EDA游乐场的过程中是否会被修改。这些步骤不涉及Systemverilog代码,它只是一个文件上传/下载。

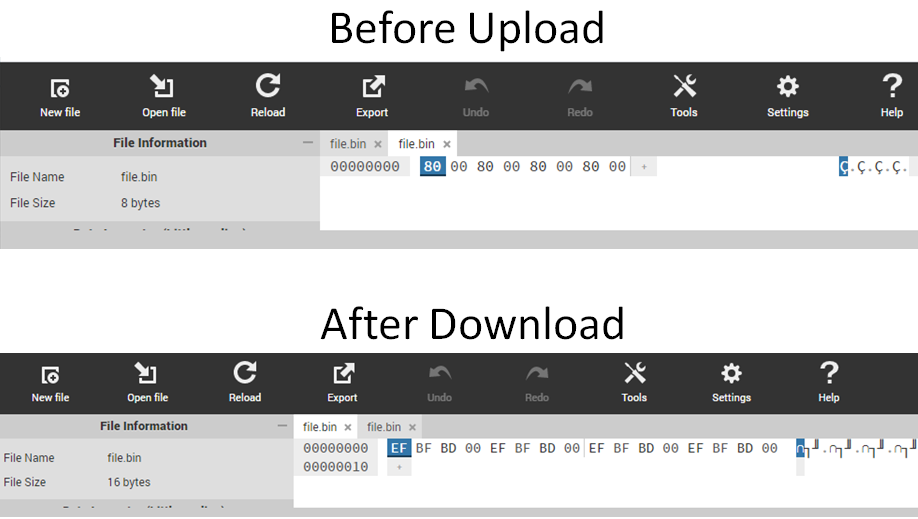

步骤:(使用https://hexed.it/创建和查看二进制文件)

用十六进制模式创建/保存二进制文件,以十六进制模式创建新的playground

- Upload新创建的二进制文件到新playground

- Check上的“运行后下载文件”框中,从操场上运行

- 查看二进制文件,在我的示例中,它在上传/下载过程中被修改。结果的屏幕截图如下:

本实验在两个不同的Windows工作站上进行。基于这些结果和评论,我将结束这个问题,并认为这不是Systemverilog问题,而是与上传/下载二进制文件到EDA游乐场有关。感谢那些发表评论的人。

回答 1

Stack Overflow用户

发布于 2020-07-22 13:52:29

testbench产生的意外输出是由于在上传到EDA游乐场期间/之后对二进制刺激文件进行的修改。Systemverilog执行用于打印二进制文件内容的操作。

这一结论是基于社区的评论和实验结果提供的,在最后的更新问题。给出了一个详细的程序,以便其他人可以重复这个实验。

https://stackoverflow.com/questions/63000128

复制相似问题