为什么MIPS在计算分支目标地址时使用'PC+4‘作为基址?

为什么MIPS在计算分支目标地址时使用'PC+4‘作为基址?

提问于 2020-05-12 20:11:13

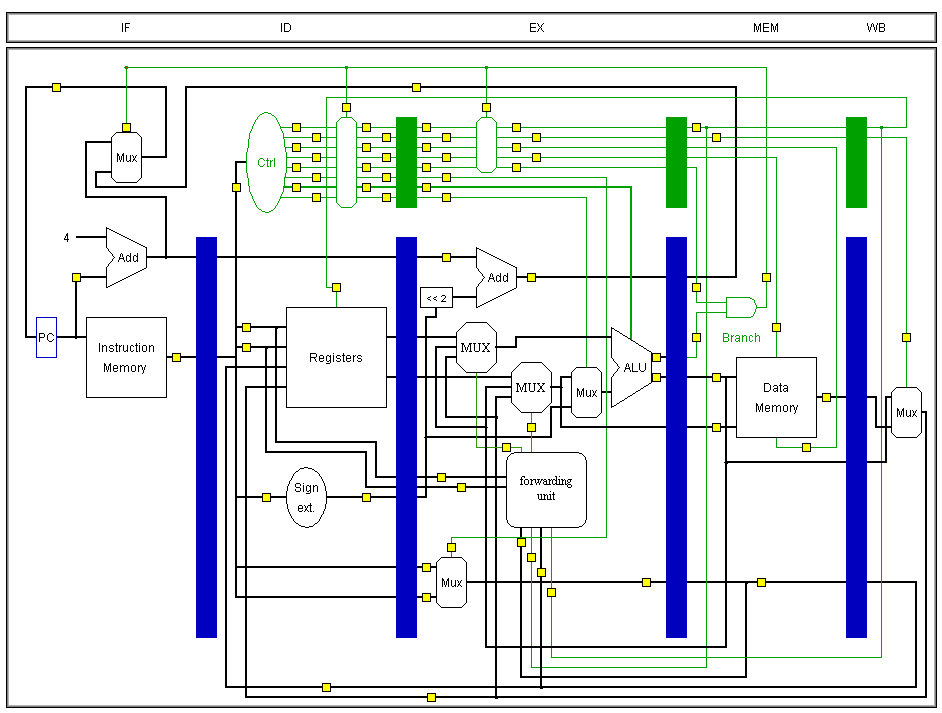

如果您观察到MIPS 5级管道(1.1.Instruction-2.1.Instruction- 3.Execute -4. 4.Memory -5 5.WriteBack),则在执行阶段最终确定是否分支。

从图像中可以看到,ALU的上输出输入到MUX中,以便在普通PC步骤和分支之间进行选择。

因此,当CPU决定是否分支时,从相应指令的IF阶段已经通过了两个管道级。假设PC1 = PC (如果时)和PC2 = PC (决定分支)。因此,PC2 = PC1+4。为了将PC2还原为PC1+4,需要额外的硬件。(用于PC2-4操作)

尽管存在这个缺点,但我想知道为什么MIPS处理器使用PC+4作为基址而不是使用PC+8呢?

回答 1

Stack Overflow用户

回答已采纳

发布于 2020-05-12 20:38:03

如果您需要更多的硬件来获得PC+8,或者如果您认为可以跳过管道阶段并让分支偏移量应用于获取阶段地址的值,则会使异常返回处理变得更加复杂。(MIPS分支延迟时隙意味着从异常返回需要一个PC和单独的next-PC,以防分支延迟时隙发生故障。)

另外,如果抓取货摊而不提前电脑,怎么办?

在实际的典型MIPS中,branch latency is 1 cycle,所以分支相对于分支中的指令是有意义的--延迟时隙,而不是后面的两个指令;How to Calculate Jump Target Address and Branch Target Address?。

另外,IF阶段已经计算了PC+4,因此它可以将该值与指令一起发送到管道中。如果可以避免,您就不需要很长的连线;通过管道阶段之间的闩锁发送PC+4值是有意义的。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/61761068

复制相关文章

相似问题