英特尔是否为其GPU有单独的指令集?

假设我使用的是基于英特尔x64的笔记本电脑,没有专用的GPU。我必须有一些GPU在飞机上,否则我的屏幕将无法工作,对吗?

- 星载CPU通常嵌入到CPU中吗?

- 英特尔是否有一个单独的指令集为它的GPU?如果是的话有医生吗?

- GPU指令与CPU有很大不同吗?例如,GPU也有

shift、add、load、store指令吗?他们还有哪些常规CPU没有的指令? - 星载GPU与专用GPU的指令集/流水线之间是否有区别?或者区别仅仅是额外的内核和专用RAM的数量?

- 在具有专用GPU的机器上,如何在GPU上执行从C++ OpenGL代码生成的指令,而不是以常规CPU结束?

回答 1

Stack Overflow用户

发布于 2021-01-19 05:08:15

全硬件参考

您可以在01.org上找到英特尔图形控制器的完整文档

硬件规范- PRMs发布: Paul Parenteau最后修改:2020年6月15日

回答问题2:是的,有单独的组装说明,如下所示(来自"GEN组件简介")

英特尔GPU总成

通常,所有指令都采用以下形式:

[(pred)] opcode (exec-size|exec-offset) dst src0 [src1] [src2](pred)是可选谓词。我们现在要跳过它。

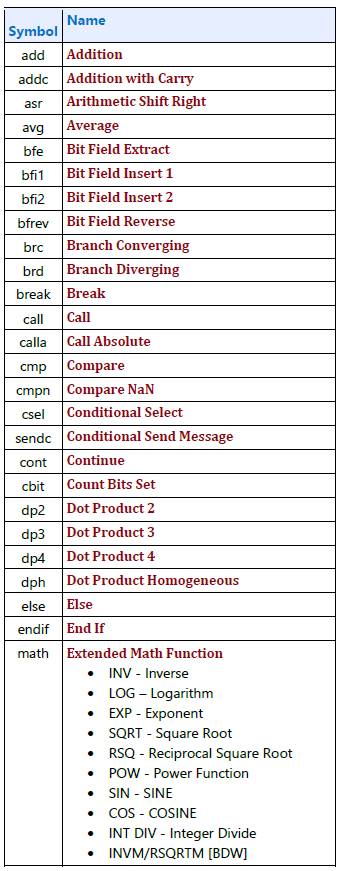

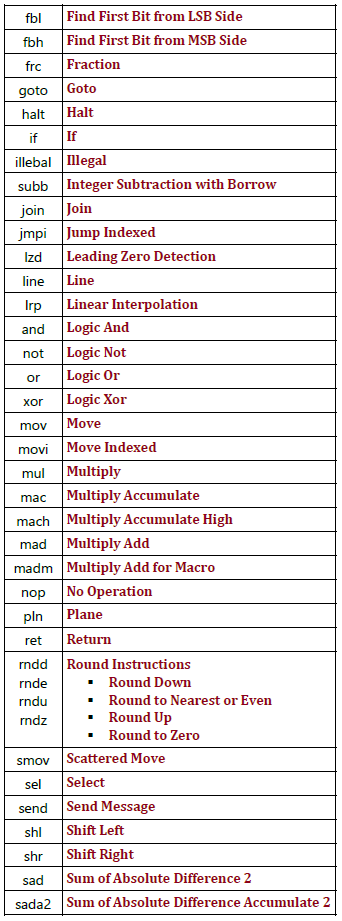

opcode是指令的符号,如add或mov (下面有完整的操作码表)。

exec-size是指令的SIMD宽度,我们的体系结构可以是1、2、4、8或16。在SIMD32编译中,通常有两个执行大小为8或16的指令分组为一个。

exec-offset是告诉欧盟的部分,ARF寄存器的哪一部分要读或写,例如(8\M24)参考执行掩码的第24-31位。当发出SIMD16或SIMD32代码时,如下所示:

mov (8|M0) r11.0<1>:q r5.0<8;8,1>:d // id:1

mov (8|M8) r13.0<1>:q r6.0<8;8,1>:d // id:1

mov (8|M16) r15.0<1>:q r9.0<8;8,1>:d // id:1

mov (8|M24) r17.0<1>:q r10.0<8;8,1>:d // id:1( SIMD32组装的mov指令)

由于GRF中每个操作数可以访问多少字节的限制,编译器必须发出四个8范围的操作。

dst是一个目标寄存器

src0是一个源寄存器

src1是一个可选的源寄存器。注意,它也可能是一个即时值,比如0x3F000000:f (0.5)或0x2A:ud (42)。

src2是一个可选的源寄存器。

普通登记册(GRF)登记册

每个线程都有128个寄存器的专用空间,r0通过r127。每个寄存器是256位或32字节。

体系结构寄存器(ARF)寄存器

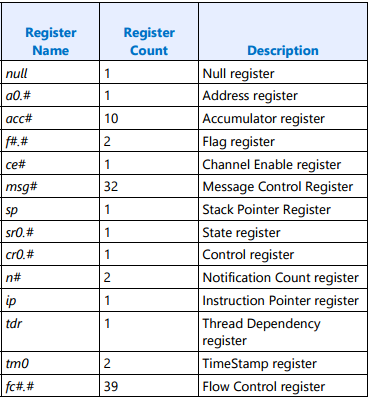

在上面的汇编代码中,我们只看到其中一个特殊寄存器,即null寄存器,它通常用作用于写入和指示线程结束的发送指令的目的地。以下是其他体系结构寄存器的完整表:

通用(一般)大会指示

https://stackoverflow.com/questions/61665743

复制相似问题