用20 pin单片机IO引脚驱动高频输出(32 Pin)

我需要驱动一个32千赫方波在19针的R8C/36C控制器。引脚是不可转让的(电路设计已经完成)。

软件设计使用了一个250秒的中断来模拟多任务处理,但这只适用于2 2Khz的全波。

我是否需要为32 Khz的驱动器创建另一个更高优先级的中断,还是还有其他一些我不知道的技巧?

- R8C/36C硬件手册

- R8C/36C软件手册

回答 4

Stack Overflow用户

发布于 2011-07-22 21:13:37

我不太熟悉RC8和Renesas在性能方面的内容,但是它是一个CISC处理器,每个指令通常有4个周期,所以让我们估计一下大约4个MIPS?有些指令要长得多,除法最多可达30个周期。

因此,如果您创建一个64 the定时器并在每个中断上翻转输出,您在每个中断之间有大约63个指令,您有中断延迟加上翻转位的代码。如果它能工作,它很可能构成一个巨大的CPU负载,并可能影响其他操作的及时性。

现实点,如果没有重新设计,这个项目可能是不可行的。在我看来,你已经在用4 4KHz操作系统来强调它了--以这个速度计算的软件开销很可能是CPU负载的很大一部分。

添加了

我之前曾建议在中断之间使用6条指令--计算器中的手指故障,我已经将估计值改为63,并将我的结论调整到“几乎不可行”。

然而,我再次查看了数据表,中断延迟是可变的,因为指令执行是可变的,当前的指令必须在中断服务之前完成,最糟糕的情况是,当DIVX指令执行时,它占用中断例程的第一个指令之前的51个周期。即2.55us,当您需要中断来每15.625us触发一次时,可变的延迟将造成很大的抖动,构成您的CPU总时间的6%至16 %,甚至不考虑ISR本身所使用的时间。另外,如果中断本身被抢占,或者当这个中断到期时,一个更高优先级的中断正在运行,则会产生进一步的抖动。

它是否工作将取决于32 the的准确性和抖动限制,以及您的代码需要完成的其他任何事情。

Stack Overflow用户

发布于 2011-07-23 20:22:05

正如许多人指出的那样,如果32 the的时钟是用gpio生成的,那么从硬件的角度来看,这种设计似乎不是很好。

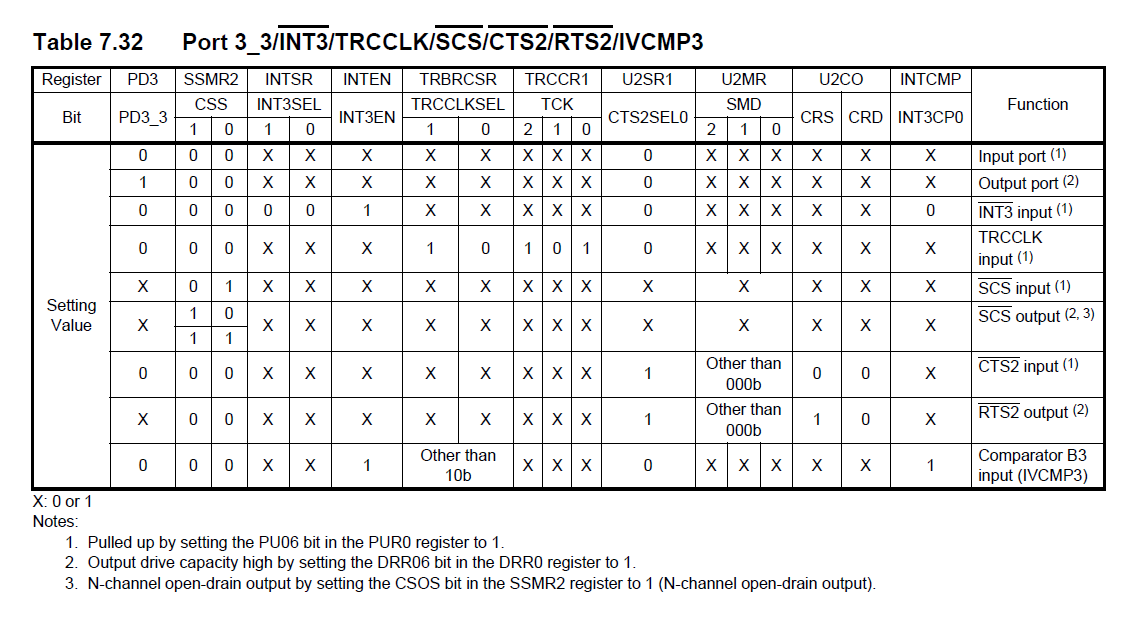

然而,我不知道你的处境有多绝望,我也不知道涉及的数量。但如果它是一个原型或非常短的系列,而20引脚是免费的,你可以短路引脚19和20,安装引脚19作为输入和20作为输出。由于引脚20可以用作来自计时器rd的输出,您可以设置该计时器输出32 the而不使用任何中断。

我不是renesas的微专家,但我说的是我在你附上的数据表中看到的,以及以前与其他mcu的经验。

我希望这能帮到你。

Stack Overflow用户

发布于 2011-07-22 17:42:07

看看芯片的数据表:

看起来,您唯一的实际选择是使用引脚作为通用输出端口。唯一可用的输出模式似乎是泛型输出端口。

https://stackoverflow.com/questions/6793686

复制相似问题