VHDL输入端口设置为高阻抗

VHDL输入端口设置为高阻抗

提问于 2015-11-30 19:58:24

更新

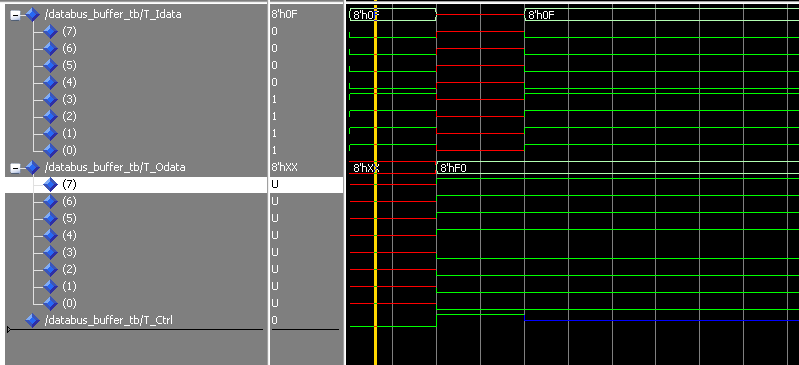

我更新了testbench代码,但现在似乎数据库并不驱动信号。

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY databus_buffer_tb IS

END databus_buffer_tb;

ARCHITECTURE dataflow OF databus_buffer_tb IS

SIGNAL T_Idata:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL T_Odata:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL T_Ctrl:STD_LOGIC:='0';

COMPONENT databus_buffer IS

PORT

(

--IDATA represent the bus lines that comes from the uC for reading and writing;

--ODATA represents the bus lines that communicate with the internal bus;

IDATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000";

CTRL: IN STD_LOGIC;

ODATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000"

);

END COMPONENT;

BEGIN

databuffer:databus_buffer PORT MAP

(

IDATA=>T_Idata,

CTRL=>T_Ctrl,

ODATA=>T_Odata

);

PROCESS

BEGIN

T_Idata<="00001111";

T_Ctrl<='0';

WAIT FOR 10 ns;

assert(T_Odata="00001111") REPORT "Expected 00001111" SEVERITY error;

T_Odata<="11110000";

T_Ctrl<='1';

WAIT FOR 10 ns;

assert(T_Idata="11110000") REPORT "Expected 11110000" SEVERITY error;

T_Ctrl<='Z';

WAIT FOR 10 ns;

assert(T_Idata="ZZZZZZZZ") REPORT "Expected Z FOR T_Idata" SEVERITY error;

assert(T_Odata="ZZZZZZZZ") REPORT "Expected Z FOR T_Odata" SEVERITY error;

wait;

END PROCESS;

END dataflow;和

我试图理解如何用VHDL实现INOUT端口,但失败了。以下是代码:

library ieee;

use ieee.std_logic_1164.all;

----------------------------

-- Databus Buffer

----------------------------

ENTITY databus_buffer IS

-- data bus buffer have the next ports:

-- IDATA: 8 bit bus ->inout

-- CTRL: 1 bit control ->in

-- ODATA: 8 bit bus ->inout

PORT

(

--IDATA represent the bus lines that comes from the uC for reading and writing;

--ODATA represents the bus lines that communicate with the internal bus;

IDATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0);

CTRL: IN STD_LOGIC;

ODATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END databus_buffer;

ARCHITECTURE behaviour OF databus_buffer IS

-- behaviour of databus buffer;

BEGIN

-- is a 3 state bidirection 8 bit buffer.

-- if CTRL is 1, IDATA=ODATA; reading from counter operation

-- if CTRL is 0, ODATA=IDATA; writing to control word

-- if CTRL is Z, IDATA=Z; this happens when nor read and write are active but

-- cs is active;

-- also, data bus can be in 3rd state if the chip is not selected, this means

-- that CTRL will be Z;

ODATA<=IDATA WHEN CTRL='0' else "ZZZZZZZZ" WHEN CTRL='Z' else (OTHERS=>'Z');

IDATA<=ODATA WHEN CTRL='1' else "ZZZZZZZZ" WHEN CTRL='Z' else (OTHERS=>'Z');

END behaviour; 此代码在CTRL为0或1时工作,但当我将CTRL设置为'Z‘时,在高阻抗中,IDATA和ODATA没有设置为高阻抗。

我的测试台:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY databus_buffer_tb IS

END databus_buffer_tb;

ARCHITECTURE dataflow OF databus_buffer_tb IS

SIGNAL T_Idata:STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL T_Odata:STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL T_Ctrl:STD_LOGIC:='0';

COMPONENT databus_buffer IS

PORT

(

--IDATA represent the bus lines that comes from the uC for reading and writing;

--ODATA represents the bus lines that communicate with the internal bus;

IDATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0);

CTRL: IN STD_LOGIC;

ODATA: INOUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END COMPONENT;

BEGIN

databuffer:databus_buffer PORT MAP

(

IDATA=>T_Idata,

CTRL=>T_Ctrl,

ODATA=>T_Odata

);

PROCESS

BEGIN

T_Idata<="00000000";

T_Odata<="00000000";

T_Ctrl<='0';

T_Idata<="00001111";

T_ODATA<="ZZZZZZZZ";

T_Ctrl<='0';

WAIT FOR 10 ns;

assert(T_Odata="00001111") REPORT "Expected 00001111" SEVERITY error;

T_Odata<="11110000";

T_IDATA<="ZZZZZZZZ";

T_Ctrl<='1';

WAIT FOR 10 ns;

assert(T_Idata="11110000") REPORT "Expected 11110000" SEVERITY error;

T_IData<="00000000";

T_OData<="00000000";

T_Ctrl<='Z';

WAIT FOR 10 ns;

assert(T_Idata="ZZZZZZZZ") REPORT "Expected Z FOR T_Idata" SEVERITY error;

assert(T_Odata="ZZZZZZZZ") REPORT "Expected Z FOR T_Odata" SEVERITY error;

wait;

END PROCESS;

END dataflow;此外,如何在一个进程中,以顺序的方式控制inout端口?

回答 1

Stack Overflow用户

回答已采纳

发布于 2015-11-30 20:24:47

T_IDATA和T_ODATA有多个驱动程序。这些信号由测试台和数据库驱动。最终结果由std_logic的分辨率函数决定。在最后一种情况下(不起作用),testbench本身驱动T_IDATA和T_ODATA降低。

让我们看一看起作用的情况:(从原始testbench获取的示例,这个例子在更新的testbench中被破坏了,因为信号T_ODATA没有初始化。)

T_Idata<="00001111";

T_ODATA<="ZZZZZZZZ";

T_Ctrl<='0';

WAIT FOR 10 ns;

assert(T_Odata="00001111") REPORT "Expected 00001111" SEVERITY error;这里,testbench驱动T_ODATA <= "ZZZZZZZZ"和数据缓冲区T_ODATA <= "00001111"。这被解析为"00001111",因此断言是满意的。

现在不起作用的情况是:

T_IData<="00000000";

T_OData<="00000000";

T_Ctrl<='Z';

WAIT FOR 10 ns;

assert(T_Idata="ZZZZZZZZ") REPORT "Expected Z FOR T_Idata" SEVERITY error;

assert(T_Odata="ZZZZZZZZ") REPORT "Expected Z FOR T_Odata" SEVERITY error;这里,testbench驱动T_ODATA <= "00000000"和数据缓冲区T_ODATA <= "ZZZZZZZZ"。这被解析为"00000000",因此断言失败。T_IDATA也是如此。

编辑:在这个不工作的情况下,testbench也应该驱动

T_IData<="ZZZZZZZZ";

T_OData<="ZZZZZZZZ"; 得到预期的结果。

编辑2:这些行必须添加到更新的testbench中,否则以前来自testbench的分配将用于解析。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/34006881

复制相关文章

相似问题