ASIC合成时序分析报告

在获取预定位方面存在一些问题&用于ASIC综合的路由时序分析报告

为了获得定时,我们应该在流动的步骤中使用ABC:

将当前网络转换为AIG(具有两个逻辑门的图和/或)

*结构散列是一种纯粹的组合变换

2--我不知道这个命令是做什么的。所以第一个问题是:这个命令是做什么的?

2.1当我使用这个命令时,我会得到一些错误:

如果我使用组合电路类

module combinational(a, b, sel, out);

input a, b;

input sel;

output out;

reg out;

always @ (a or b or sel)

begin

if (sel) out = a;

else out = b;

end

endmodule错误:网络是组合的(运行"fraig“或"fraig_sweep").

来自yosys synth.log输出:

2.1.1. Executing ABC.

Running ABC command: <yosys-exe-dir>/berkeley-abc -s -f <abc-temp-dir>/abc.script 2>&1

ABC: ABC command line: "source <abc-temp-dir>/abc.script".

ABC:

ABC: + read_blif <abc-temp-dir>/input.blif

ABC: + read_lib -w /usr/local/share/qflow/tech/osu035/osu035_stdcells.lib

ABC: Parsing finished successfully. Parsing time = 0.00 sec

ABC: Scl_LibertyReadGenlib() skipped sequential cell "DFFNEGX1".

ABC: Scl_LibertyReadGenlib() skipped sequential cell "DFFPOSX1".

ABC: Scl_LibertyReadGenlib() skipped sequential cell "DFFSR".

ABC: Scl_LibertyReadGenlib() skipped sequential cell "LATCH".

ABC: Scl_LibertyReadGenlib() skipped three-state cell "PADINOUT".

ABC: Scl_LibertyReadGenlib() skipped three-state cell "TBUFX1".

ABC: Scl_LibertyReadGenlib() skipped three-state cell "TBUFX2".

ABC: Scl_LibertyReadGenlib() skipped cell "PADFC" without logic function.

ABC: Scl_LibertyReadGenlib() skipped cell "PADNC" without logic function.

ABC: Scl_LibertyReadGenlib() skipped cell "PADVDD" without logic function.

ABC: Scl_LibertyReadGenlib() skipped cell "PADGND" without logic function.

ABC: Library "osu035_stdcells" from "/usr/local/share/qflow/tech/osu035/osu035_stdcells.lib" has 28 cells (11 skipped: 4 seq; 3 tri-state; 4 no func). Time = 0.01 sec

ABC: Memory = 0.38 MB. Time = 0.01 sec

ABC: Warning: Detected 2 multi-output gates (for example, "FAX1").

ABC: + strash

ABC: + scorr

ABC: Error: The network is combinational (run "fraig" or "fraig_sweep").

ABC: + ifraig

ABC: + retime

ABC: + strash

ABC: + dch -f

ABC: + map

ABC: + write_blif <abc-temp-dir>/output.blif

12.1.2. Re-integrating ABC results.

ABC RESULTS: INVX1 cells: 1

ABC RESULTS: NAND2X1 cells: 3

ABC RESULTS: internal signals: 0

ABC RESULTS: input signals: 3

ABC RESULTS: output signals: 1

Removing temp directory.如果我给出顺序

module sequential(a, b, sel,

clk, out);

input a, b;

input sel, clk;

output out;

reg out;

always @ (posedge clk)

begin

if (sel) out <= a;

else out <= b;

end

endmodule而且我们也有同样的错误

for this module:

module blocking(in, clk, out);

input in, clk;

output out;

reg q1, q2, out;

always @ (posedge clk)

begin

q1 = in;

q2 = q1;

out = q2;

end

endmodule伊格特

12. Executing ABC pass (technology mapping using ABC).

12.1. Extracting gate netlist of module `\blocking' to `<abctempdir>/input.blif'..

Extracted 0 gates and 0 wires to a netlist network with 0 inputs and 0 outputs.

Don't call ABC as there is nothing to map.

Removing temp directory.从错误中我们知道我们应该运行"fraig“或"fraig_sweep”

3.1 fraig-

将当前网络转换为功能缩减的AIG

fraig_sweep检测逻辑网络中功能等效的节点。与fraig不同,此命令保留了网络结构,只合并了功能上等效的节点。

4-ifraig,我不知道它做什么,也不知道这个命令是做什么的?

5-在retime /map命令中,您在{d}中的意思是

in

**

> for liberty with constr: strash; scorr; ifraig; retime {D};

> strash; dch -f; map {D}; buffer;

upsize {D}; dnsize {D}; stime p**

在dch -f中,我们应该给它一个脚本文件*,dch命令应该做什么?

及其地图绘制失败的原因?

**

*总之,我们如何获得和打印一份预置和路由时间分析报告?

它是否适用于所有电路--并行的,顺序的,...or --它不是在所有verilog文件中都能工作吗?

我想知道ABC的每一步应该做什么?

**

回答 1

Stack Overflow用户

发布于 2016-03-06 10:11:06

根据您的问题,您使用了以下模块:

module blocking(in, clk, out);

input in, clk;

output out;

reg q1, q2, out;

always @ (posedge clk)

begin

q1 = in;

q2 = q1;

out = q2;

end

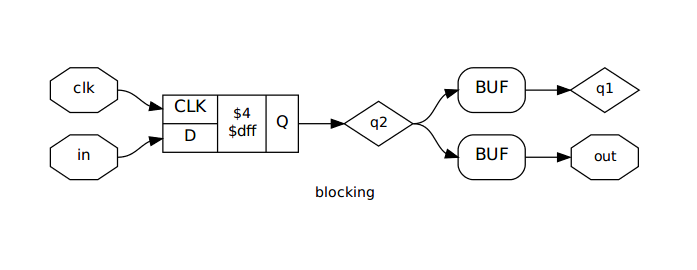

endmodule除了该模块引入了模拟竞赛条件(请参阅本论文,您的代码与“示例5-糟糕的阻塞分配顺序编码风格#1")基本相同之外,该模块只描述了一个D型触发器(用yosys -p 'proc; opt; show生成):

Yosys abc命令的默认行为是只考虑设计的逻辑部分(除非用-dff选项调用abc命令,请参阅Yosys中的help abc ),否则不会执行重计时。

因为这个模块中根本没有逻辑,而且abc命令对模块的逻辑部分起作用,所以您自然会得到:

Extracted 0 gates and 0 wires to a netlist network with 0 inputs and 0 outputs.

Don't call ABC as there is nothing to map.

Removing temp directory.关于消息Error: The network is combinational (run "fraig" or "fraig_sweep").:这只是scorr在处理纯粹组合的输入时生成的一个错误。(关于scorr -h所做的事情,请参阅yosys中的scorr -abc。它只对顺序输入网络是有意义的,因此当abc不被-dff调用时,它是不运行的。)Abc简单地继续使用下一个命令,正如您在引用的输出中看到的那样。这里没什么不对的。

总之,如何获取和打印一个预置&路由时间分析报告,为ASIC?

通过使用延迟目标abc和-constr <file>文件调用-liberty <file>,同时将其映射到带有-liberty <file>的ASIC库。

还是它不适用于所有verilog文件?

正如你所看到的,它不工作在没有逻辑的电路上,因为这样就没有什么可以映射和分析的了。

https://stackoverflow.com/questions/35820432

复制相似问题