水平敏感的SR孵化行为

水平敏感的SR孵化行为

提问于 2016-05-12 18:07:15

回答 1

Stack Overflow用户

回答已采纳

发布于 2016-05-25 03:37:31

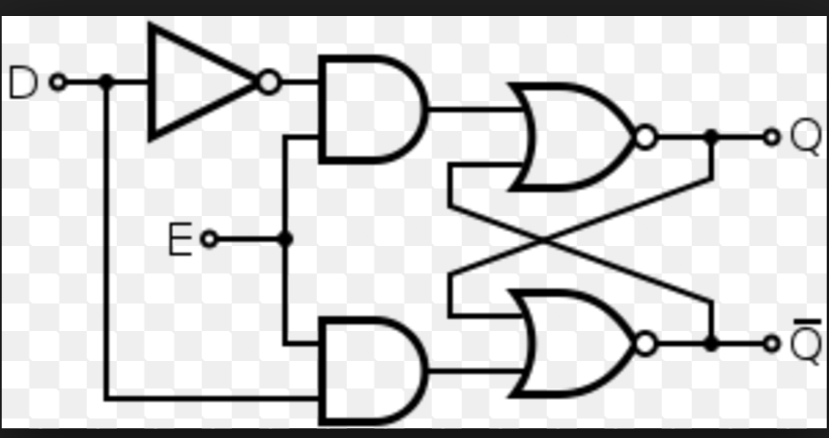

SR触发器的设计使得当S和R稳定时,C仅为1。它的设计非常仔细,以防止C在S=R=1时成为1。然而,考虑到触发器的基本图表,这一点并不明显。

对此的一个改进是D触发器。它从SR触发器中反演其中一个信号。这确保了S和R永远不会是相同的。这可以在下面的图片中看到。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/37194441

复制相关文章

相似问题