为什么L2缓存利用率低,即使L2缓存命中率约为93%?

为什么L2缓存利用率低,即使L2缓存命中率约为93%?

提问于 2019-07-21 16:47:08

我在用库达做实验。

我认为如果L2缓存命中率高,性能就会提高。

然而,从nvprof来看,L2缓存利用率很低,尽管L2缓存命中率约为93%。

为什么会发生这种事?有什么例子可以让它成为现实吗?

回答 2

Stack Overflow用户

回答已采纳

发布于 2019-07-21 17:16:51

它们是不同的东西。您可以不频繁地在L2缓存中查找数据,但是当您这样做时,发现L2几乎总是包含您要查找的数据。

事实上,这是一个很有可能结合在一起的组合,因为低利用率意味着有用的数据不太可能从缓存中被逐出。

Stack Overflow用户

发布于 2019-07-21 20:42:24

L2利用率和命中率是正交概念。

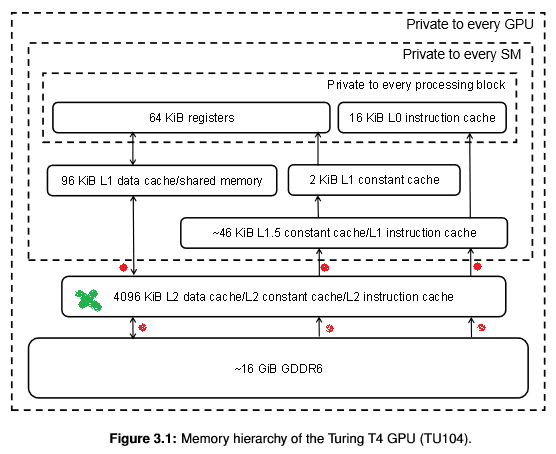

L2利用率%测量与其峰值性能相比,L2缓存执行了多少操作(读/写/原子)。您也可以将此视为“我使用了多少L2带宽”的代理,因为在给定的GPU上,L1和L2之间有固定的带宽。注意,此度量没有测量所使用的L2容量的%。(为了简化,在下图中,把它看作是测量红点旁边箭头的吞吐量)

L2缓存命中率测量当L1丢失时,它在L2中被发现的频率。(在图中,请考虑绿色X上的L2缓存标记)

https://arxiv.org/pdf/1903.07486.pdf原始图表

假设:

- 一些CUDA内核可以读取每个SM一次的单个L1缓存线(128 B),这会导致一个总是命中的L2读取。L2利用率为0%,L2命中率为100%.

- 一个不同的CUDA内核可以实现~100%的L2利用率和100%的L2命中率,方法是执行大量的负载,这些负载要么是L1中的错误,要么是“缓存全局”负载中的访问地址集符合L2的大小。

- 然而,另一个CUDA内核可以实现高L2利用率和较低的L2命中率,方法是执行大量的负载,这些负载要么在L1中丢失,要么是分散在千兆字节大小的缓冲区中的“缓存全局”负载 (也就是说,这些负载并不都同时适合于L2)。

另请参阅

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/57135152

复制相关文章

相似问题