软硬件融合技术内幕 进阶篇 (11) —— 巨头的碰撞 (下)

软硬件融合技术内幕 进阶篇 (11) —— 巨头的碰撞 (下)

在前几期,我们了解了,对于SmartNIC的实现,无论是ASIC,FPGA,NPU还是SoC方案,都有一些难以绕过的障碍,因此,NVidia收购了Mellanox后,规划了基于ASIC+NPU+SoC的方案来取长补短,也就是基于Bluefield的DPU (Datapath Process Unit)。

在计算机领域,另一家巨头——Intel,也提出了所谓的IPU概念,也就是Infrastructure Process Unit。

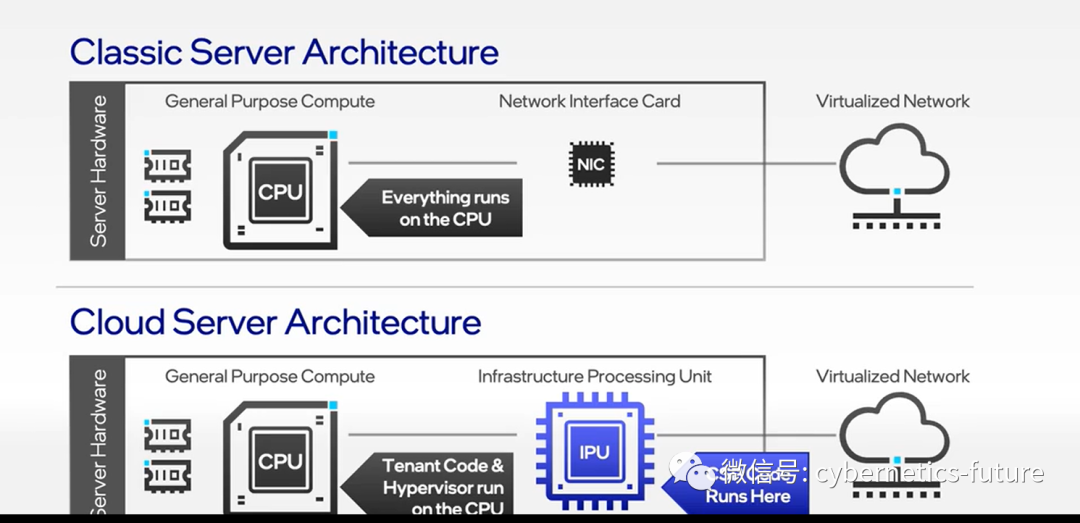

Intel认为,在传统IT架构中,所有的运算都在CPU上进行,而云时代,由于从业务请求到CPU中的路径长度大大增加了,因此,应当由专用的处理器 (Dedicated Processor)来处理基础架构(Infrastructure)相关的运算。这就是其IPU的设计思路。

Intel IPU的设计,实质上是其基于软硬件融合的高性能数据平面开发套件DPDK和SPDK的延续。我们在《软硬件融合技术内幕 进阶篇 (4) ——云计算的六次危机(中)》提到过,DPDK和SPDK实质上是利用几个专用的CPU核,来处理各虚拟机使用的虚拟化网络设备和虚拟化存储设备的工作请求。而IPU的出现,实质上就是利用专用的硬件来取代这些专用CPU核。

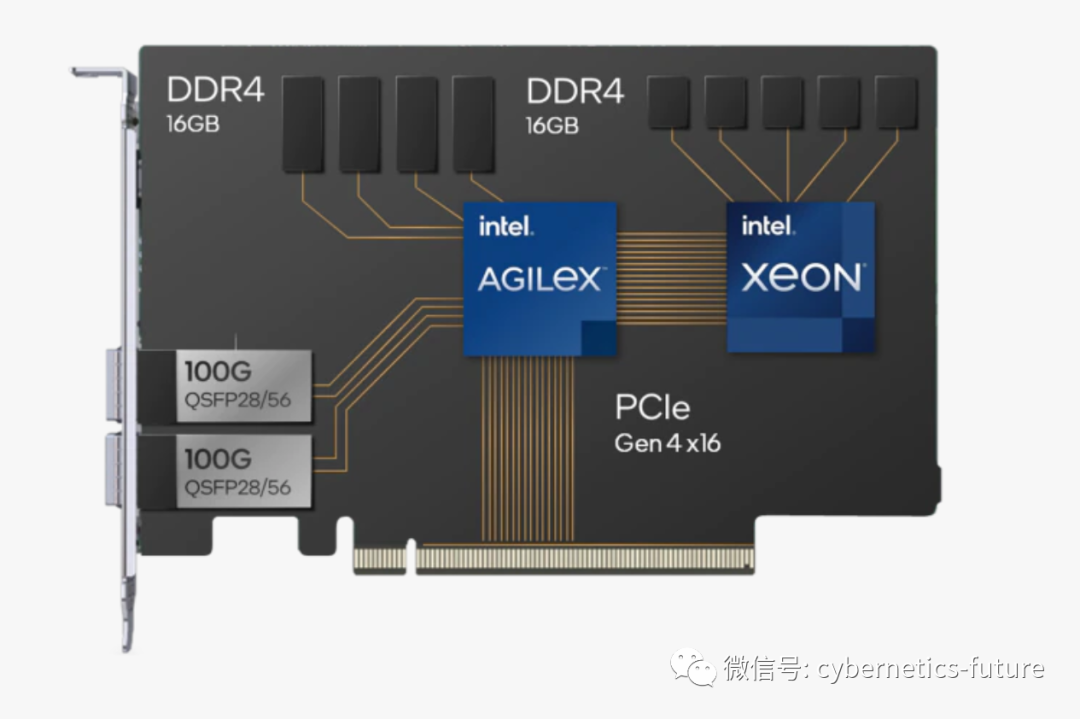

Intel c6000x产品公开的资料的一张图,体现了Intel的这一实现思路:

图中可以看出,C6000X IPU上有2个关键芯片:

Intel Agilex FPGA;Intel Xeon CPU;

Agilex FPGA通过16通道宽的PCI-E 4.0接口连接到服务器,同时提供2个QSFP28/QSFP56的100G 以太网接口。同时,FPGA挂了16GB的DDR4 DRAM;

FPGA 与Intel Xeon处理器之间通过某种特殊总线(CXL)互联,Xeon上也挂载了16GB的DDR4 DRAM。

这样的设计思想实际上是让FPGA来执行数据平面的绝大多数功能,也就是实现所谓的Fast-Path。当FPGA搞不定的时候,再转到Slow-path,也就是让Xeon处理器来指导FPGA如何做。

长期关注本公众号的同学可能会意识到,这和网络路由器的设计有类似的地方。无论是基于NP,多核SoC还是FPGA转发平面的路由器,其转发平面都只是做快速路径 (Fast-Path)的处理,而将慢速路径交给CPU处理。Intel的SmartNIC也采用了这样的设计思维。

那么,Intel使用的这颗FPGA可以实现Fast-Path的哪些功能呢?

让我们回到设计SmartNIC的初衷——解放SPDK和DPDK使用的CPU资源。熟悉虚拟化的同学很容易想到,DPDK实质上实现的是VirtIO-net的后端驱动及vSwitch,而SPDK实质上实现的是VirtIO-blk的后端驱动。

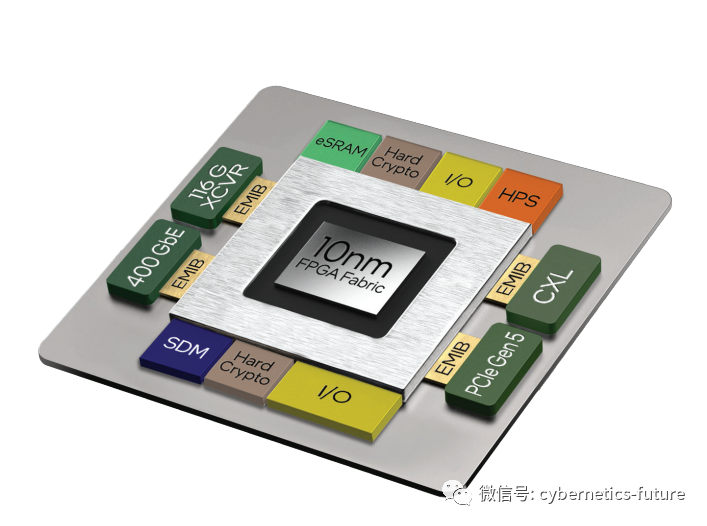

Intel这颗FPGA能够提供12对PAM4 57.8Gbps的Serdes通道,也就是理论上最多可以提供600Gbps的吞吐。FPGA内部集成了400G/200G/100G以太网的MAC,工程师们不需要购买额外的以太网相关的IP。

特别地,在FPGA内部还集成了硬件加密算法运算单元,也就是说,https的卸载可以在FPGA上完成。由于云计算系统的信任根实际上是宿主机本身,因此,SmartNIC作为明文和密文的安全边界,是非常合适的一种设计。

在这颗FPGA上,还提供了一个很好玩的东西:CXL。

CXL是Compute Express Link的缩写,于2019年由CISCO,Dell-EMC,HPE,Intel等巨头创立。它本是基于PCI-E 5.0标准上的一个远端内存互访协议,使得CPU与CPU,或CPU与其他设备之间可以通过PCI-E协议互相访问对方挂载的DRAM。——那么,这和RDMA有什么区别呢?

原来,RDMA所依托的传输方式,有IB (Infiniband)和以太网两种方式。IB和以太网目前的带宽上限是400Gbps,而PCI-E 5.0理论上可支持32个Lane,每个Lane吞吐可达32Gbps,总计可达1Tbps。当然,PCI-E 5.0的传输距离远小于以太网或IB,只能在机箱内部互联。如何让CXL能够实现更大规模的互联,构建跨CPU甚至跨host主机的memory pool, 这是后话。

在SmartNIC上,CXL的作用是让FPGA和CPU能够共享对方的内存,同时实现写入的强一致性,让两颗主芯片能够非常容易地交换数据,而不需要通过发送/接收的复杂软件流程。

基于这些黑科技的加持,Intel期望自己的SmartNIC能够让云计算的车轮更快地飞驰。

那么,各大云计算厂商,采用的是哪种方案呢?

这个问题我们留到下期和大家分享。