AI时代的PCIe技术革新:Retimer、iRedriver与Switch如何重塑数据中心架构

AI时代的PCIe技术革新:Retimer、iRedriver与Switch如何重塑数据中心架构

光芯

发布于 2025-12-25 14:52:36

发布于 2025-12-25 14:52:36

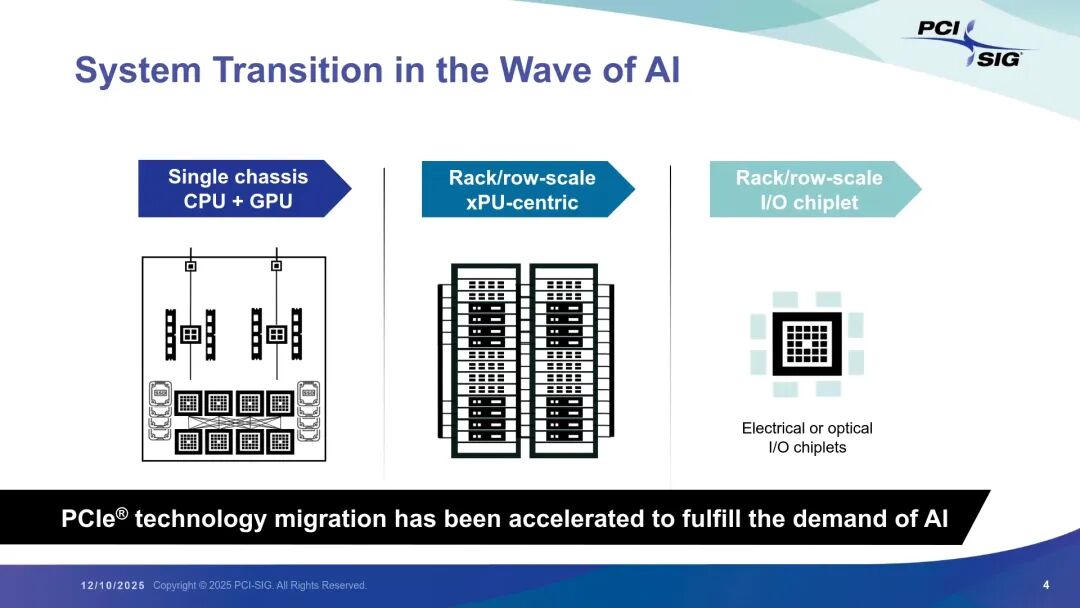

在人工智能浪潮的推动下,数据中心架构正经历从单机箱CPU+GPU模式向机架/行级XPU中心化、IO小芯片化的深刻转型。PCIe(PCI Express)技术作为连接计算、存储、网络资源的核心协议,为满足AI场景对高带宽、低延迟、复杂拓扑的需求,加速了代际迭代与功能升级。Retimer(重定时器)、iRedriver(智能重驱动器)与Switch(交换机)作为PCIe生态的关键器件,不仅解决了高速传输中的信号完整性、传输距离等核心挑战,更成为支撑AI规模化部署的“基石”。本文将基于PCI-SIG 2025年技术研讨会核心内容,深入解析PCIe技术演进、三类关键器件的技术特性与差异、应用场景及未来趋势,还原AI时代PCIe架构革新的完整图景。

一、PCIe技术:AI时代的数据中心连接基石 1. 技术演进与核心优势

PCIe协议自诞生以来已走过20余年历程,凭借三大核心优势成为行业最普及的开放标准:一是成熟且普及的生态系统,工具、IP、测试设备一应俱全, 互操作性与合规性经过长期验证;二是完备的前后向兼容性,PCI-SIG的合规测试确保新老设备无缝对接;三是高速低延迟与可扩展带宽,通过速率提升与端口分叉(bifurcation)配置,满足不同场景的性能需求。

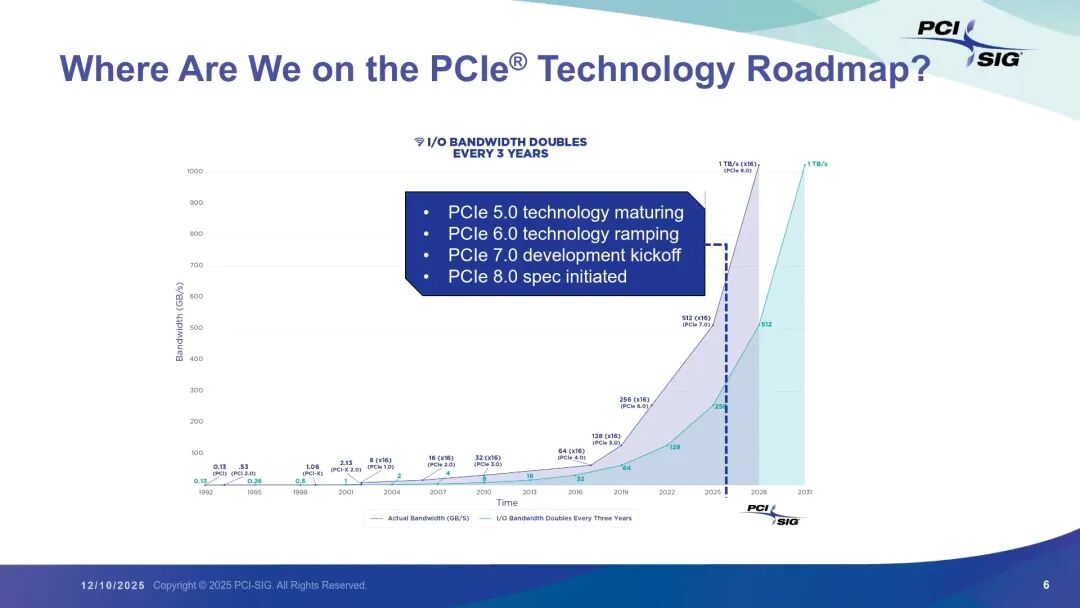

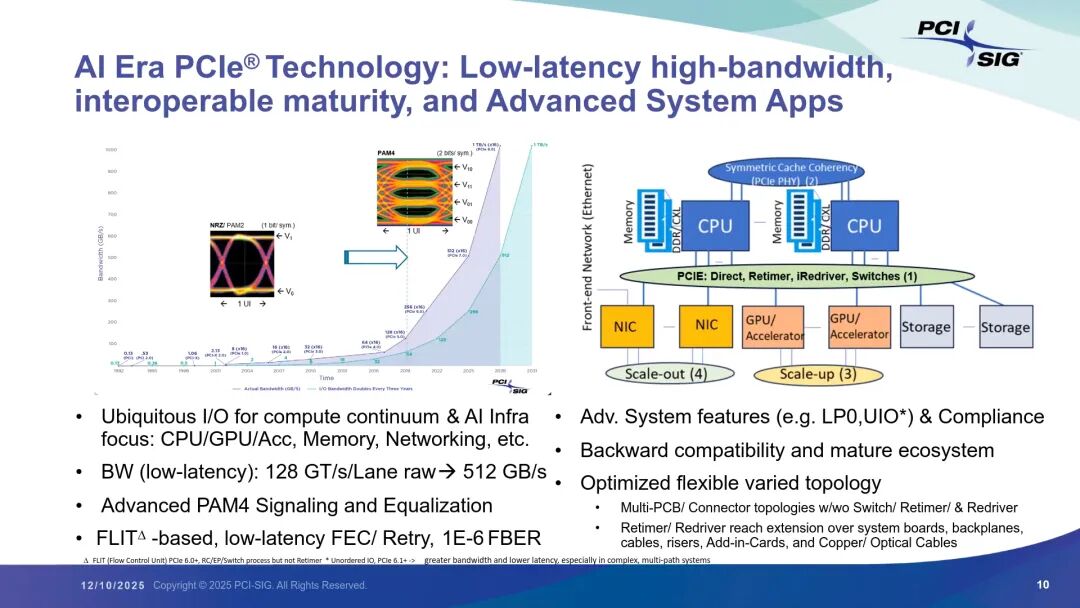

从技术路线图来看,PCIe带宽每三年翻倍的节奏持续兑现:2025年末,PCIe 5.0技术已走向成熟,PCIe 6.0进入规模化部署阶段,PCIe 7.0规范正式定稿(芯片与测试设备研发同步推进),而PCIe 8.0的预研工作已启动。其中,PCIe 7.0实现了128 GT/s每通道的原始速率,x16链路带宽可达512 GB/s,核心技术突破源于PAM4调制与FLIT(Flow Control Unit)编码,配合低延迟前向纠错(FEC)与重试机制,实现了1E-6的误码率(FBER),满足AI场景的高可靠性要求。

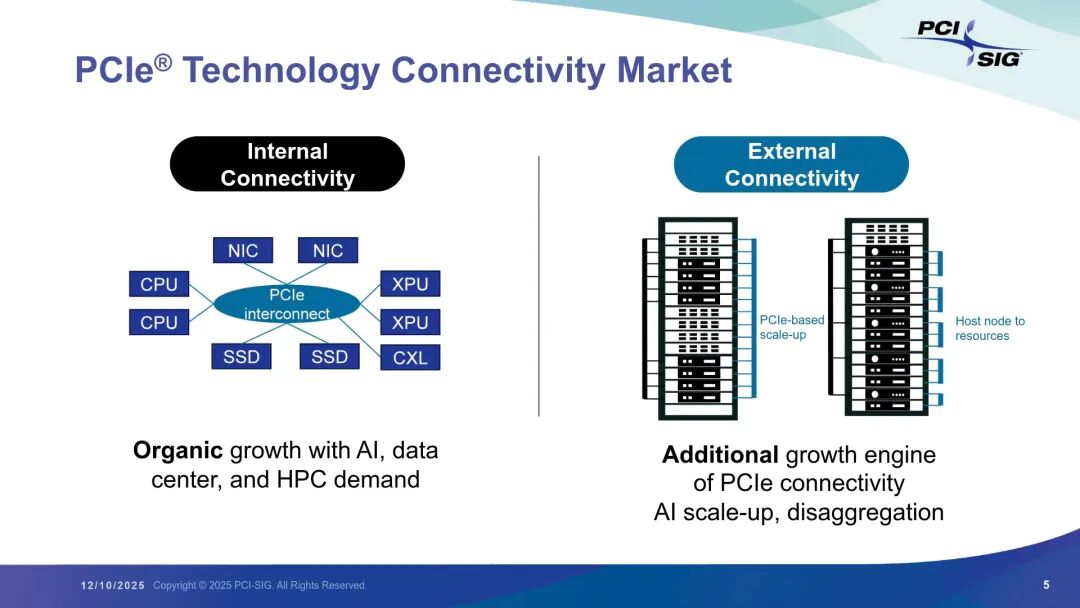

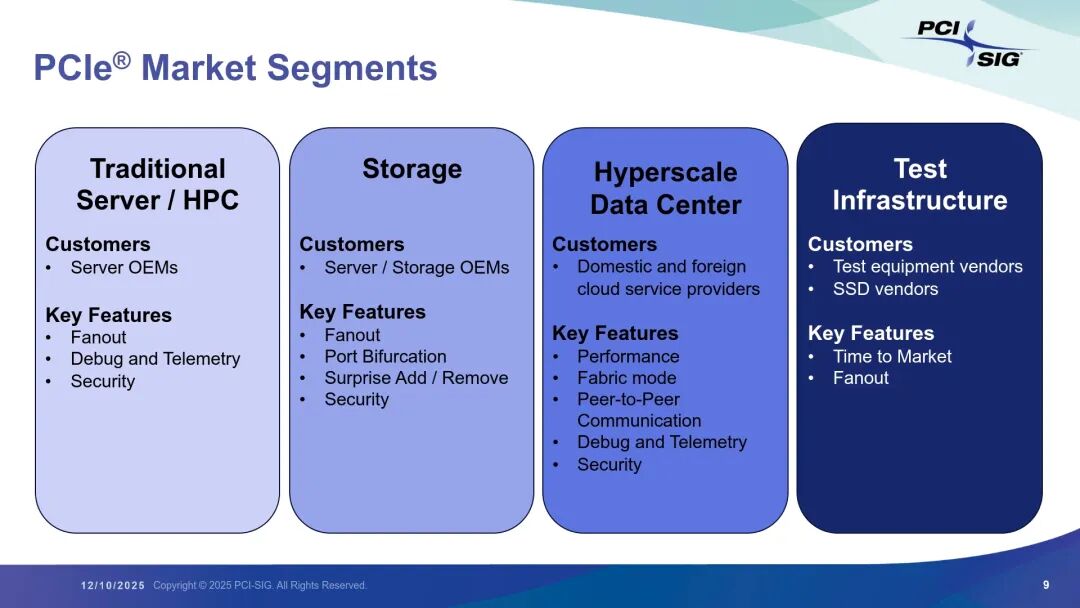

2. 市场应用与需求驱动 PCIe的连接能力覆盖数据中心内部与外部场景:内部连接CPU、XPU、SSD、内存及网卡,支撑单机架资源协同;外部则面向机架间互联与AI架构解耦,成为规模化部署的关键增长引擎。其市场细分场景呈现鲜明需求差异:

- 传统服务器/HPC:核心需求包括热插拔(Surprise Add/Remove)、端口分叉与扇出(Fanout),由服务器OEM主导功能定义; - 存储领域:聚焦NVMe存储支持、端到端通信(Peer-to-Peer)、安全与诊断能力,服务器与存储OEM共同推动技术迭代; - 超大规模数据中心:由云服务提供商(CSP)主导,追求快速上市(Time to Market)、高带宽fabric、多主机支持等特性,节奏远超以往; - 测试基础设施:虽市场规模较小,但为PCIe合规测试提供核心支撑,是生态成熟的关键保障。

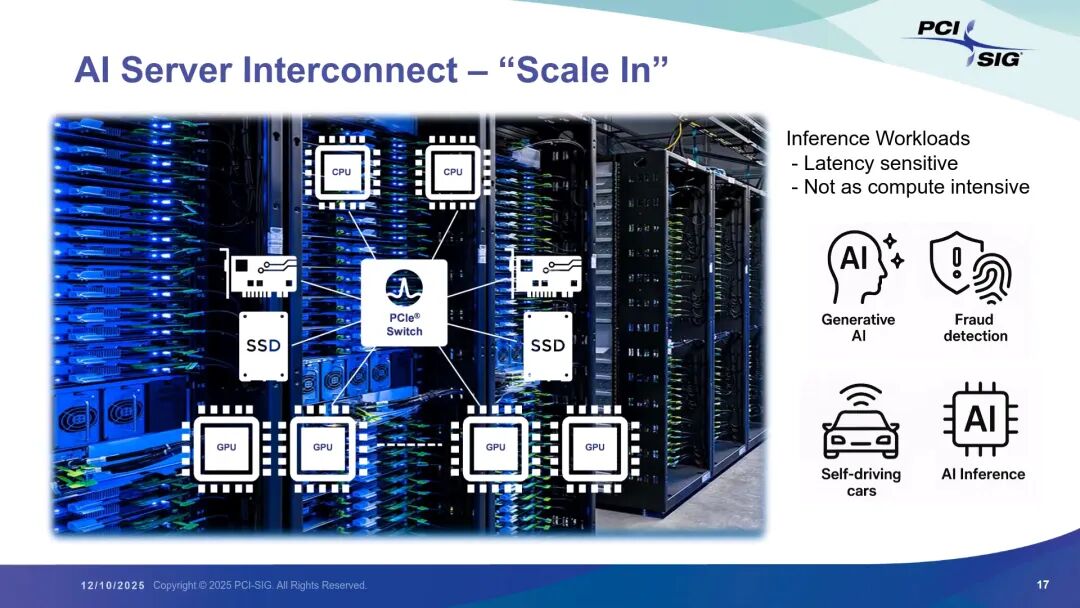

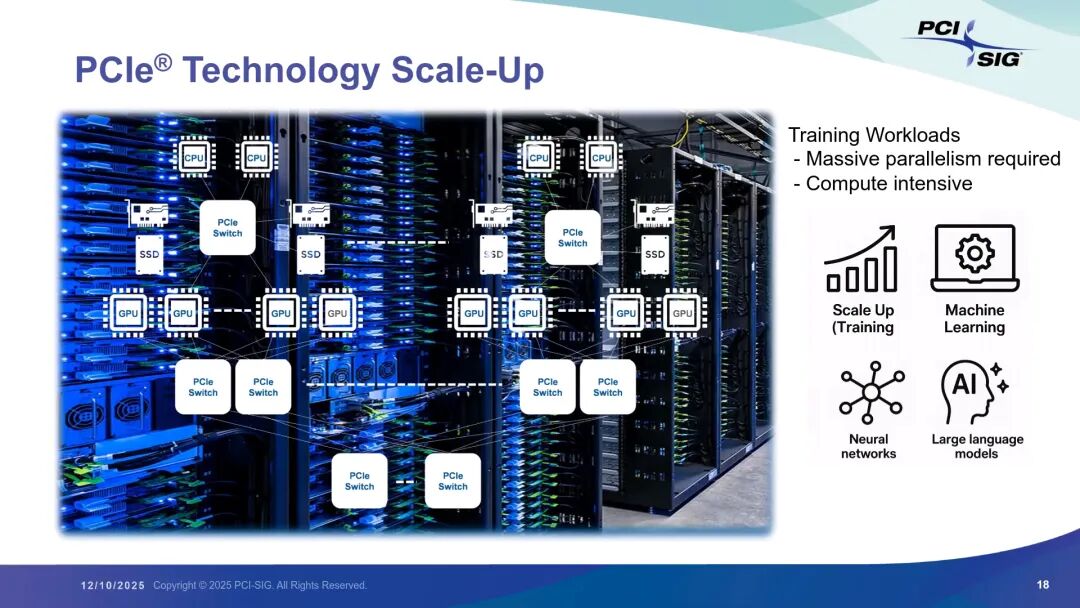

AI场景的爆发式增长成为PCIe技术演进的核心驱动力:无论是低延迟敏感的推理工作负载(如自动驾驶、欺诈检测),还是需大规模并行计算的训练工作负载(如大语言模型训练),都对PCIe的带宽、延迟、传输距离提出了更严苛的要求,也直接推动了Retimer、iRedriver与Switch的技术升级。

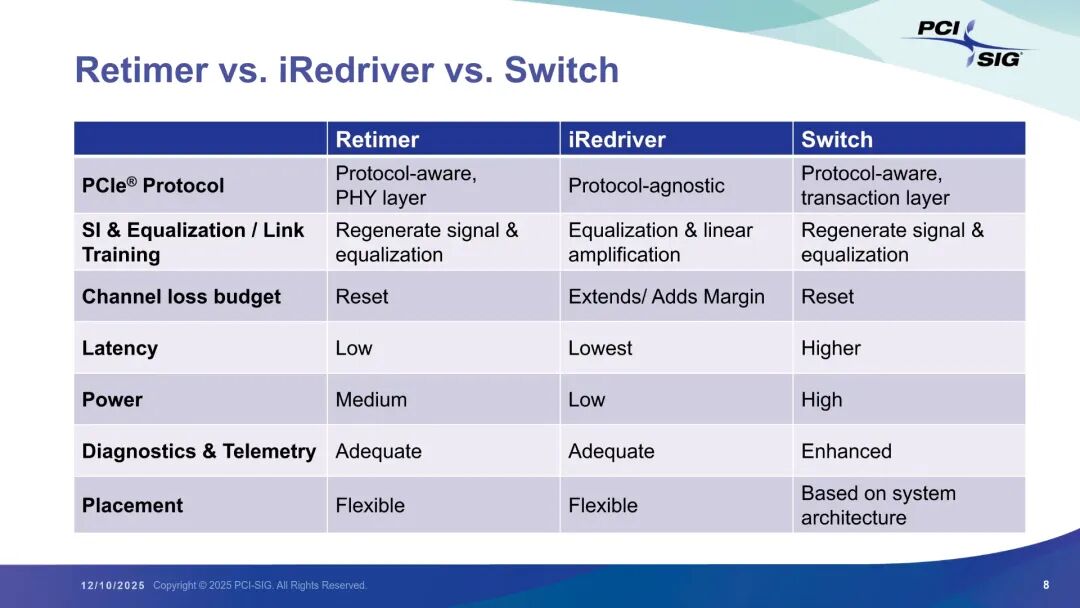

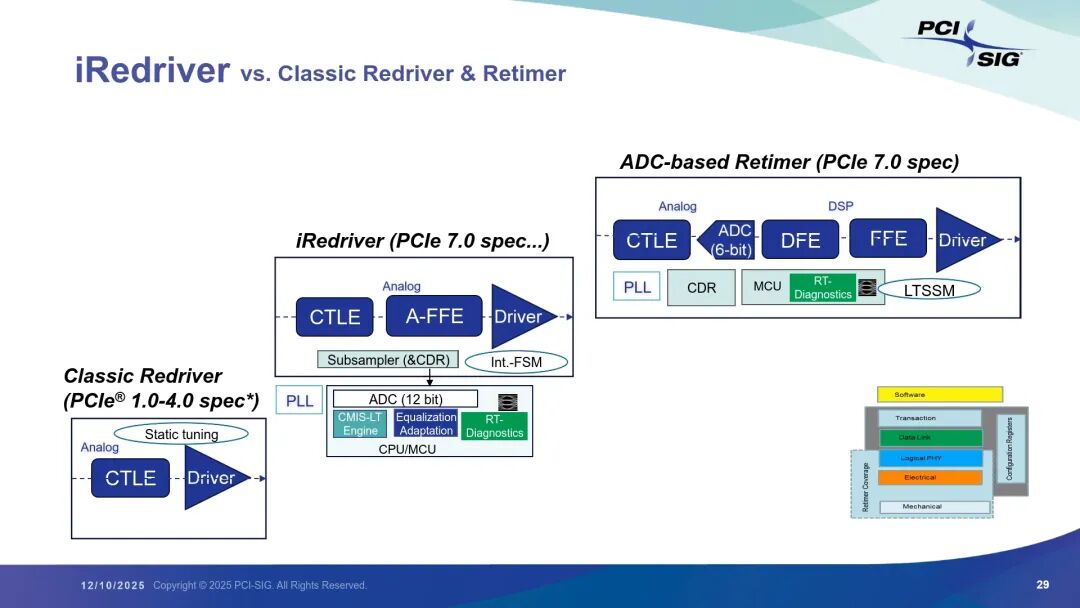

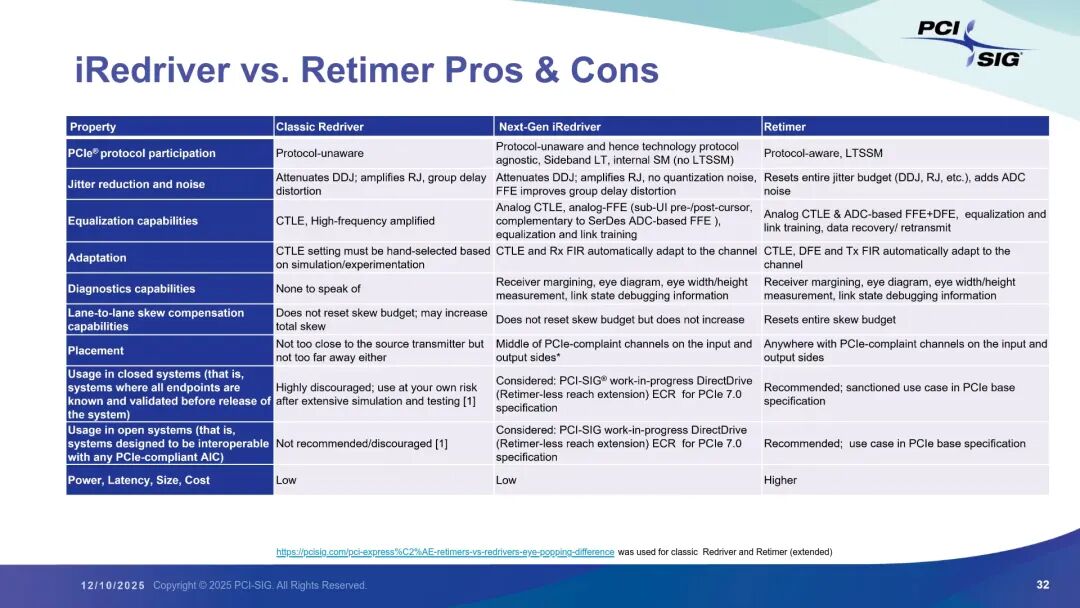

二、关键器件解析:Retimer、iRedriver与Switch的技术特性与演进 1. 三类器件核心差异与定位 PCIe生态的三类关键器件在协议支持、信号处理、性能表现等方面各有侧重,共同支撑不同场景的连接需求:

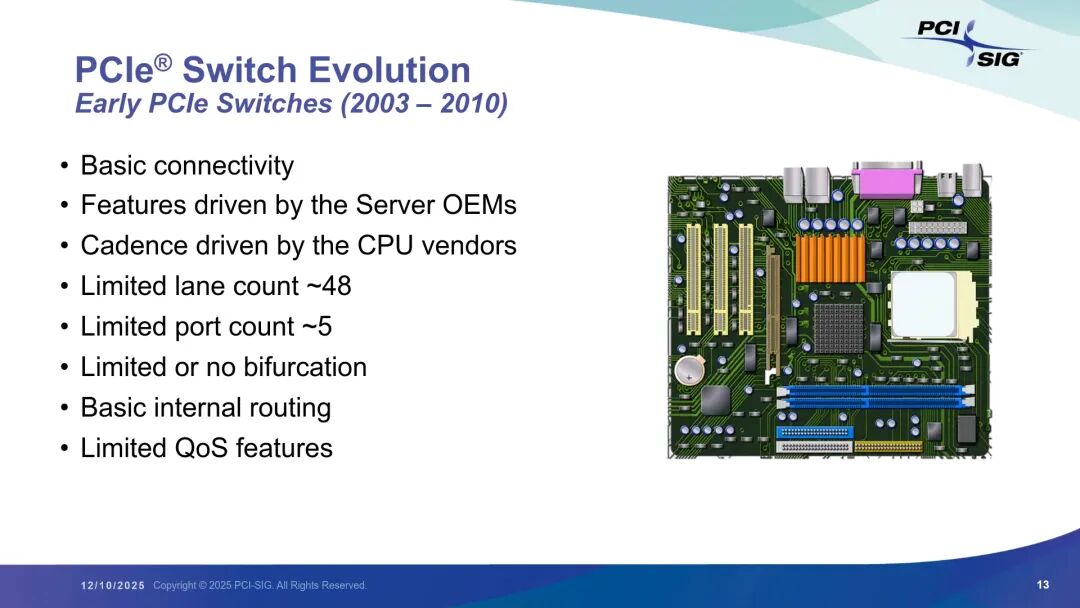

Retimer是协议感知型器件,工作于PHY层,核心能力是信号再生与均衡,可重置通道损耗预算,延迟处于低水平(通常10ns左右),功耗中等。其具备充足的诊断与遥测功能(如BER监控、电压/温度监测、LTSSM状态跟踪),部署位置灵活,适用于需要延长传输距离且对信号完整性要求高的场景,是PCIe 5.0及以上版本长距离传输的核心选择。 iRedriver是新一代智能重驱动器,属于协议无关器件,不参与PCIe协议交互,仅通过线性放大与均衡(CTLE+模拟FFE)扩展通道余量,延迟最低(亚纳秒级)且功耗极低。与传统Redriver的静态调优不同,iRedriver内置CDR(时钟数据恢复)、子采样器与12位ADC,支持自动链路训练与实时诊断(数字眼图监控、BER检测),可直接驱动光模块,部署灵活度高,尤其适合AI场景中对功耗、延迟、成本敏感的短距离传输需求。 Switch是协议感知型器件,工作于事务层,不仅能再生信号与均衡,还具备风扇输出、多主机互联、端到端通信等复杂功能。其诊断与遥测能力最强,但延迟较高、功耗最大,部署位置需结合系统架构设计,是构建大规模PCIe fabric、支撑多设备协同的核心器件。 2. Switch的演进历程:从基础连接到AI驱动 PCIe Switch的发展历程与数据中心需求变迁高度同步,可分为四个关键阶段: - 早期阶段(2003-2010):以基础连接为核心,由CPU厂商主导迭代节奏,lane数仅48左右,端口数约5个,无分叉能力,仅支持简单内部路由,QoS功能有限;

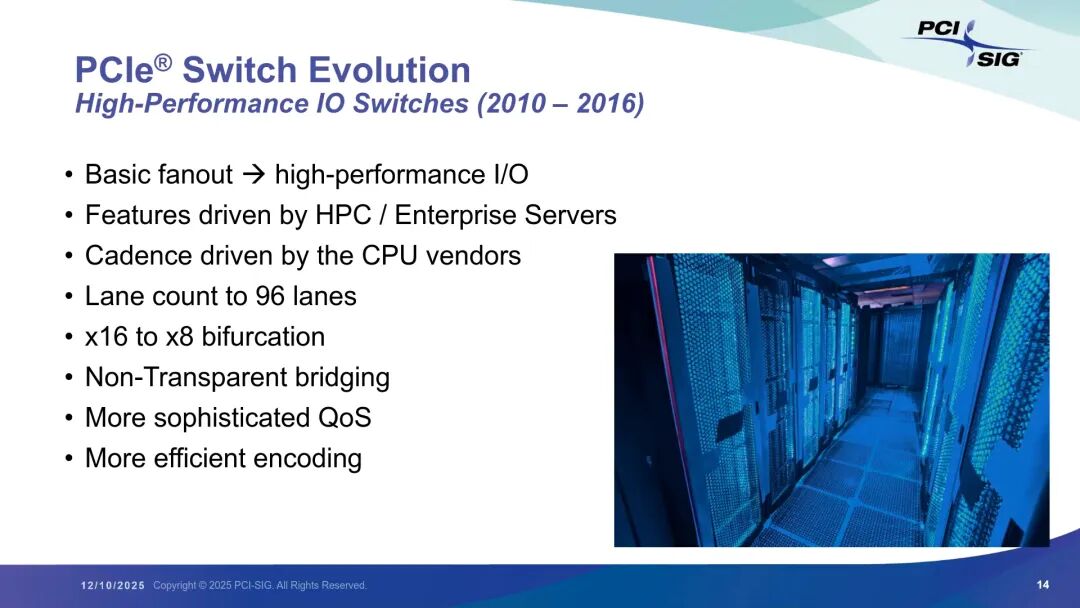

- 高性能IO阶段(2010-2016):受HPC与企业服务器需求驱动,lane数提升至96,支持x16到x8分叉,引入非透明桥接(Non-Transparent bridging)与更高效的128b/130b编码,QoS功能升级;

- 存储导向阶段(2016-2020):NVMe存储爆发推动技术迭代,lane数增至144,支持x16到x2分叉,可支撑大规模NVMe存储集群,热插拔与稳健的热添加/移除成为核心特性;

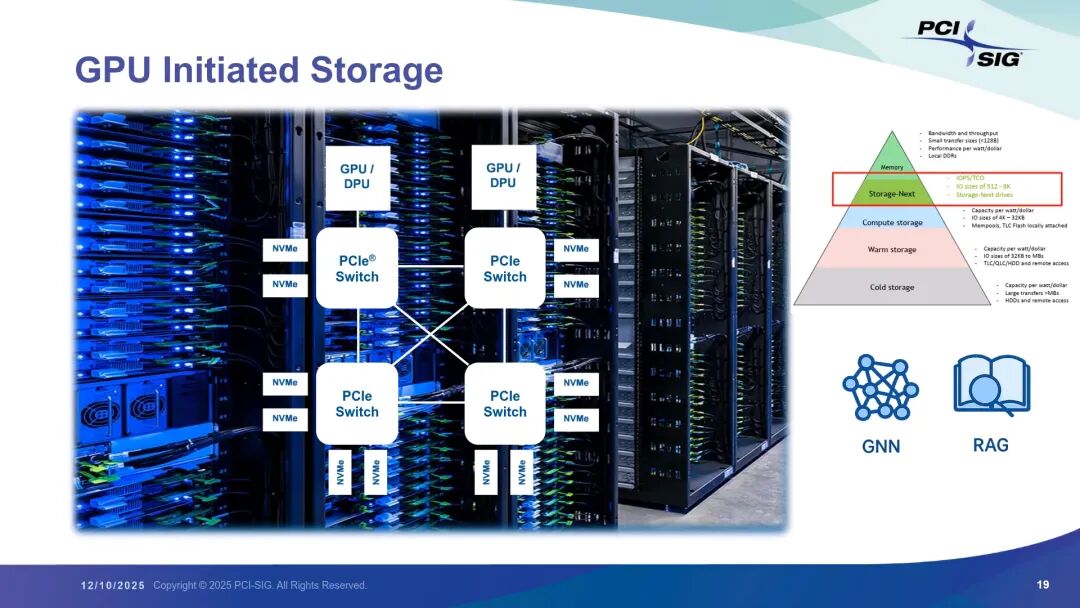

- AI驱动阶段(2020至今):由CSP主导节奏,lane数持续增加,支持高带宽fabric、多主机、端到端通信,引入PAM4调制与前向纠错,适配AI场景的大规模并行与低延迟需求,迭代节奏空前加快。 在现代AI基础设施中,Switch承担三大核心角色:一是Scale In互联,作为CPU、GPU、存储的连接枢纽,支撑低延迟推理工作负载;二是Scale Up互联,构建专用高速网络,满足训练工作负载的GPU间低延迟通信需求;三是存储优化,支撑“Storage Next”架构,让GPU直接发起存储访问,突破DDR/HBM容量限制,实现百万级IOPS。

3. Retimer:信号完整性与长距离传输的核心保障

随着PCIe速率从PCIe 1.0的2.5 GT/s提升至PCIe 7.0的128 GT/s,信号完整性与传输距离成为核心挑战。Retimer通过信号再生与均衡,将失真的高速信号重新整形为清洁信号,同时重置通道损耗预算,成为解决这一问题的关键。

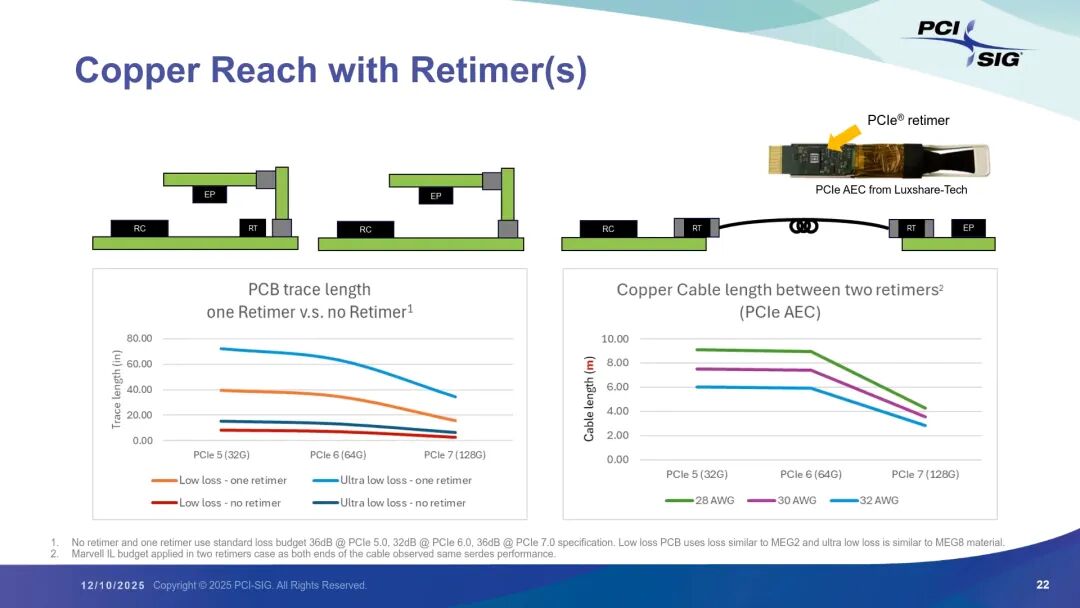

在传输距离扩展方面,Retimer的作用尤为显著:PCIe 7.0在低损耗PCB上无Retimer时,传输距离不足10英寸,而加入1个Retimer后可延长至20英寸;若采用超低损耗PCB,传输距离可进一步扩展至35英寸。在外部连接场景,Retimer集成于线缆连接器形成PCIe AEC(Active Electrical Cable),PCIe 5.0/6.0下可实现6-8米铜缆传输,PCIe 7.0下也能达到3-4.5米。

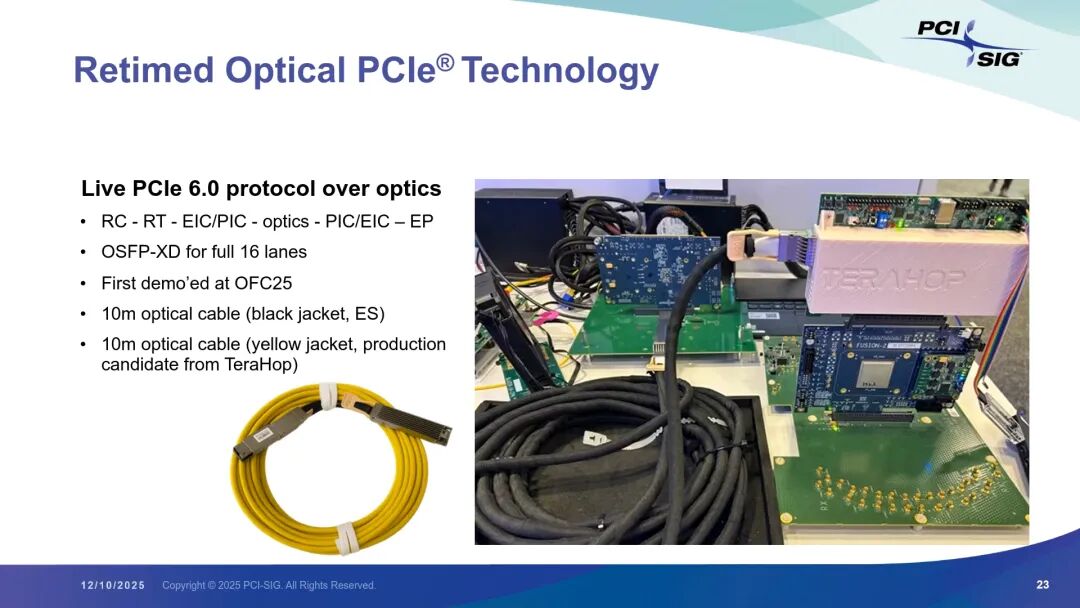

在光传输领域,Marvel在OFC 2025上演示了全球首个PCIe 6.0光链路方案,通过1个Retimer配合10米光缆,实现16 lane、64 GT/s的协议传输,验证了PCIe跨机架光互联的可行性。

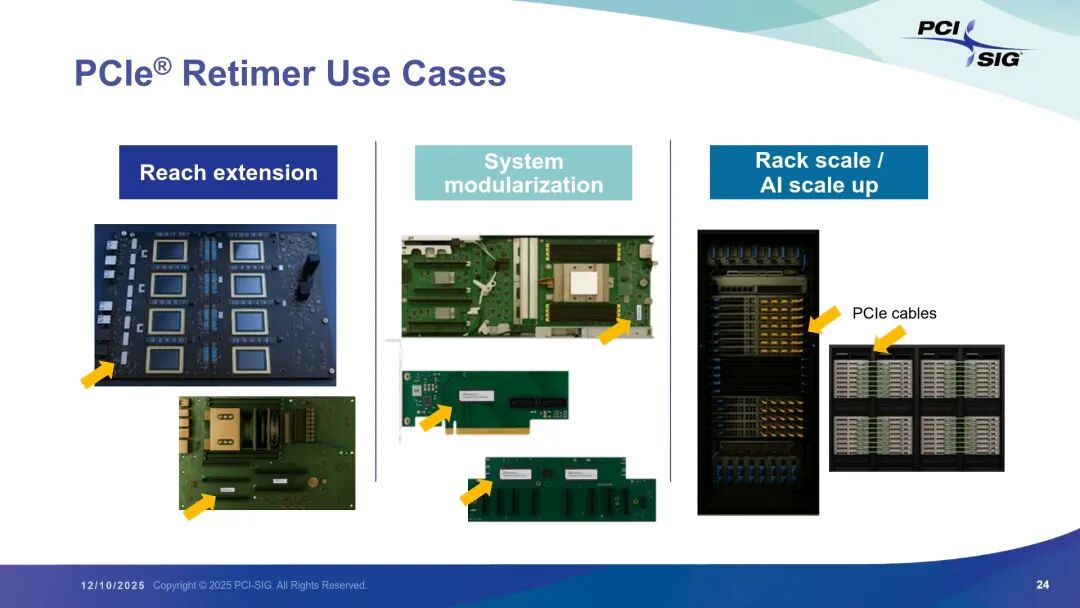

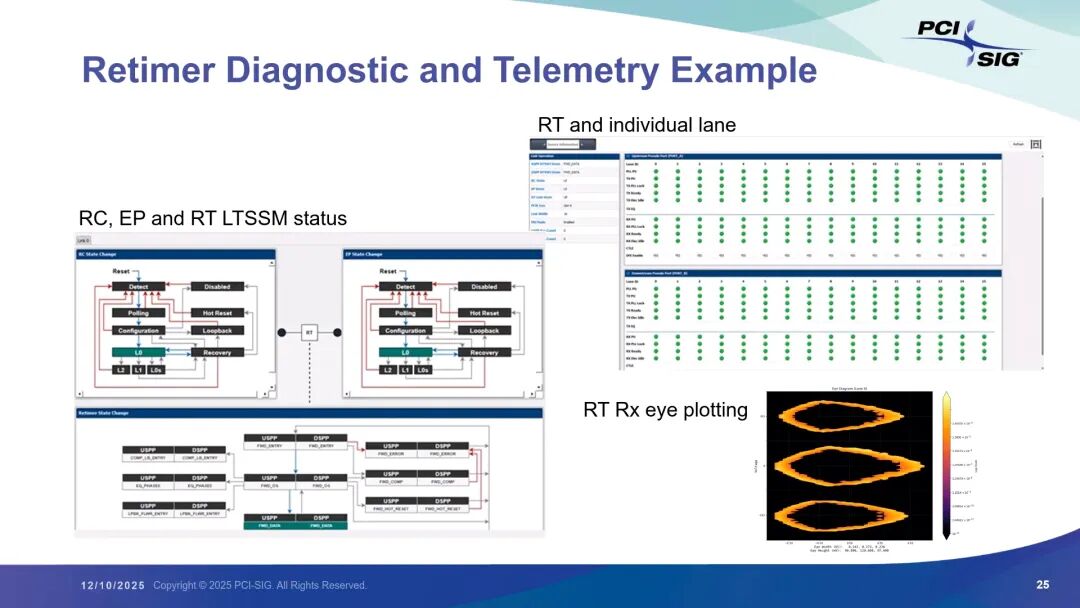

Retimer的应用场景覆盖AI服务器、机架级系统与解耦架构:在GPU基板上,每个GPU配置1个Retimer,优化CPU到GPU的信号传输;在主板上,Retimer靠近PCIe插槽部署,提升扩展卡的信号质量;在背板与线缆中,Retimer则成为延长传输距离、保障信号完整性的核心器件。此外,Retimer还具备丰富的诊断与遥测能力,可监控LTSSM状态、绘制接收端眼图、跟踪单通道状态,为系统维护提供关键数据。

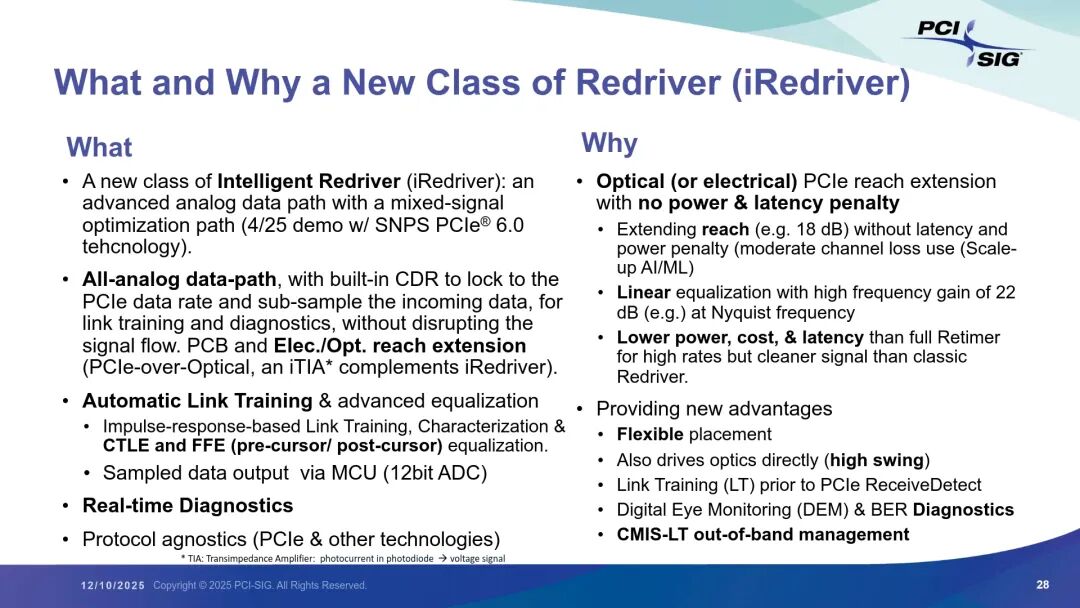

4. iRedriver:AI时代的低功耗低延迟连接新选择

PCIe 7.0及以上版本对功耗与延迟的极致追求,催生了iRedriver这一新器件品类。与传统Redriver的静态调优不同,iRedriver采用全模拟数据路径,集成CTLE、模拟FFE(子UI预/后抽头)与CDR,可自动适配通道特性,无需手动配置;通过12位ADC与MCU实现子采样,支持实时诊断与数字眼图监控,且不干扰PCIe数据传输。

iRedriver的核心优势在于“低功耗、低延迟、低成本”:功耗仅为传统Retimer的一小部分(亚瓦级 vs 10瓦级),延迟低至亚纳秒级(远低于Retimer的10ns+),尺寸与成本也更具优势。同时,其协议无关特性使其不仅适用于PCIe,还可支持其他高速协议,部署灵活性极高。

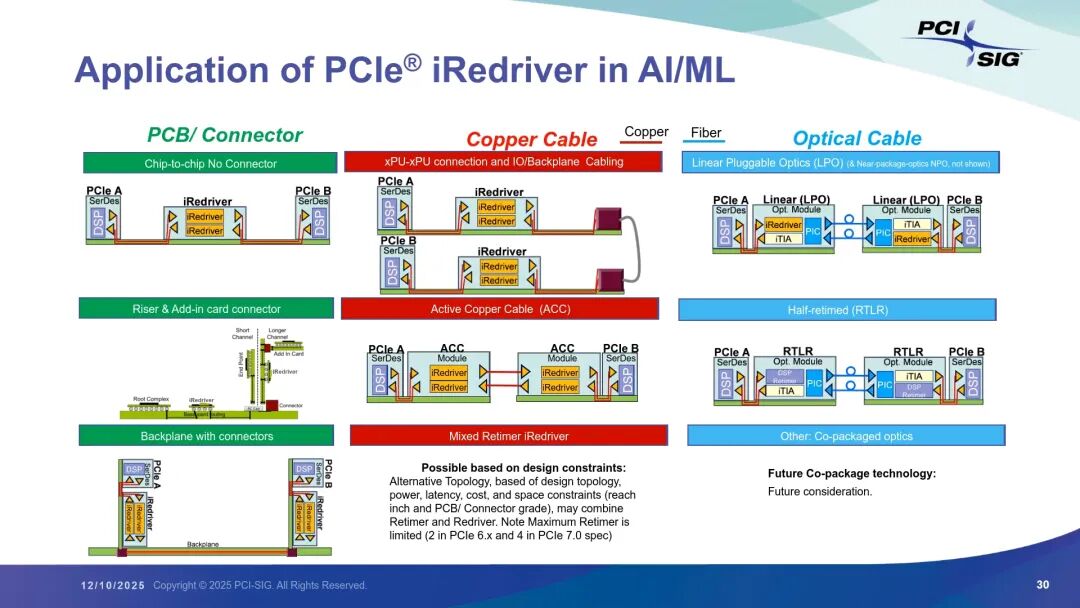

在AI基础设施中,iRedriver的应用场景包括:芯片间互联(当PCB长度超过PCIe 7.0最大距离时,提供50%链路余量提升)、背板与扩展卡连接(多连接器场景下优化链路预算)、XPU间铜缆互联(配合DAC线缆实现低延迟连接)、光模块驱动(与iTIA配合,支撑光链路的链路训练与诊断)。值得注意的是,PCI-SIG正在推进DirectDrive ECR规范,旨在实现无Retimer的长距离传输,而iRedriver正是这一规范的核心支撑器件。 三、技术挑战与解决方案:信号完整性与硅片的双重优化 PCIe速率的持续提升,需要信号完整性与硅片技术的协同突破:

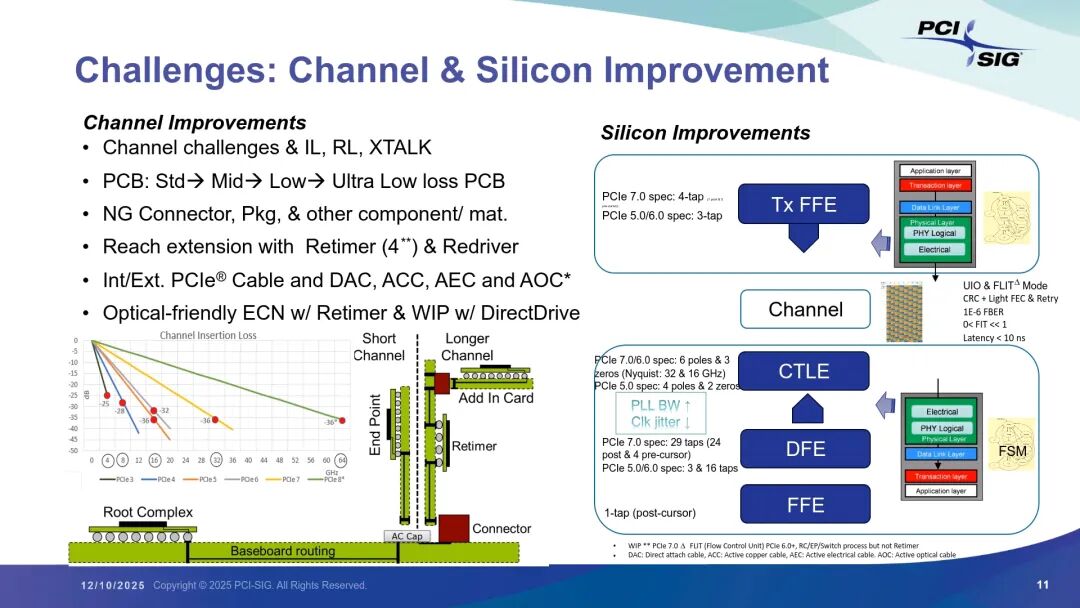

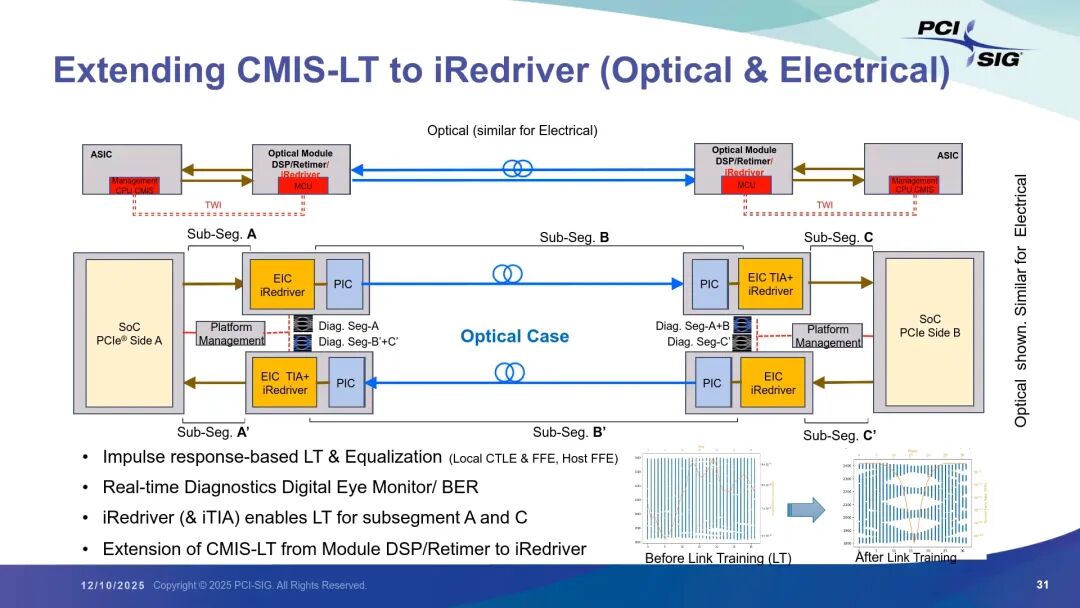

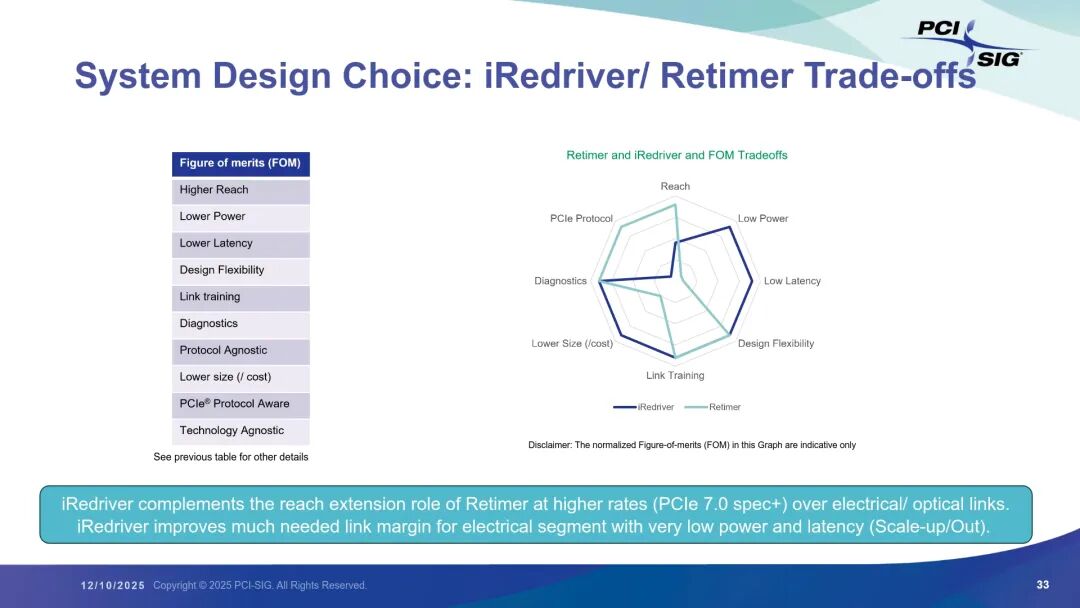

在通道优化方面,随着速率提升,插入损耗、回波损耗、串扰等问题愈发突出。解决方案包括采用更高等级的PCB(如超低损耗Megatron 8材质)、新型连接器设计与先进材料,同时PCIe 6.0/7.0规范引入光学友好ECN,支持光链路部署;Retimer的最大部署数量从2个增加至4个,iRedriver的引入进一步扩展了链路预算优化空间。 在硅片优化方面,PCIe从传统架构转向ADC-based DSV架构,发射端与接收端采用更复杂的均衡技术(如PCIe 5.0/6.0的3抽头FFE、PCIe 7.0的4抽头FFE),PLL带宽提升与抖动管理技术升级,保障了高速信号的稳定性;FLIT模式与低延迟FEC/重试机制结合,在实现1E-6误码率的同时,满足AI场景的可靠性要求(Fit目标)。 四、关键技术对比:链路训练与器件权衡 1. 链路训练的核心差异 Retimer与iRedriver的链路训练机制存在本质区别:Retimer作为PCIe协议感知器件,深度参与PHY层交互,通过LTSSM(链路训练与状态机)与根复合体、端点或Switch协同,在带内完成均衡参数调整与信号优化;而iRedriver采用带外管理模式,通过CMIS-LT协议与PCIe设备的固件通信,基于子采样器估算通道脉冲响应,自动优化自身CTLE/FFE参数,甚至建议Host 端FFE配置,完成局部链路优化后,再移交PCIe端到端链路训练。这种模式既保证了链路质量,又避免了协议依赖,实现了低延迟与灵活性的平衡。 2. 器件选择的核心权衡 Retimer与iRedriver并非替代关系,而是互补关系:Retimer的优势在于协议原生支持、更高的传输距离与更全面的信号重置能力,适合开放系统、长距离传输等场景;iRedriver则在低功耗、低延迟、低成本与协议无关性上表现突出,适合封闭系统、短距离互联、AI scale-up/scale-out等对功耗和成本敏感的场景。Switch则专注于大规模fabric构建,支撑多设备协同与复杂拓扑,是规模化部署的核心枢纽。 从关键指标权衡来看,Retimer在“传输距离”与“PCIe协议兼容性”上占优,iRedriver则在“功耗”“延迟”“尺寸成本”“部署灵活性”上更具优势,两者共同覆盖了AI数据中心从短距离互联到长距离传输的全场景需求。 五、总结与未来展望

AI时代的数据中心架构革新,将PCIe技术推向了新的高度。Retimer、iRedriver与Switch作为核心连接器件,分别以“信号完整性与长距离”“低功耗低延迟”“大规模拓扑支撑”为核心优势,共同构建了PCIe生态的多元化解决方案。PCIe 7.0的落地与PCIe 8.0的预研,叠加PAM4、FLIT、ADC-based架构等技术突破,持续推动带宽翻倍与性能升级;而DirectDrive ECR等规范的推进,将进一步释放iRedriver的潜力,实现无Retimer的长距离传输。

未来,PCIe技术将继续围绕AI场景的核心需求迭代:带宽将持续提升以支撑更大规模的并行计算,延迟与功耗将进一步优化以适配边缘AI与高密度部署,协议无关性与多协议支持将增强生态灵活性。Retimer、iRedriver与Switch的协同应用,将成为数据中心架构设计的核心考量,为AI训练、推理、存储等全场景提供稳定、高效、灵活的连接支撑,推动数据中心向更高性能、更低功耗、更优成本的方向演进。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-12-19,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读