计算机中的软件和硬件是如何协同工作的?

计算机中的软件和硬件是如何协同工作的?

用户1493530

发布于 2026-05-06 21:38:22

发布于 2026-05-06 21:38:22

计算机中的软件和硬件是如何协同工作的?能否举例说明?

我本科是化工专业出身,后来自学转行做了 iOS 开发。说实话,刚入行那几年我对软硬件协同这个问题也是一头雾水,觉得代码写完点个 Run 就跑了,底下发生了什么跟我没关系。直到有一次线上出了个性能问题,一个列表滑动卡顿到掉帧,我用 Instruments 抓 profile 发现瓶颈居然不在业务逻辑,而是图片解码占满了 CPU 导致 GPU 合成跟不上节奏。那一刻我才意识到:你写的每一行代码,最终都要经过 5 到 8 层抽象才能让硬件真正执行,任何一层出问题都会炸。

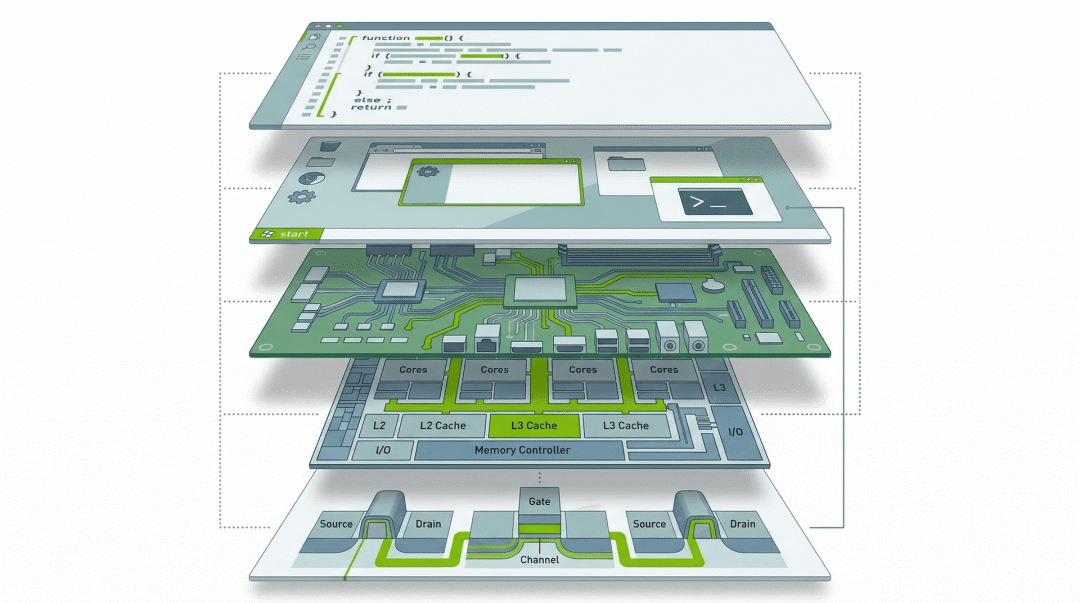

这个回答我打算从一个化工人的视角来讲这件事。化工里有个核心方法论叫控制变量法,做实验、调参数、排查问题全靠它。计算机的软硬件协同其实也是一样的思路:每一层抽象都在「控制」上下层之间的接口变量,让复杂度不会一路泄漏到顶层。理解了这些「控制界面」在哪,你就真正理解了软硬件是怎么配合的。

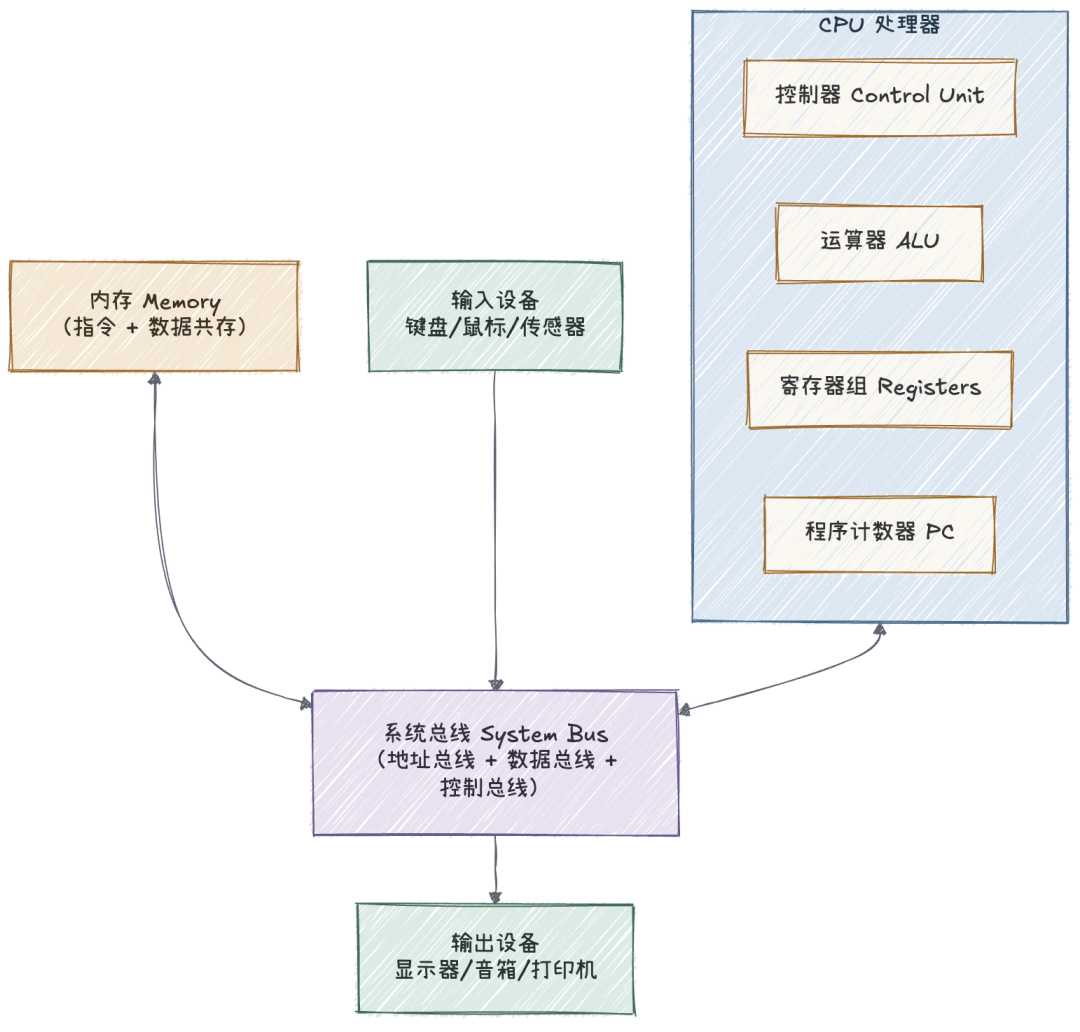

◆一切的起点:冯·诺依曼的那个「存储程序」想法

1945 年之前,「编程」这件事是物理操作。ENIAC 的程序员得手动插拔电缆、拨开关来配置计算路径,换个程序可能要折腾好几天。冯·诺依曼在那份著名的 EDVAC 报告里提出了一个看起来很简单的想法:把程序指令和数据放在同一块可读写的内存里。这个想法直接催生了「软件」这个概念,程序不再是物理连线,而是可以像数据一样被存储、复制、修改的东西。

今天几乎所有计算机仍然遵循这个基本架构,核心就五个部件:CPU(包含运算器和控制器)、内存、输入设备、输出设备,以及连接它们的总线。CPU 做的事情说白了就是一个死循环:从内存取指令→解码→执行→取下一条,周而复始。程序计数器(PC)负责记住「下一条指令在哪」,所有的程序执行归根到底就是这个循环在不停转。

这个架构有个天生的瓶颈,John Backus 在 1977 年图灵奖演讲里管它叫 「冯·诺依曼瓶颈」:CPU 和内存之间只有一条总线,所有指令和数据都要通过这根「独木桥」。后面你会看到,缓存、DMA、统一内存这些东西全是在想办法把这根独木桥拓宽或者绕过去。

◆ISA:软件和硬件之间的「合同」

好,冯·诺依曼架构告诉我们硬件的基本骨架长什么样。但软件怎么知道该跟硬件说什么「语言」呢?答案是 ISA(Instruction Set Architecture,指令集架构)。

宾夕法尼亚大学 CIS 371 课程对 ISA 的定义特别精准:它是软件和硬件之间一份明确定义的接口合同。这份合同规定了:有哪些指令可以用、数据格式是什么、有多少寄存器、怎么寻址内存、怎么做 I/O。但关键是,它不规定硬件内部怎么实现这些指令,也不承诺哪条指令跑得快。

这个分离是 1964 年 Fred Brooks 做 IBM System/360 时确立的,意义极其深远。它意味着 Intel 和 AMD 可以用完全不同的芯片内部设计来实现同一套 x86 指令集,你编译好的程序在两家的 CPU 上都能跑。ISA 就是那个「控制变量」的界面,上面的软件只需要关心合同里写了什么,下面的硬件想怎么优化是自己的事。

目前主流的 ISA 哲学有两派。CISC(复杂指令集),代表是 x86,一条指令可以做很多事,指令长度不固定(1~15 字节),好处是程序体积小,代价是硬件解码复杂。RISC(精简指令集),代表是 ARM 和 RISC-V,每条指令只做一件事,固定长度(通常 32 位),硬件流水线简单高效,把优化的活儿交给编译器。David Patterson 1982 年做的 RISC-I 只有 44,420 个晶体管和 32 条指令,性能却超过了同期所有单芯片设计。

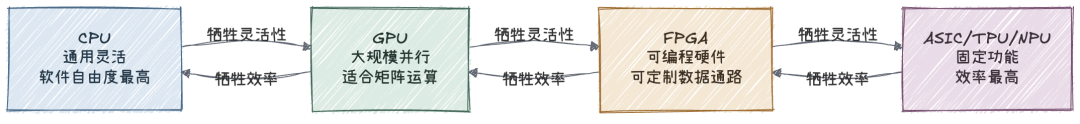

其实吧,今天这个界限已经很模糊了。现代 x86 CPU 内部会把 CISC 指令拆成类似 RISC 的微操作(µops)来执行,而 ARM 也搞了压缩指令集。真正有意思的区分变成了通用 ISA(x86、ARM、RISC-V)和领域专用架构(GPU shader 指令、Google TPU 指令、NPU 指令)之间的光谱。从 CPU 到 GPU 到 FPGA 到 ASIC,本质上是在软件灵活性和硬件效率之间做取舍。

◆从源代码到机器指令:编译是怎么「翻译」的

你写了一行 printf("Hello, World!\n"),CPU 不认识这玩意儿。它只认识 0 和 1 组成的机器指令。从你的源代码到硬件能执行的二进制之间,要经过一整条编译流水线,每个阶段都是软件在为硬件做「翻译」和「适配」。

这里面最关键的一步是编译器优化。编译器要理解目标硬件的特性(缓存行大小、流水线深度、分支预测行为),才能生成高效的机器码。GCC 开 -O2 优化,典型场景下能比 -O0 快 2~3 倍。而 -O3 有时候反而比 -O2 慢,因为过于激进的内联会把代码膨胀到超出指令缓存容量,顾此失彼。

不同语言在这条流水线上的位置不同,直接决定了它们利用硬件的效率。C 代码直接编译成原生机器指令,CPU 拿来就跑。Java 先编译成平台无关的字节码,运行时由 JIT 编译器把热点代码再翻译成原生指令。Python(标准 CPython)则是纯解释执行字节码,没有 JIT,同样的计算密集任务比 C 慢 20~150 倍。说白了,编译策略决定了你的代码离硬件有多「近」,离得越近性能越好,但开发效率和可移植性就越差。这又是一个 trade-off。

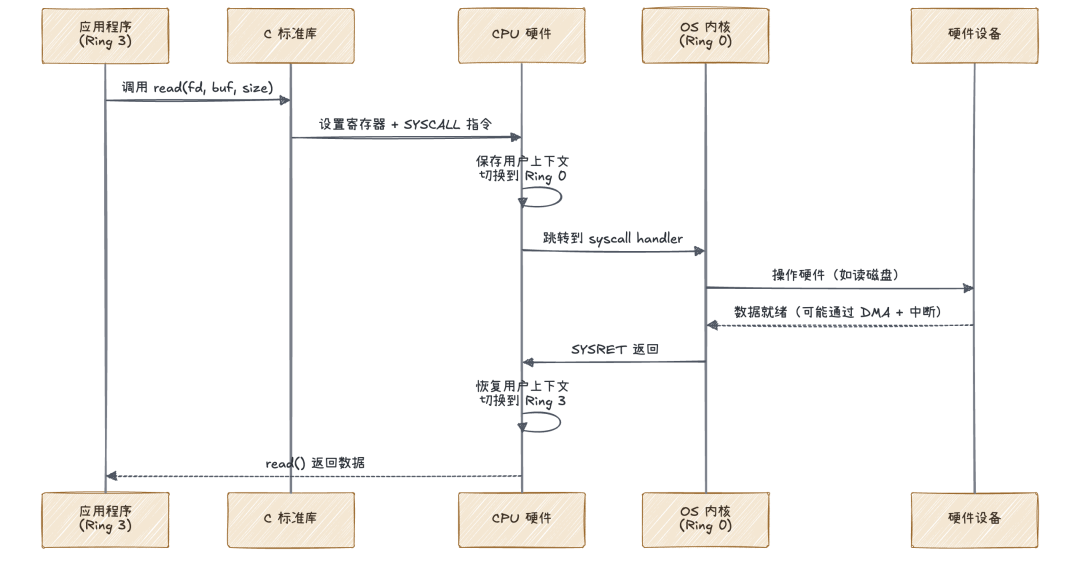

◆操作系统:用户程序和硬件之间的守门人

你写的程序不能直接访问硬件。这是个硬性规定,由 CPU 硬件强制执行。x86 处理器有特权级机制(Ring 0 到 Ring 3),OS 内核跑在 Ring 0,拥有完整硬件访问权限;你的应用程序跑在 Ring 3,碰不到任何硬件资源。这个隔离是安全和稳定性的基石,也是软硬件协同中最重要的一道「防火墙」。

那程序要读文件、发网络包、写屏幕怎么办?答案是系统调用(System Call)。以 Linux 上调用 read() 为例:C 库的封装函数把系统调用号放进 RAX 寄存器,参数放进 RDI、RSI、RDX,然后执行 SYSCALL 指令。CPU 硬件自动保存用户态上下文、切换到内核态(Ring 0)、跳转到内核的系统调用处理入口。内核通过系统调用表找到对应的处理函数,执行完毕后用 SYSRET 返回用户态。一次简单的系统调用(比如 getuid())大概耗时 50-200 纳秒,比普通函数调用(1~5 ns)贵 100 倍左右。

这个开销不是白花的。Linux 为了优化高频调用搞了 vDSO 机制,把 gettimeofday() 这类只读操作映射到用户空间,开销降到 5~20 ns,根本不用切内核。

中断是反过来的通道:硬件主动通知 CPU。键盘按了一个键,产生 IRQ 1,中断控制器(现代系统用 APIC)通知 CPU,CPU 执行完当前指令后保存上下文、查 中断描述符表(x86 上 256 个表项)、切到内核态、跳到对应的中断服务程序(ISR)。定时器中断(通常每 1-10 毫秒触发一次)让内核调度器得以抢占正在运行的进程,做上下文切换,制造出「多个程序同时运行」的假象。一次上下文切换直接开销大约 1.5-3.5 微秒,但间接代价更大:缓存和 TLB 被污染,恢复后的程序得重新「热身」。

I/O 机制也经历了三代进化。最原始的轮询 I/O,CPU 死循环检查设备状态,纯浪费算力。中断驱动 I/O 让 CPU 在等待期间可以干别的,但每传一个字节都要 CPU 介入。终极方案是 DMA(直接内存访问):CPU 告诉 DMA 控制器「从这里搬这么多数据到那里」,然后就可以去执行其他指令了。DMA 控制器独立完成整块数据的搬运,搬完了才发一个中断通知 CPU。现代的进阶版本包括 Intel 的 DDIO(DMA 直接写入 L3 缓存而非内存)和 RDMA(跨网络的远程 DMA,AI 训练集群的关键技术)。

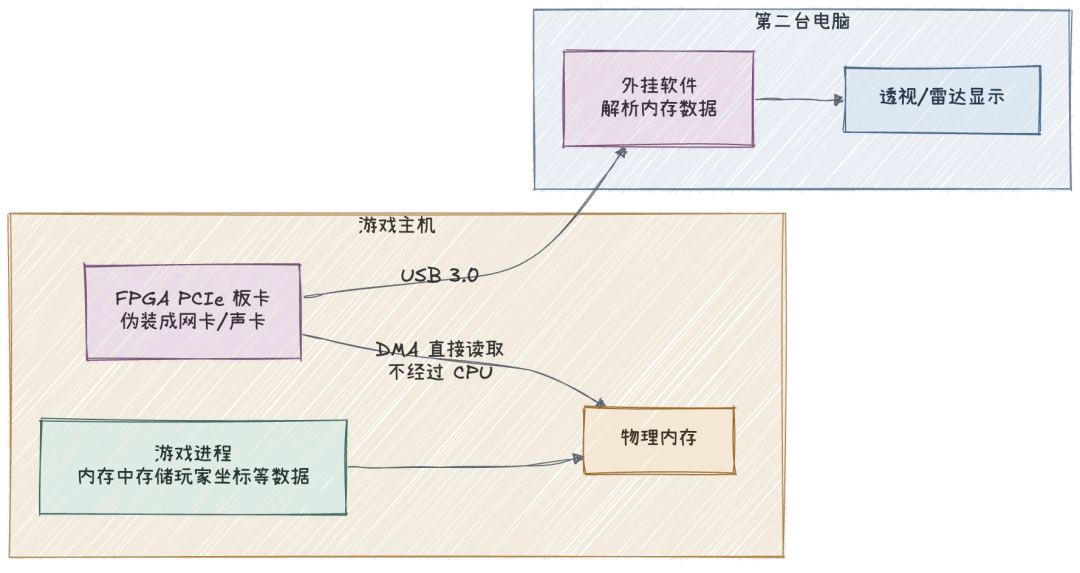

说到 DMA,打游戏的朋友可能会觉得这词耳熟。没错,现在 FPS 游戏里那些「硬件外挂」用的就是这个技术。外挂制作者把一块基于 FPGA 的 PCIe 板卡插到游戏主机的主板上,这块板卡通过 PCIe 总线直接读取物理内存里的游戏数据(玩家坐标、血量、敌人位置),然后通过 USB 3.0 线把数据传到第二台电脑。副机上运行外挂软件做数据解析,再通过融合器把透视框叠加到游戏画面上,或者通过键鼠模拟盒子实现自瞄。

这就是为什么传统反作弊软件拿它没办法的原因。前面讲了,DMA 的核心特性就是绕过 CPU 直接访问内存,不走操作系统的任何软件通道。反作弊程序哪怕跑在内核态(Ring 0),它监控的也是 CPU 上的软件行为(进程注入、内存修改、驱动加载),对一块 PCIe 设备通过硬件总线直接读内存这种事,它根本「看不见」。而且这块 FPGA 板卡还会通过定制固件把自己伪装成一块普通网卡或声卡,Vendor ID、Device ID 全部仿冒合法设备,系统看到的只是多了一个「正常」的 PCIe 外设。

其实吧,理解了前面讲的软硬件分层架构,你就能看出这个攻击的精妙之处:它恰好卡在了操作系统管不到、但硬件总线又允许的那个缝隙里。反作弊系统的「管辖范围」在 Ring 0 内核层,而 DMA 操作发生在更底层的 PCIe 总线层,两者之间缺少一道门。

反制手段也很有意思,本质上是在补这道门。Intel 的 VT-d 和 AMD 的 IOMMU 技术给外设的 DMA 请求也加了一层类似 MMU 的地址翻译和权限控制。说白了就是给 PCIe 设备的内存访问也装一个「虚拟内存」机制,操作系统可以精确控制每个设备能访问哪些内存区域。腾讯的《三角洲行动》已经强制要求 Intel 平台玩家开启 VT-d,Riot 的 Vanguard 反作弊也会在游戏启动时扫描 PCIe 插槽检测可疑设备。这场攻防战本身就是软硬件协同的一个绝佳案例:攻击者利用硬件层的 DMA 能力绕过软件层的安全检测,防御者则通过启用更底层的硬件安全特性(IOMMU)来封堵漏洞。每一轮升级都是在不同的抽象层上重新划定软硬件的权限边界。

◆内存层次:软硬件协同的最亲密接触

内存层次结构大概是软硬件协同最精妙的设计了。硬件提供了一个金字塔形的存储体系(越往上越快越贵越小),软件(OS 和应用程序)必须让数据访问模式去「适配」这个金字塔,才能获得好的性能。

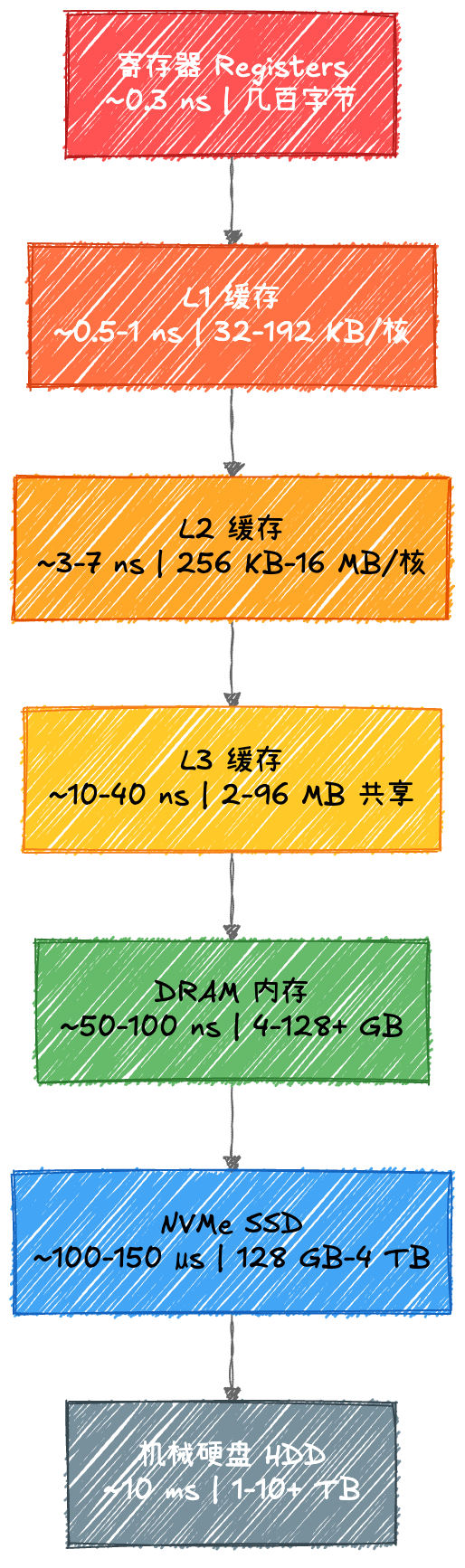

先看一组延迟数字,这是每个程序员都应该刻在脑子里的:L1 缓存 ~0.5 ns,DRAM ~100 ns(慢 200 倍),NVMe SSD ~100 µs(慢 20 万倍),机械硬盘 ~10 ms(慢 2000 万倍)。

这个 20 万倍的延迟落差意味着什么?同样是遍历一个二维数组,按行遍历(cache-friendly)和按列遍历(cache-unfriendly)的性能差距可以达到 2~8 倍,加上向量化优化能拉到 25 倍。代码一模一样,数据一模一样,就因为访问顺序不同导致缓存命中率天差地别。这就是纯粹的「软件理解硬件」带来的性能红利。

虚拟内存是硬件和软件合作的巅峰之作。每个进程都以为自己独占了一整块连续的内存空间,实际上 OS 在背后通过页表把虚拟地址映射到物理内存的不同位置。CPU 内置的 MMU(内存管理单元) 在每次内存访问时都要做这个地址翻译,为了加速,硬件还有一个 TLB(地址转换缓存),命中率通常超过 99%。TLB 没命中的话,MMU 得做一次「页表行走」(x86-64 上要遍历 4 级页表)。如果请求的页面根本不在物理内存里(缺页中断),MMU 产生异常,OS 把页面从磁盘加载进来,更新页表和 TLB,然后重启那条指令。整个过程对应用程序完全透明。中文资料对此有个很精辟的评价:虚拟存储是 CPU/MMU/TLB 硬件与操作系统深度协同的典范杰作。

设备驱动是最后一块拼图。驱动运行在内核态,负责把 OS 的通用命令翻译成特定硬件能理解的寄存器读写操作。现代系统主要通过 **MMIO(内存映射 I/O)**来做这件事:设备的控制寄存器被映射到 CPU 的地址空间,驱动用普通的 load/store 指令就能操作硬件。驱动知道设备的寄存器布局和时序要求,OS 只认识通用接口。这种分离让你换一块网卡不需要重新编译浏览器。

◆按一下键盘到底发生了什么

理论讲完了,来追踪一次真实的按键过程,看看每一层是怎么交接的。

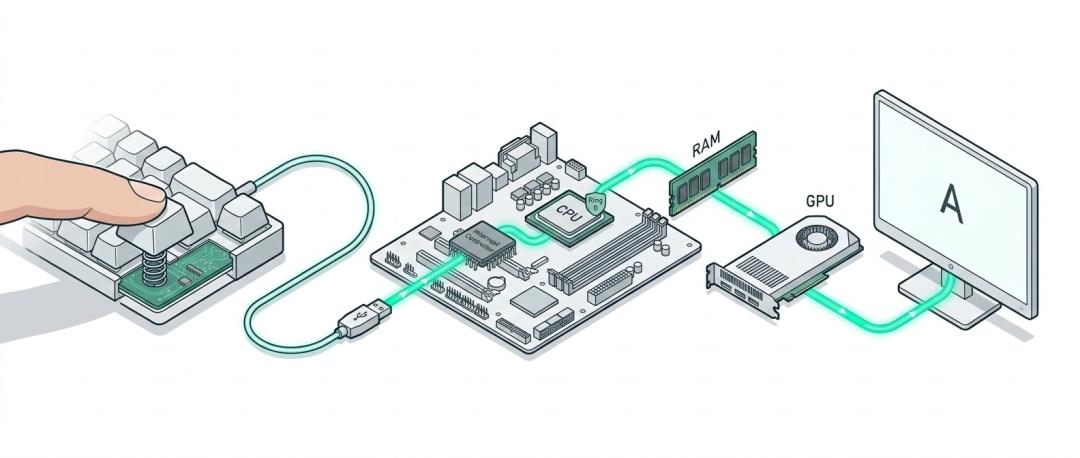

键盘内部有个嵌入式微控制器,以 1000 Hz 的频率扫描按键矩阵。检测到某个键按下后,生成一个扫描码,通过 USB 协议发送到主机的 USB 控制器。控制器触发一个硬件中断(PS/2 键盘是 IRQ 1,USB 键盘走 MSI 中断)。

CPU 执行完当前指令(约 200~500 ns),保存上下文到内核栈,查中断描述符表找到对应的 ISR 地址,切到 Ring 0 执行。ISR 从 I/O 端口(PS/2 的 0x60)或 USB 缓冲区读出扫描码,应答中断,排入延迟处理队列。键盘驱动把扫描码翻译成键码(考虑当前键盘布局和修饰键状态),生成一个输入事件放进 OS 的事件队列(Linux 上是 /dev/input/)。

窗口管理器读取事件,判断哪个应用程序拥有键盘焦点,通过显示协议(X11 的 KeyPress、Wayland 的 wl_keyboard、Windows 的 WM_KEYDOWN)分发给目标应用。应用的事件循环收到字符,插入文本缓冲区,触发渲染引擎查字体文件找到对应字形,计算排版,通过显示服务器发绘制指令给 GPU,GPU 把像素写入帧缓冲,显示控制器扫描帧缓冲输出到屏幕。

一次按键,12 次跨越软硬件边界的交接。从电信号到微控制器到总线协议到中断控制器到 CPU 到内核到驱动到输入子系统到窗口管理器到应用到 GPU 到显示器。整个链路耗时通常在 10~50 毫秒 量级,人类感知不到延迟,但底层跑了一整套精密的软硬件协作流程。

◆GPU 渲染:软硬件高强度合作的现场

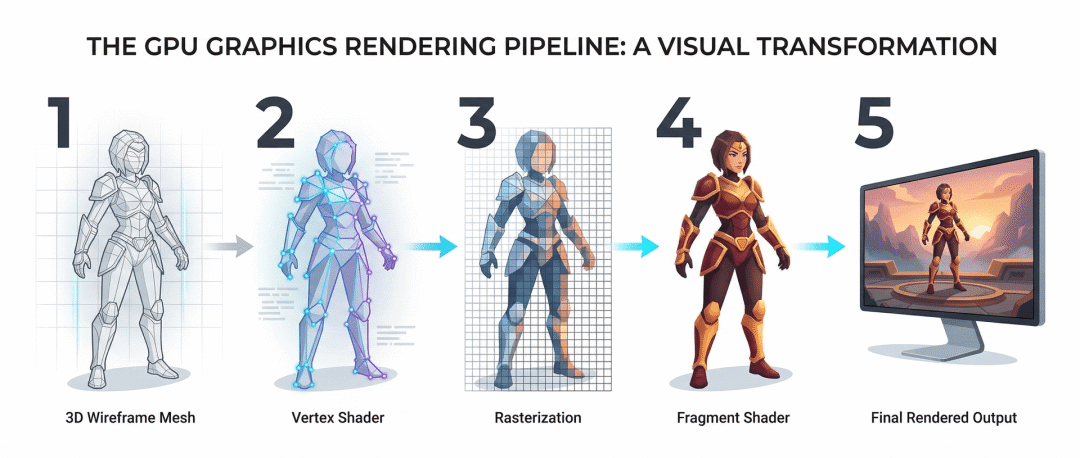

如果说键盘输入是「轻量级」的软硬件协同,那 GPU 渲染就是「重体力活」了。游戏的每一帧画面,CPU 和 GPU 都要密切配合完成一条完整的渲染管线。

CPU 这边负责游戏逻辑(物理模拟、AI、输入处理),然后用图形 API(Vulkan、DirectX 12、Metal)把绘制命令录制到 Command Buffer 里,提交到 GPU 的命令队列。图形驱动负责把 API 调用翻译成 GPU 硬件能理解的私有二进制格式。

GPU 收到命令后,通过一条混合了可编程着色器阶段和固定功能硬件的管线来处理。顶点着色器把每个顶点做矩阵变换(模型→视图→投影),这是纯并行计算,几千个 GPU 核心同时干活。然后固定功能硬件做裁剪、透视除法、光栅化(把三角形转成片元/候选像素)。片元着色器是计算最密集的阶段:采样纹理、计算光照、施加特效,每个片元独立处理。最后光栅操作单元做深度测试、模板测试、混合,把最终颜色写入帧缓冲。

双缓冲或三缓冲防止撕裂:GPU 往后台缓冲区画,显示器展示前台缓冲区,VSync 信号来了再交换(60 Hz 显示器每 16.67 ms 一次)。G-Sync、FreeSync 这类自适应同步技术让 GPU 控制刷新节奏,减少延迟。典型渲染管线从输入到画面上屏有 2~3 帧的延迟(60 FPS 下约 33~50 ms)。

◆AI 时代:软件的计算模式直接重塑了芯片

AI 是软件驱动硬件设计最极端的案例。神经网络的核心操作是矩阵乘法,这玩意天然可并行:输出矩阵的每个元素可以独立算出来。CPU 的 4~64 个强核做这事效率很低,但 GPU 的几千个小核心正好合适。NVIDIA A100 的 6,912 个 CUDA 核心加 432 个 Tensor Core 能达到 312 TFLOPS(FP16)。做 4096×4096 的矩阵乘法,GPU 比单线程 CPU 快大约 593 倍。

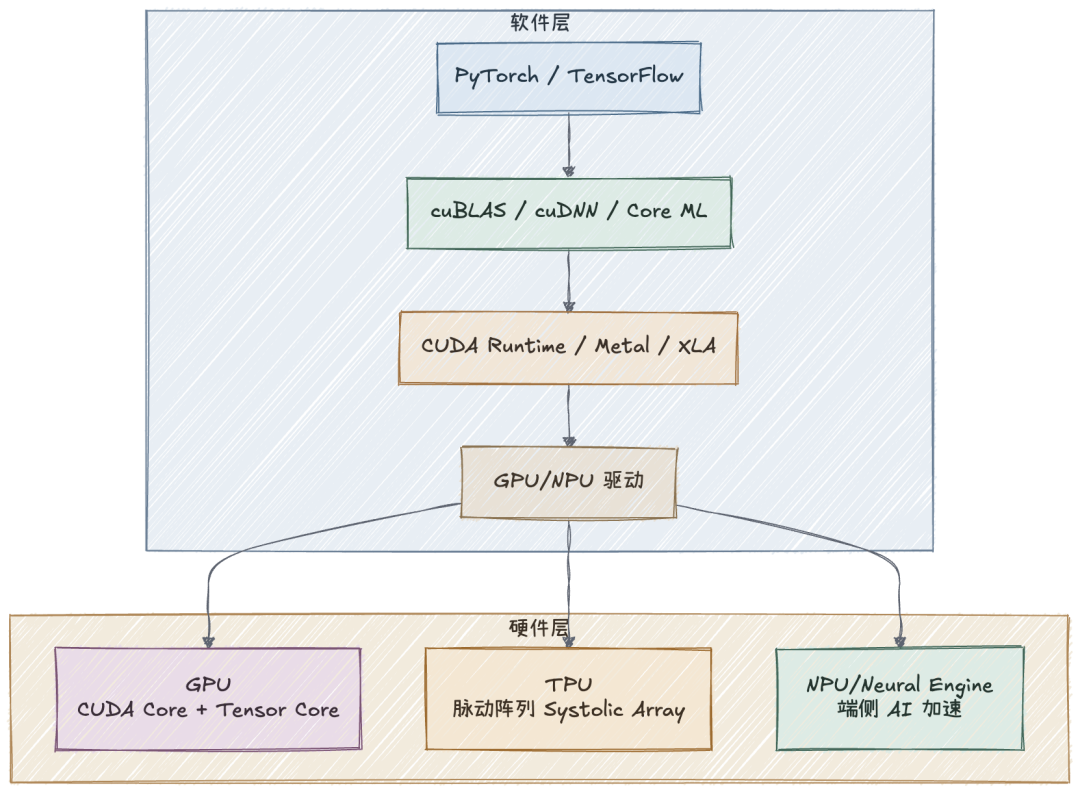

CUDA 是连接软件和 GPU 硬件的桥梁。开发者写 kernel 函数,组织成线程块和网格,映射到 GPU 的流多处理器上执行。完整的调用栈是:PyTorch → cuBLAS/cuDNN → CUDA Runtime → CUDA Driver → GPU 硬件。你在 PyTorch 里调 torch.matmul(),底层其实是 C++ 后端选了一个优化过的 cuBLAS kernel,通过 CUDA 运行时提交给 GPU,GPU 用 Tensor Core 做混合精度矩阵运算。

Google 的 TPU 把协同设计推到了极致:芯片内部的 256×256 脉动阵列(65,536 个乘累加单元)让数据像节拍器一样流过处理单元,从根本上消除了冯·诺依曼瓶颈中反复访问内存的问题。初代 TPU 在推理场景下比同时期 CPU/GPU 实现了 15~30 倍的性能提升和 30~80 倍的能效提升。**NPU(神经网络处理单元)**则把这种专用设计带到了终端设备:Apple M5 的 16 核 Neural Engine 配合 GPU 内每核心内置的 Neural Accelerator,AI 性能达到 M1 的 5.6 倍,用毫瓦级功耗就能跑 Face ID、Siri 和计算摄影的推理。

◆前沿动态:Apple Silicon、RISC-V、NVIDIA Rubin

Apple Silicon 是消费级产品里软硬件协同做得最深的。最新的 M5 芯片(2025 年 10 月发布,台积电第三代 3nm)把 CPU、GPU、Neural Engine、媒体引擎和内存控制器集成在一颗芯片上,用 统一内存架构(UMA) 让所有处理器共享同一块 LPDDR5X 内存,带宽达到 153.6 GB/s,比 M4 提升近 30%。这消除了传统架构中 CPU 和 GPU 之间来回拷贝数据的开销。M5 的 GPU 引入了全新架构:每个 GPU 核心内置一个 Neural Accelerator,AI 工作负载的 GPU 峰值算力达到 M4 的 3.5 倍。2026 年 3 月发布的 M5 Pro 和 M5 Max 更进一步,采用 Apple 自研的 Fusion Architecture(双裸片封装),M5 Max 配备 40 核 GPU,最高 128 GB 统一内存,带宽推到 614 GB/s,足以在本地跑 70B 参数的大语言模型。macOS 从底层专门为这套架构优化:Rosetta 2 翻译 x86 应用,Metal 直接暴露 Apple GPU 的 TBDR 特性,Core ML 原生调度 Neural Engine。Apple 的 MLX 框架专门为 UMA 设计,模型权重对所有处理器直接可见,不需要 PCIe 搬运,可以在本机跑 LLM 推理。M5 还引入了 Memory Integrity Enforcement(MIE),基于 ARM 的增强内存标签扩展实现硬件级内存安全保护,防御缓冲区溢出和 use-after-free 漏洞。从 M1 到 M5 这五代迭代,Apple 把软硬件协同的边界不断往深处推:芯片架构为操作系统量身定制,操作系统又反过来充分压榨芯片的每一个特性。

RISC-V 正在重塑软硬件之间的「合同」本身。作为开源 ISA,没有授权费,任何人都可以添加领域专用扩展指令。2023 年市场规模达到 61 亿美元(同比增长 276.8%),预计 2030 年将达到 927 亿美元。NVIDIA 已经在 GPU 内部嵌入了大约 10 亿颗 RISC-V 核心用于内部控制功能,并正在把 CUDA 移植到 RISC-V。Google 宣布 RISC-V 是 Android 开发的「一等公民」,并在 2025 年 10 月发布了基于 RISC-V 的 Coral NPU 边缘 AI 平台。2024 年 10 月批准的 RVA23 profile 标准化了通用扩展集,让不同实现之间的软件可以互相迁移。

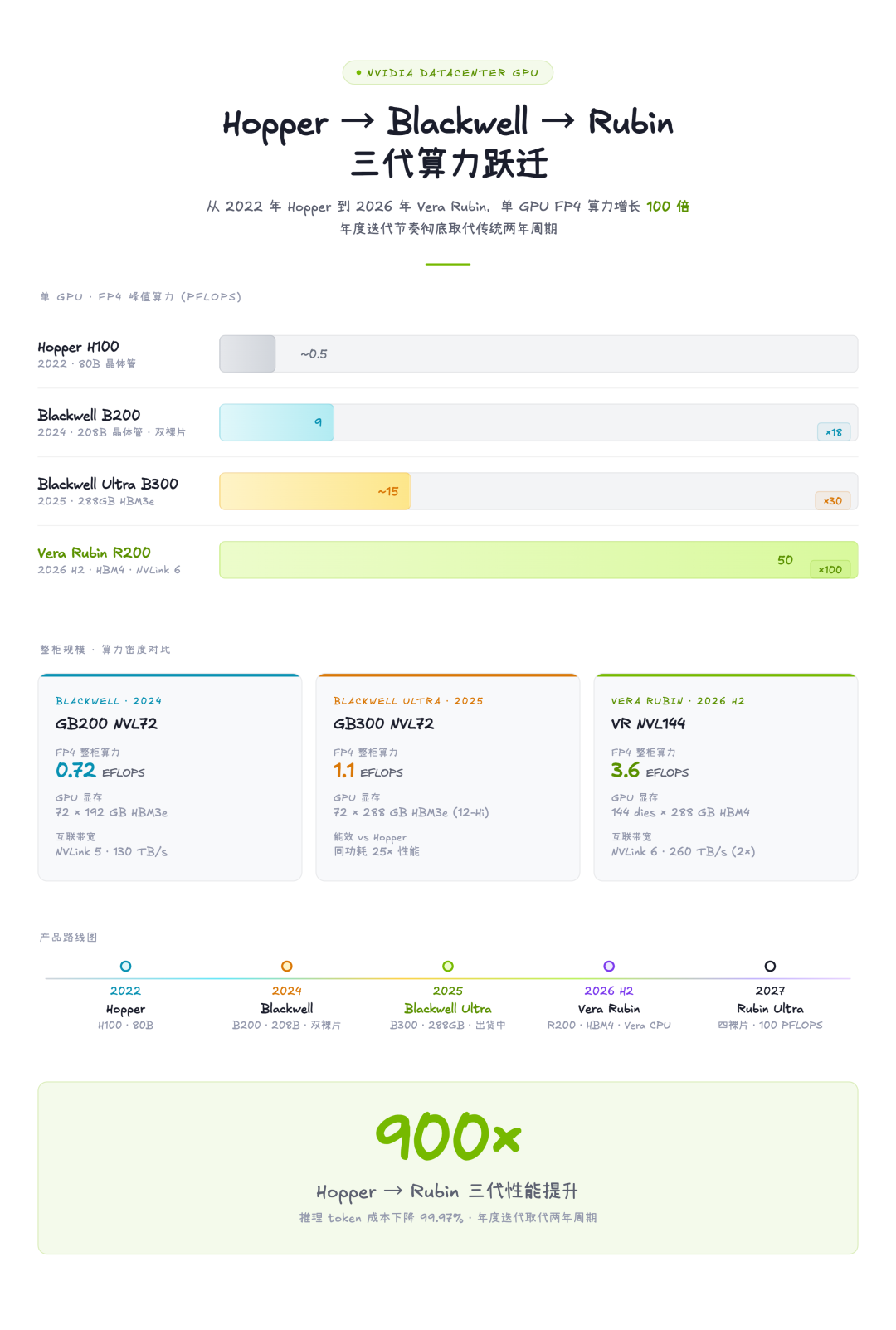

NVIDIA 的数据中心 GPU 已经进入年度迭代节奏,软硬件协同设计的密度越来越高。Blackwell 架构(B200,2024 年)首次采用双裸片封装,2080 亿晶体管通过 10 TB/s 芯片间互联组成统一 GPU,配备 192 GB HBM3e(带宽 8 TB/s),第二代 Transformer Engine 支持 FP4 精度动态缩放,单 token 能耗从 Hopper 的 12 焦降到 0.4 焦。2025 年中发布的 Blackwell Ultra(B300) 把显存推到每 GPU 288 GB(12-Hi HBM3e),GB300 NVL72 整柜提供 1.1 EFLOPS 的 FP4 算力,同等功耗下性能是 Hopper 的 25 倍。预计 2026 年 GB300 出货量将同比增长 129%,微软、亚马逊、Meta 等都在大规模部署。

再下一代 Vera Rubin 平台已经完成 tape out,计划 2026 下半年上市。Rubin GPU(台积电 3nm + HBM4)单 GPU 达到 50 PFLOPS 的 FP4 算力(Blackwell 的 3 倍以上),VR NVL144 整柜更是达到 3.6 EFLOPS。它还配套了全新的 Vera CPU(取代 Grace)和 NVLink 6(总带宽翻倍到 260 TB/s)。NVIDIA 官方称 Rubin 平台可以实现推理 token 成本降低 10 倍、训练 MoE 模型所需 GPU 数量减少 4 倍。再往后还有 2027 年的 Rubin Ultra(四裸片封装,100 PFLOPS)和 2028 年的 Feynman 架构。从 Hopper 到 Blackwell 到 Rubin 这三代,NVIDIA 实现了 900 倍的性能提升和 99.97% 的成本下降,年度迭代的节奏已经彻底取代了传统的两年周期。Google 的 TPU v6(Trillium) 于 2025 年初正式可用,峰值算力是 v5e 的 4.7 倍,能效提升 67%。

大趋势是异构计算:CPU + GPU + NPU 协同工作,每个处理器做它最擅长的事。CXL(Compute Express Link)协议构建在 PCIe 物理层之上,添加了缓存一致性协议,让 CPU 可以一致性地访问加速器挂载的内存,解决了异构处理器之间的数据搬运问题。CXL 3.0 支持跨主机的真正共享内存和点对点 DMA,PCIe 7.0 草案已发布,带宽再翻倍。

◆一张表看清优化空间有多大

最后用数据说话。下面这组数字展示的是同一个计算任务在不同软硬件协同层次上的性能差异,足以说明理解这些层次为什么重要:

优化手段 | 典型加速比 | 利用的硬件特性 |

|---|---|---|

C vs Python(同算法) | 20~150× | 编译执行 vs 解释执行 |

编译器 -O2 vs -O0 | 2~3× | 指令调度、寄存器分配 |

缓存友好 vs 缓存不友好的访问模式 | 2~25× | 内存层次局部性 |

AVX-512 SIMD vs 标量计算 | 2~8× | CPU 数据级并行 |

GPU vs CPU(大矩阵乘法) | 45~600× | 大规模硬件并行 |

全栈优化(优化 GPU 代码 vs 朴素 Python) | >10,000× | 所有层次叠加 |

4096×4096 的矩阵乘法,顺序 C 实现约 390 秒,OpenMP 并行化后约 28 秒,放到 GPU 上约 0.66 秒。从头到尾 593 倍的加速,纯粹来自对硬件并行架构的理解和利用。

◆回到那个核心问题

计算机的软硬件协同,归根到底是一个多层接口的协商过程。ISA 是指令级的合同,编译器是语言到机器码的翻译官,OS 内核通过系统调用和中断做软硬件之间的守门人,虚拟内存让 MMU 硬件和 OS 联手制造地址空间的幻觉,设备驱动翻译每种外设的「方言」,DMA 和 CXL 在后台搬运数据。每一层都在做两件事:向上隐藏复杂性,向下保留控制力。

作为一个从化工跨行到计算机的人,我觉得这跟化工里的「单元操作」思想异曲同工。一套化工流程被拆成蒸馏、萃取、结晶这些标准单元,每个单元有明确的输入输出接口,内部怎么实现可以独立优化。计算机的抽象层也是一样:每一层是一个「单元操作」,控制好接口变量,内部随便折腾。

理解了这些层次,你就不再是「写完代码点 Run 然后祈祷」的状态了。缓存未命中是 200 倍延迟惩罚,系统调用是 100 ns 的特权切换开销,GPU 是一种根本不同的计算架构需要不同的算法。把计算机从黑盒变成可理解的工程系统,起点就是搞清楚软件和硬件在每一层是怎么握手的。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-07,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录