Verilog:公共总线实现问题

提问于 2014-07-22 10:06:02

我在Verilog上编写了一个16位的RISC微处理器,我遇到了另一个障碍。在代码编写任务结束后,我试着合成它。发现了几个偶然的错误,我把它们修好了。然后砰,大错特错。

该设计由四条16位通用总线组成.出于某种原因,我从综合工具中得到了这些总线的多个驱动错误。

该计算机的架构是由灵感和几乎完全相同的魔术-1由比尔Buzzbee,不包括页面表机制。这是比尔的原理图PDF:单击此处。向下滚动到第7页的架构。

控制矩阵负责处理巴士和驾驶时的情况,我绝对相信在任何给定的情况下,每辆巴士只有一名司机。我想知道这是否是问题所在,因为合成工具可能不知道这一点。

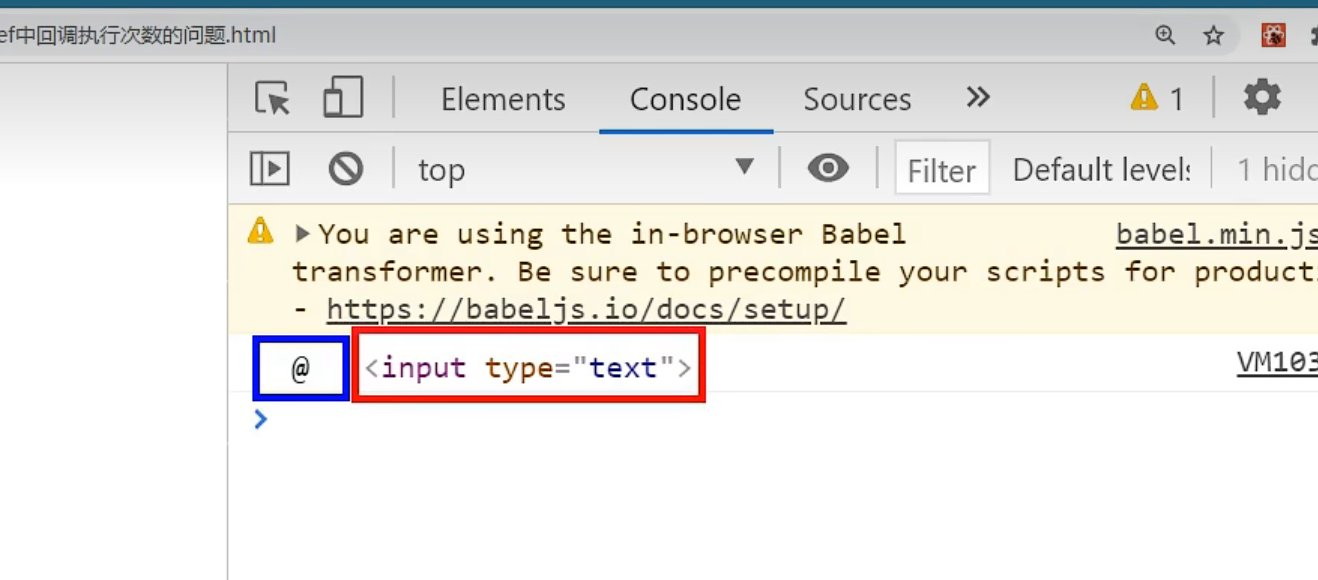

三状态语句允许写入总线,例如:

assign io [width-1:0] = (re)?rd_out [width-1:0]:0; // Assign IO Port the value of memory at address add if re is true.编辑:我忘了提到,io端口是双向的(inout),只是连接到总线上。这段代码来自RAM,单端口。RAM以外的所有其他寄存器都有独立的输入和输出端口。

控制矩阵更新每个负边缘的30位状态,例如:

state [29:0] <= 30'b100000000010000000000000100000; // Initiate RAM Read, Read ALU, Write PC, Update Instruction Register (ins_reg).控制矩阵相当小,因为我只编写了一条指令来测试设计,然后再花时间编写其余的代码。

不幸的是,在这里复制粘贴整个代码是不合逻辑的。

我已经思考了好几天了,我会很感激你把我引向正确的方向。

回答 1

Stack Overflow用户

回答已采纳

发布于 2014-07-22 10:23:01

当re较低时,赋值语句应该是浮动的(驱动Z)。

// enable ? driving : floating

assign io [width-1:0] = (re) ? rd_out [width-1:0] : {width{1'bz}};如果它正在驱动任何其他值,那么合成器将把它看作是一个mux,而不是一个三态。这就是冲突的司机信息的来源。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/24894631

复制相关文章