逻辑电路&代数运算(下)

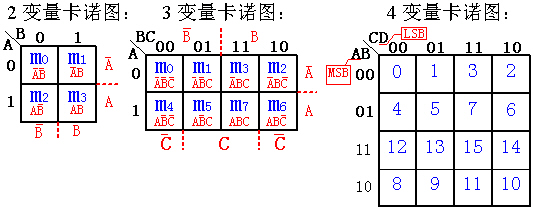

在逻辑代数中,卡诺图(Karnaugh map)是真值表的变形,它可以将有n个变量的逻辑函数的2^n个最小项组织在给定的长方形表格中,同时为相邻最小项(相邻与项)运用邻接律化简提供了直观的图形工具。但是,如果需要处理的逻辑函数的自变量较多(有五个或更多的时候,此时有些项就很难圈了),那么卡诺图的行列数将迅速增加,使图形更加复杂。

变量卡诺图&格雷码

- 表示各最小项的2^n(n-变量数)个小格,排列呈矩形。

- 小格按“格雷码” 排列,保证最小项间“几何相邻”与“逻辑相邻性”的统一。(几何相邻有“内相邻” “外相邻”和“中心对称”)

格雷码的应用

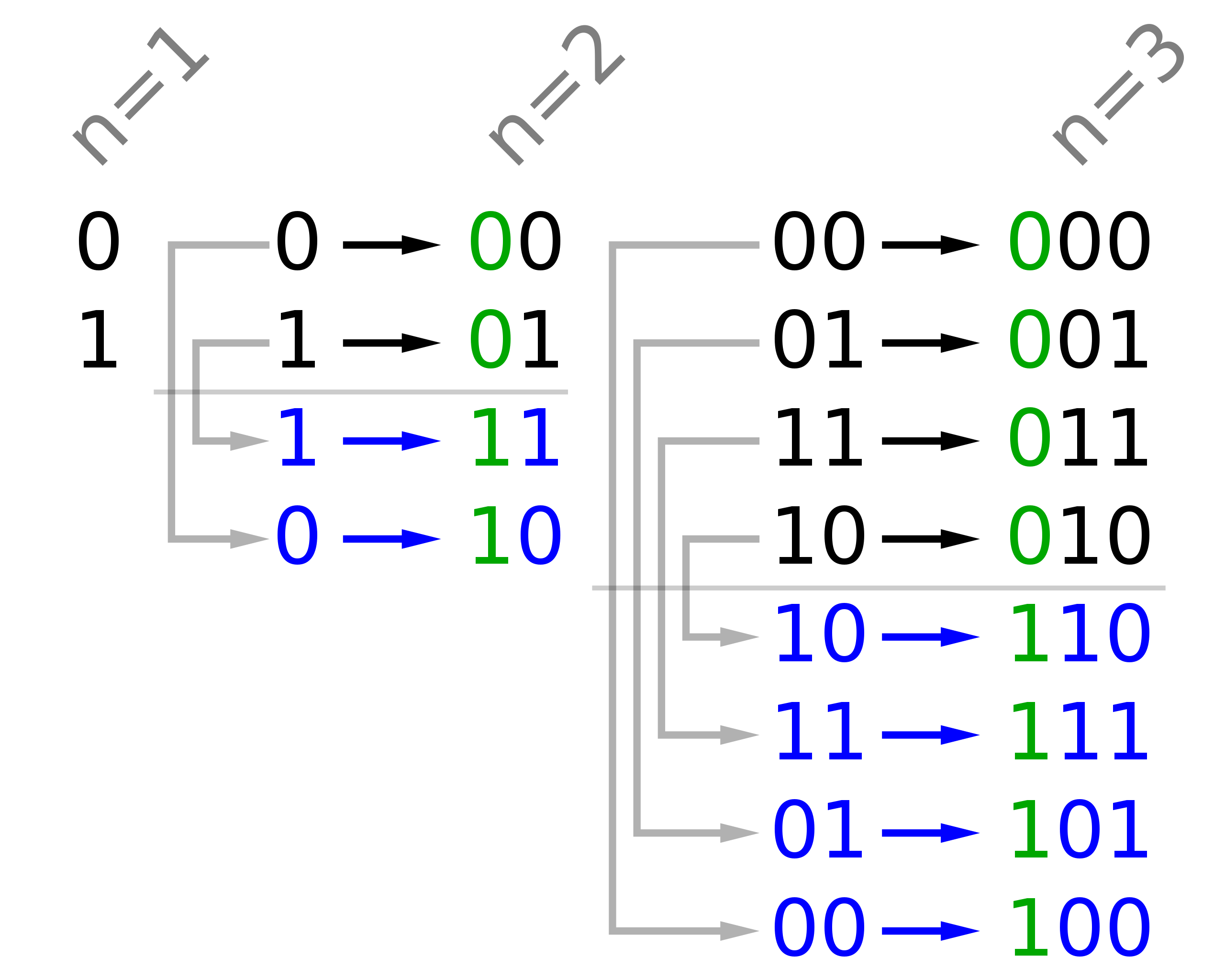

格雷码(循环二进制单位距离码)是任意两个相邻数的代码只有一位二进制数不同的编码,它与奇偶校验码同属可靠性编码。

格雷码能避免讯号传送错误的原理

传统的二进制系统例如数字3的表示法为011,要切换为邻近的数字4,也就是100时,装置中的三个位元都得要转换,因此于未完全转换的过程时装置会经历短暂的,010,001,101,110,111等其中数种状态,也就是代表着2、1、5、6、7,因此此种数字编码方法于邻近数字转换时有比较大的误差可能范围。格雷码的发明即是用来将误差之可能性缩减至最小,编码的方式定义为每个邻近数字都只相差一个位元,因此也称为最小差异码,可以使装置做数字步进时只更动最少的位元数以提高稳定性。 数字0~7的编码比较如下:

十进制 格雷码 二进制

0 000 000

1 001 001

2 011 010

3 010 011

4 110 100

5 111 101

6 101 110

7 100 111格雷码的构建方法

直接排列:

- 以二进制为0值的格雷码为第零项,第一项改变最右边的位元,第二项改变右起第一个为1的位元的左边位元,第三、四项方法同第一、二项,如此反复,即可排列出n个位元的格雷码。

镜射排列:

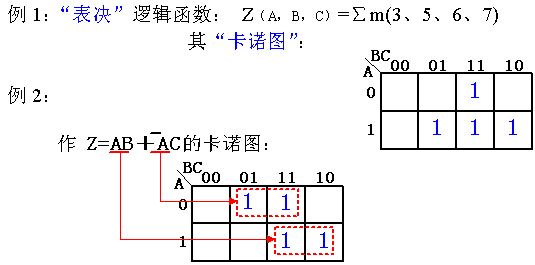

函数卡诺图

- 最小项(Σm):把函数包含的所有最小项,以“1”填入变量卡诺图对应编号的小格内。

- 最大项(ΠM):把函数包含的所有最大项,以“0”填入变量卡诺图对应编号的小格内。

用卡诺图化简逻辑函数的步骤

- 如果表达式为最小项表达式,则可直接填入卡诺图

- 如表达式不是最小项表达式,但是“与—或表达式”,可将其先化成最小项表达式,再填入卡诺图。也可直接填入。

- 合并相邻的最小项,即根据下述原则画圈

- 尽量画大圈,但每个圈内只能含有2^n(n=0,1,2,3……)个相邻项。要特别注意对边相邻性和四角相邻性。

- 圈的个数尽量少。

- 卡诺图中所有取值为1的方格均要被圈过,即不能漏下取值为1的最小项。

- 在新画的包围圈中至少要含有1个未被圈过的1方格,否则该包围圈是多余的。

- 写出化简后的表达式。每一个圈写一个最简与项,规则是,取值为l的变量用原变量表示,取值为0的变量用反变量表示,将这些变量相与。然后将所有与项进行逻辑加,即得最简与—或表达式。

在进行化简时,如果用图中真值为0的项更方便,可以用他们来处理,方法和真值取1时一样,只是结果要再做一次求反。 这一部分主要以卡诺图为主。

以下结合例题介绍如何操作

逻辑函数化简

卡诺图化简逻辑函数

卡诺图的画法

F=Σm(1,5,6,7,11,12,13,15)

解题步骤:

- 确定变量数目。

- 画出卡诺图。

- 按照编号填1。

AB\CD | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

00 | 1(1) | |||

01 | 1(5) | 1(7) | 1(6) | |

11 | 1(12) | 1(13) | 1(15) | |

10 | 1(11) |

F=AB+AC+B'C'+A'B'

解题步骤:

- 写出最小项形式:原变量为1,反变量为0.

- 画出卡诺图。

- 按编号填1。

F=AB+AC+B'C'+A'B'

F=11x+1x1+x00+00x

x分别代入0和1,填入。

A\BC | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

0 | 1(x00)(00x) | 1(00x) | ||

1 | 1(x00) | 1(1x1) | 1(11x)(1x1) | 1(11x) |

若两个最小项相邻,则二者仅有一个变量不同。 n变量有n个逻辑相邻项。(每个变量都变一下,能变n下,故有n个)

利用卡诺图化简逻辑函数

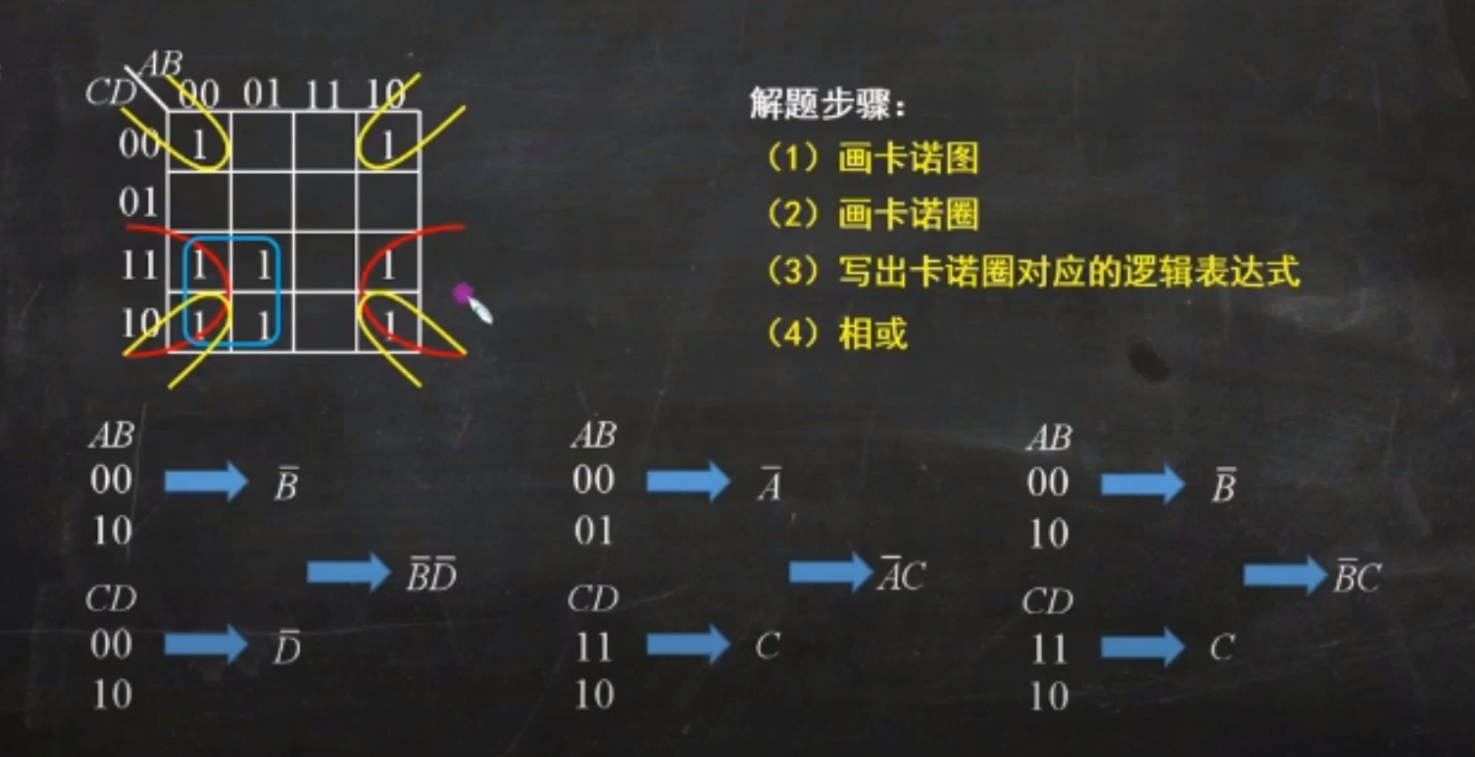

解题步骤:

- 画卡诺图。

- 画卡诺圈。

- 写出卡诺圈对应的逻辑表达式。

- 相或。

卡诺圈先找8个连续的1,然后找4个连续的1,然后找2个,直到所有的1都被圈起来。

- 如果一个变量既出现了0又出现了1,就把它消掉。

- 如果出现了0,就写它的反变量。

- 如果出现了1,就写它的原变量。

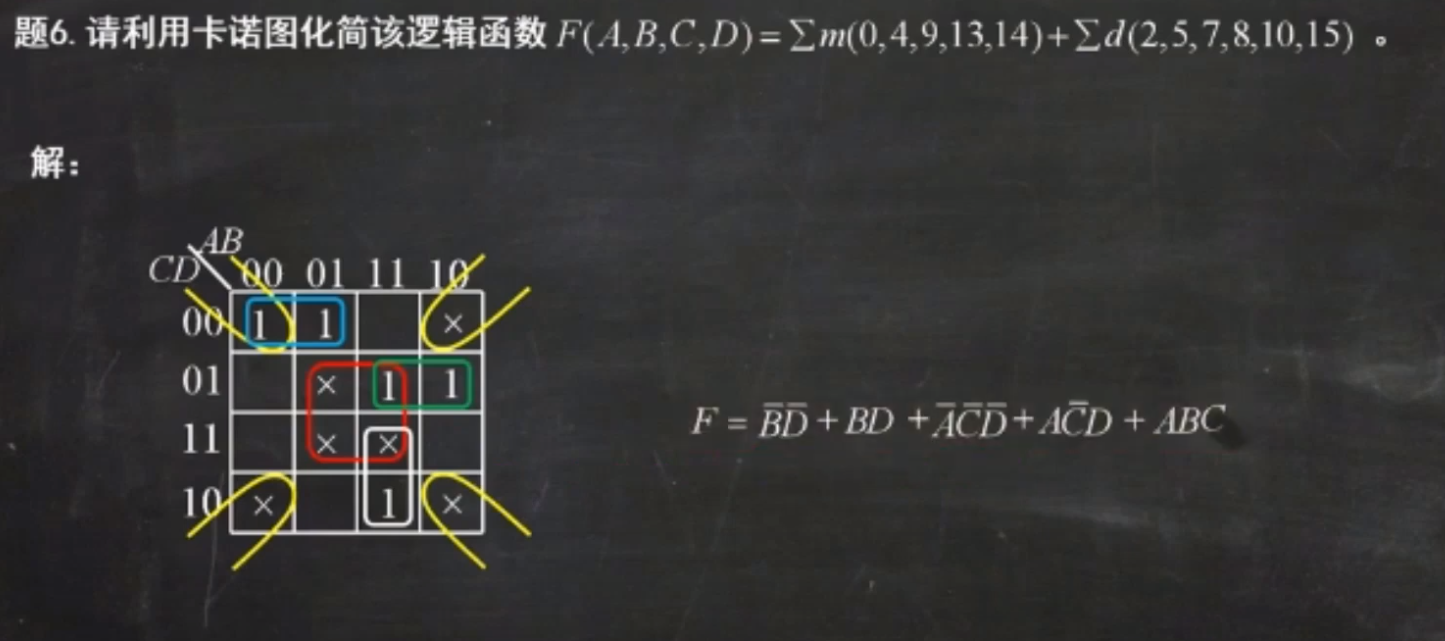

卡诺图化简带有无关项的逻辑函数

F(A,B,C,D)=Σm(0,4,9,13,14)+Σd(2,5,7,8,10,15)

- 利用最小项,在卡诺图中填写1。

- 根据无关项对应编号,在卡诺图中填写0。

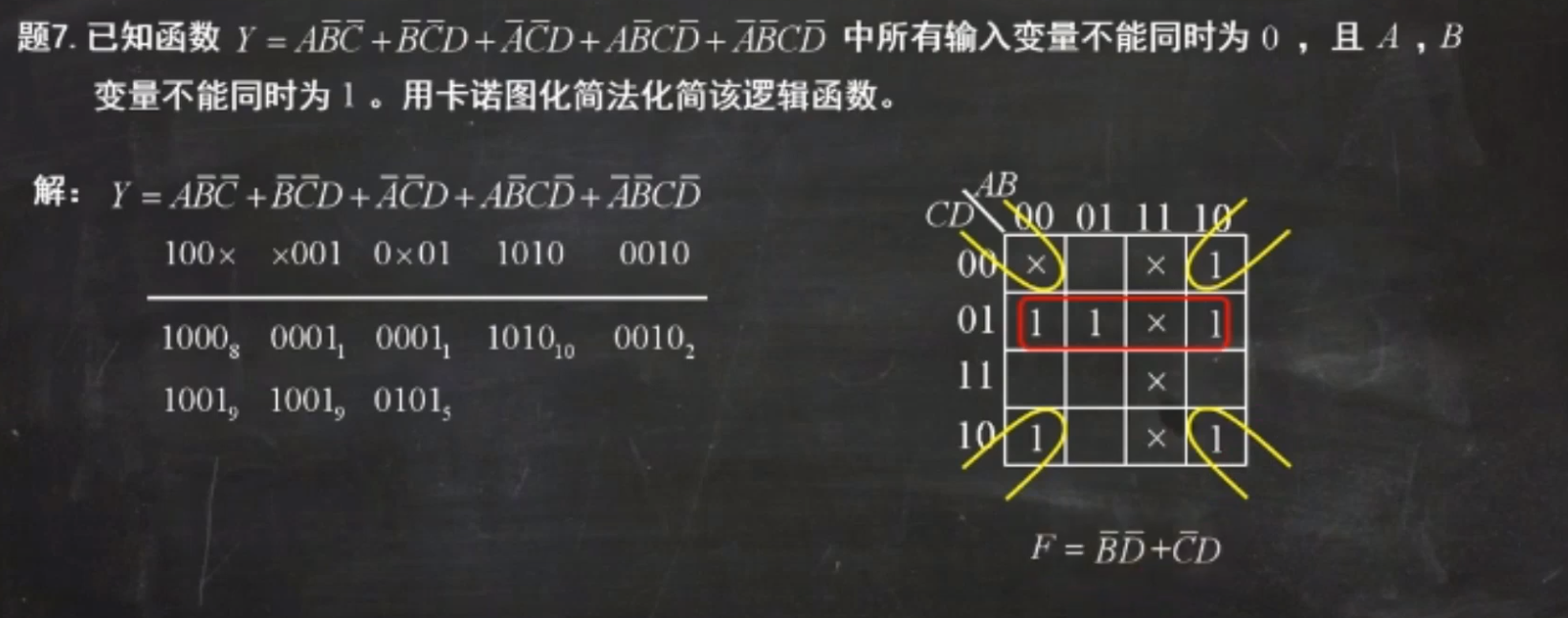

已知函数

Y=AB'C'+B'C'D+A'C'D+AB'CD'+A'B'CD'中所有输入变量不能同时为0,且A,B变量不能同时为1。用卡诺图化简法化简该逻辑函数。

对于题干中的:

- 所有输入变量不能同时为0。

- 且A,B变量不能同时为1。

可以认为是无关项,在卡诺图中填充为x。

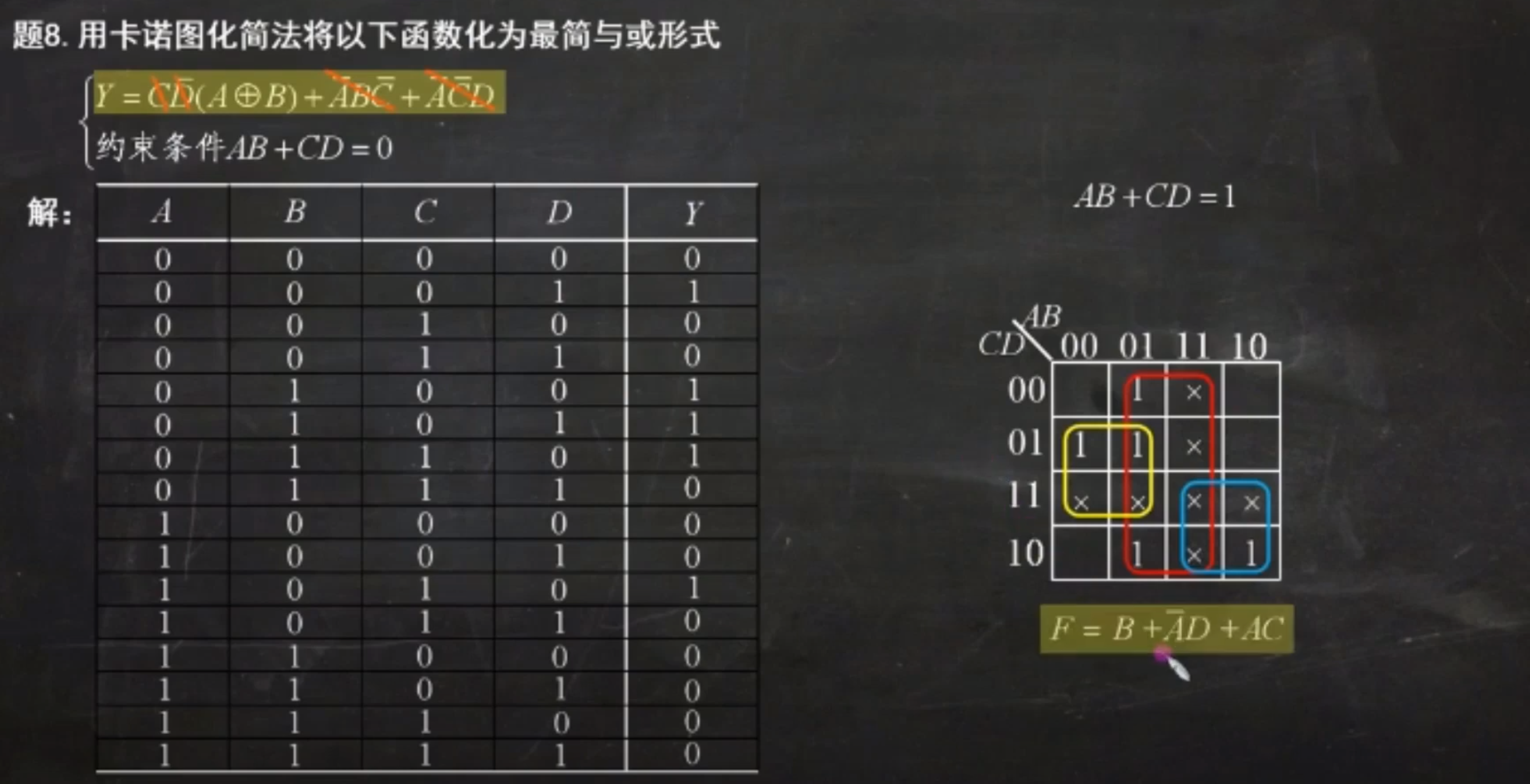

用卡诺图化简法将以下函数化简为最简与或形式 Y=CD’(A⊕B)+A’BC’+A’C’D 约束条件:AB+CD=0

如果逻辑函数比较复杂,无法写出它的最小项,那么就利用真值表来画卡诺图。

- 约束条件是对输入的约束,也就是只有当输入满足条件时,它的输入才是有效的。

- 如果输入不满足条件,那么他就是无关项。

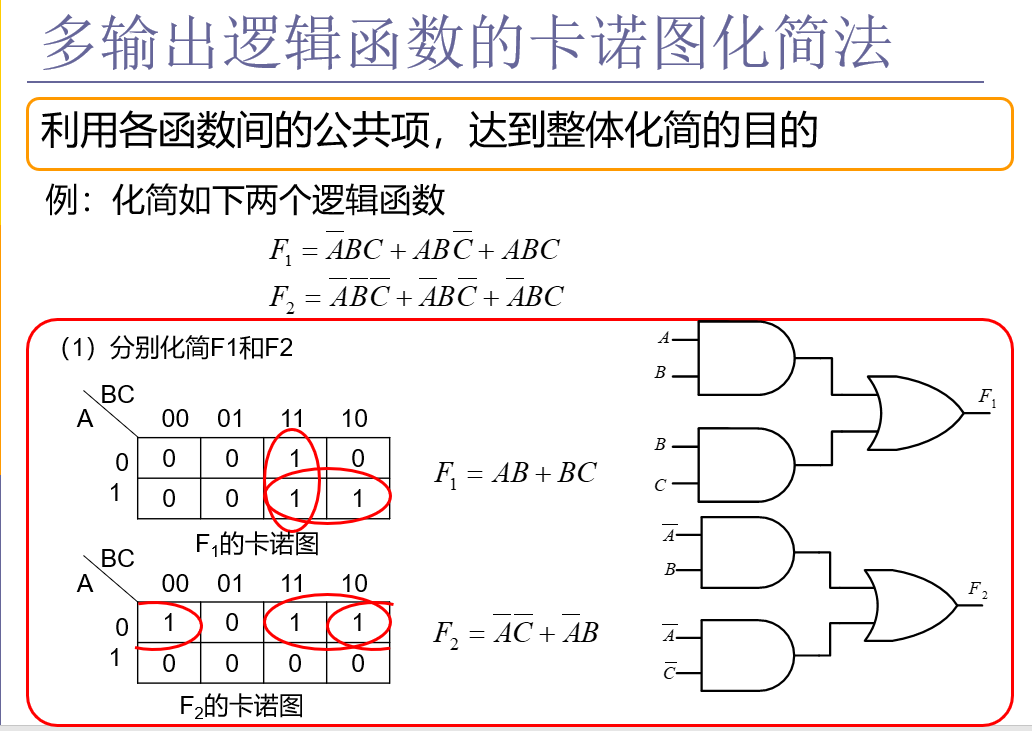

多输出函数化简

以下两幅图片来自博客园的大佬。 在此呈上链接:https://www.cnblogs.com/liuyz1996/p/15700133.html

化简与或&化简或与

前面的例子都是在化简成与或式。 如果要化简成或与式。

- 把0看成1,把1看成0.

- 用圈1的方法圈新1。

- 写出最简与或式,利用反演规则,变成新式子。

- 新式子就是最简或与式。

每个逻辑函数可能有多个最简与或和最简或与!

电路分析与设计

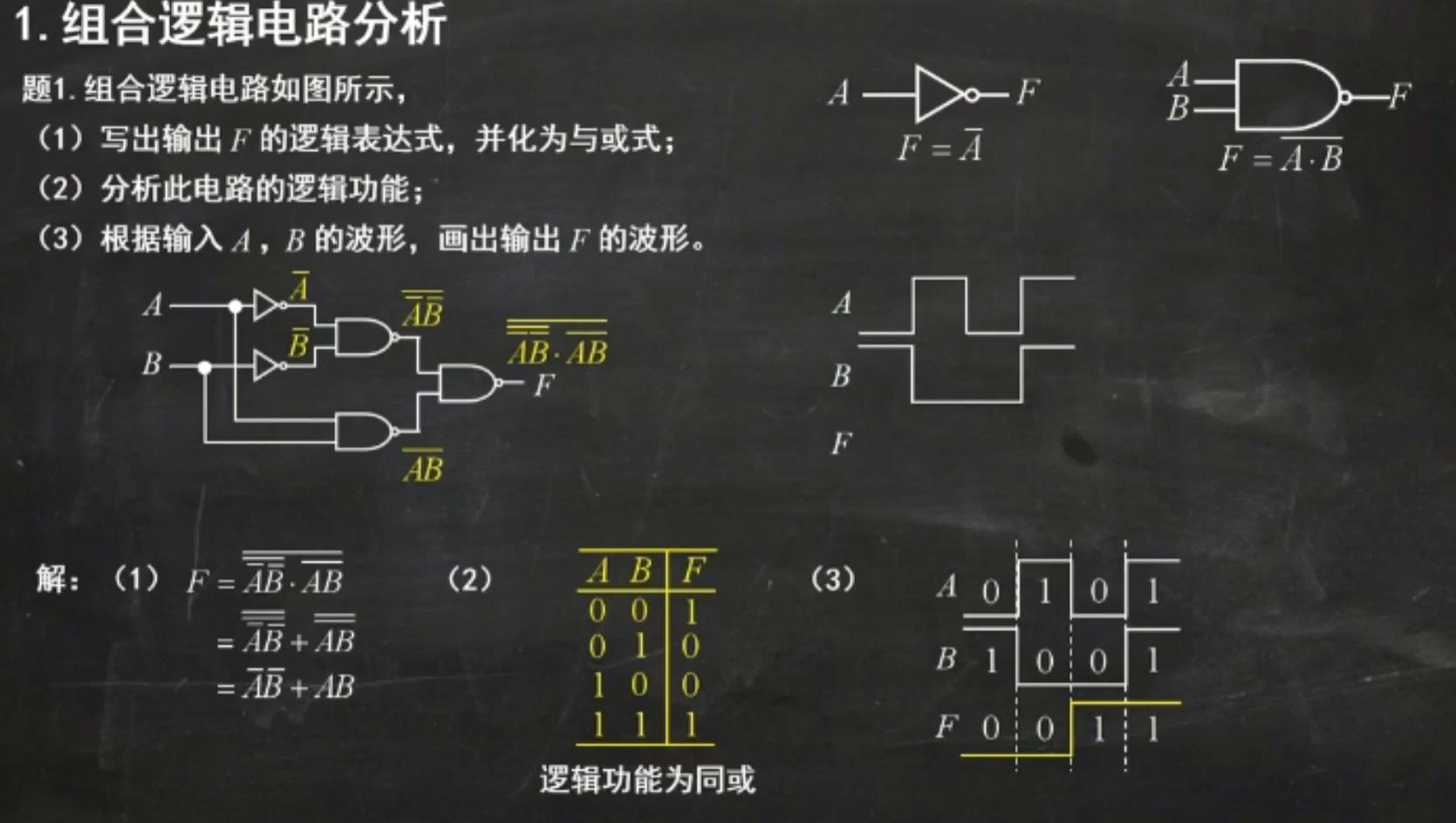

组合电路分析

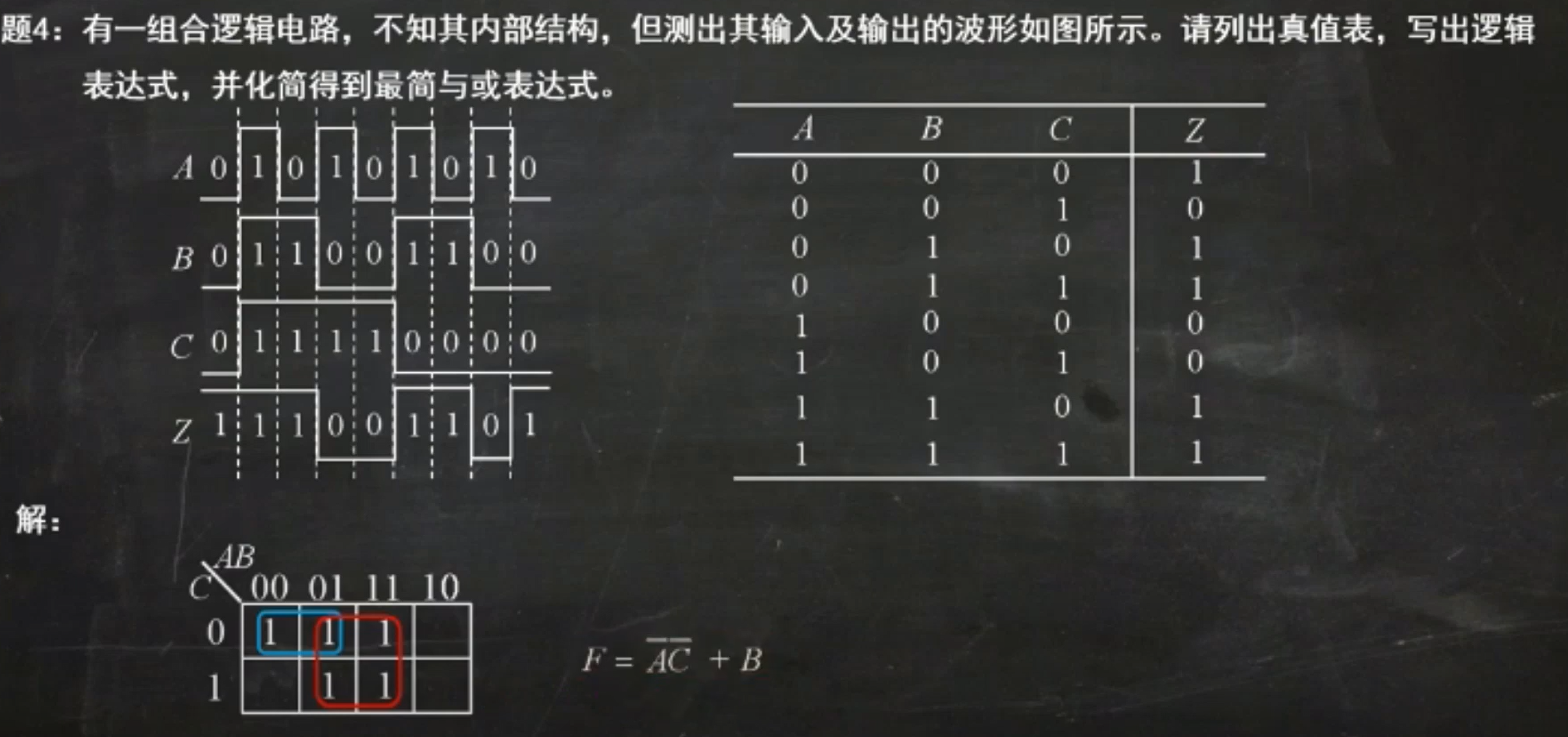

逻辑功能、逻辑表达式、卡诺图、波形之间的相互转换。

同或

A⊙B=A'B'+AB

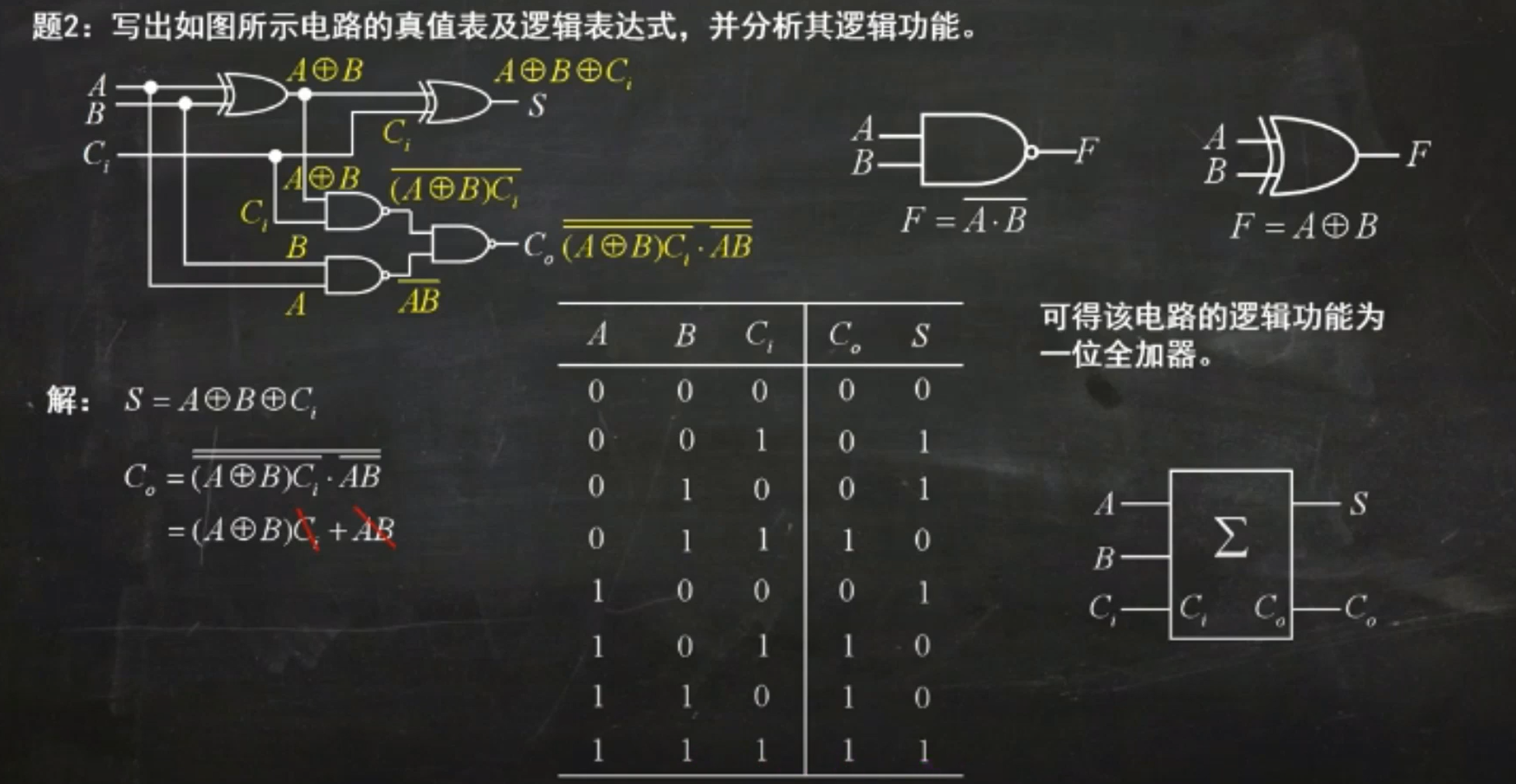

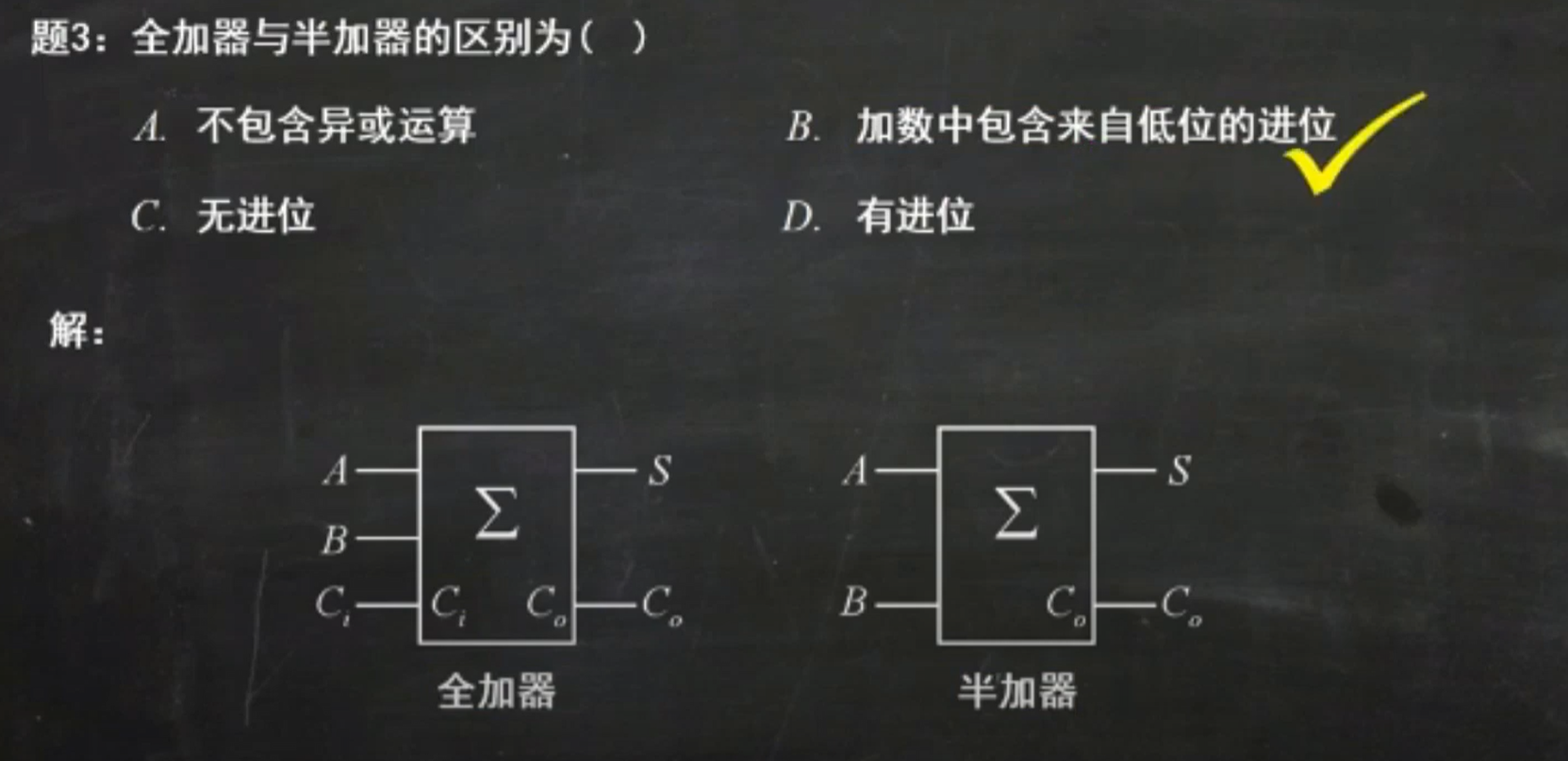

一位全加器 输入中,Ci是来自低位的进位。 结果中,Co是高位,S是低位。

半加器

全加器和半加器的区别就是,全加器包含了来自低位的进位。

根据波形列出真值表、画出卡诺图

组合逻辑电路设计

从逻辑电路图得到逻辑表达式时:

- 从输入依次得到输出。

从逻辑表达式得到逻辑电路图时:

- 从输出依次得到输入。

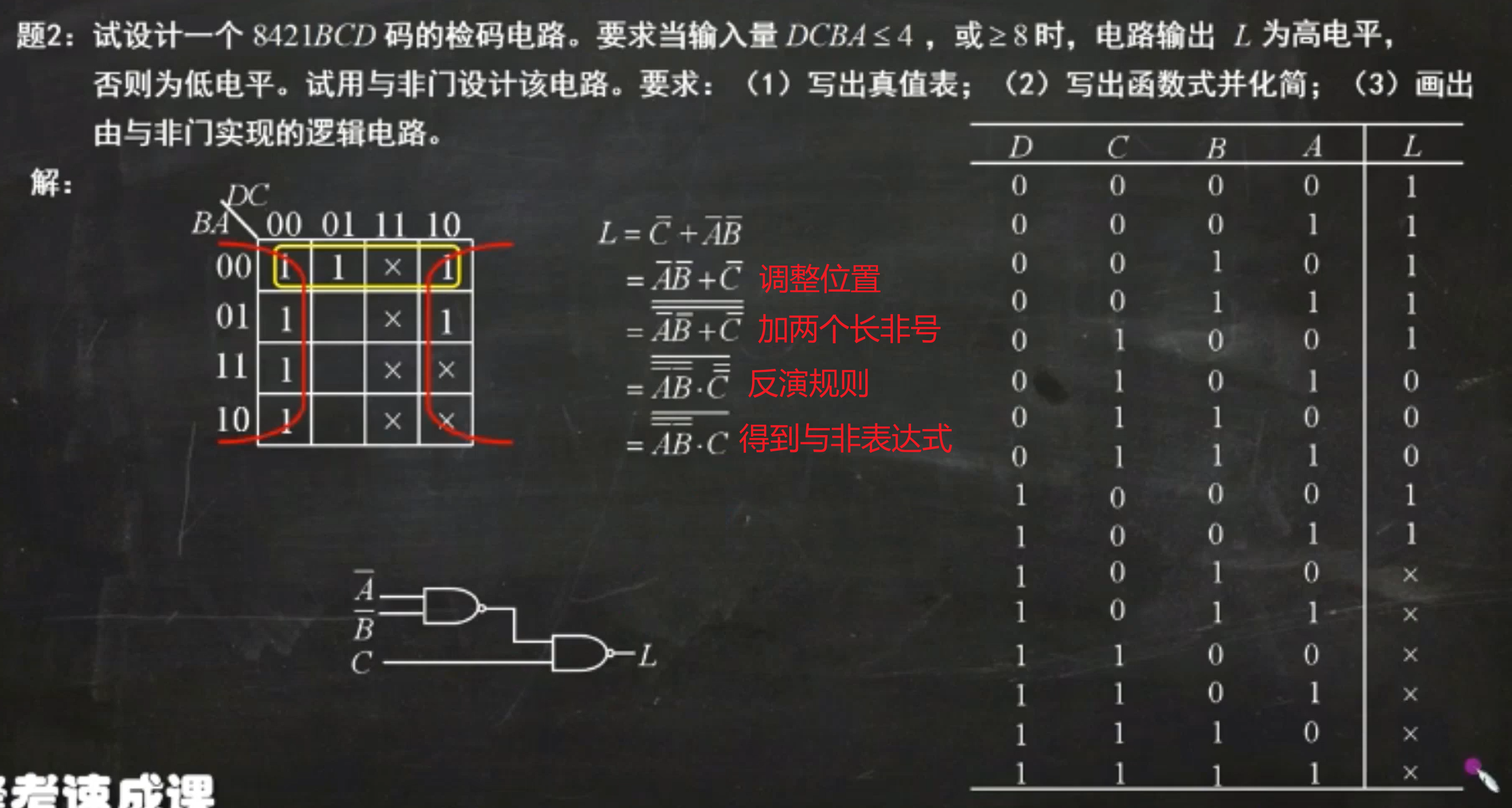

题目中将D作为了高位,我们写真值表时也应该按照题目的顺序来写。 画卡诺图时也应按新的顺序来写。

BCD码只能表示0-9十位数字,所以10-16就是无关项,在卡诺图中填x。 利用与或求与非的步骤:

- 加两个长非号。

- 反演规则。

- 得到与非表达式。

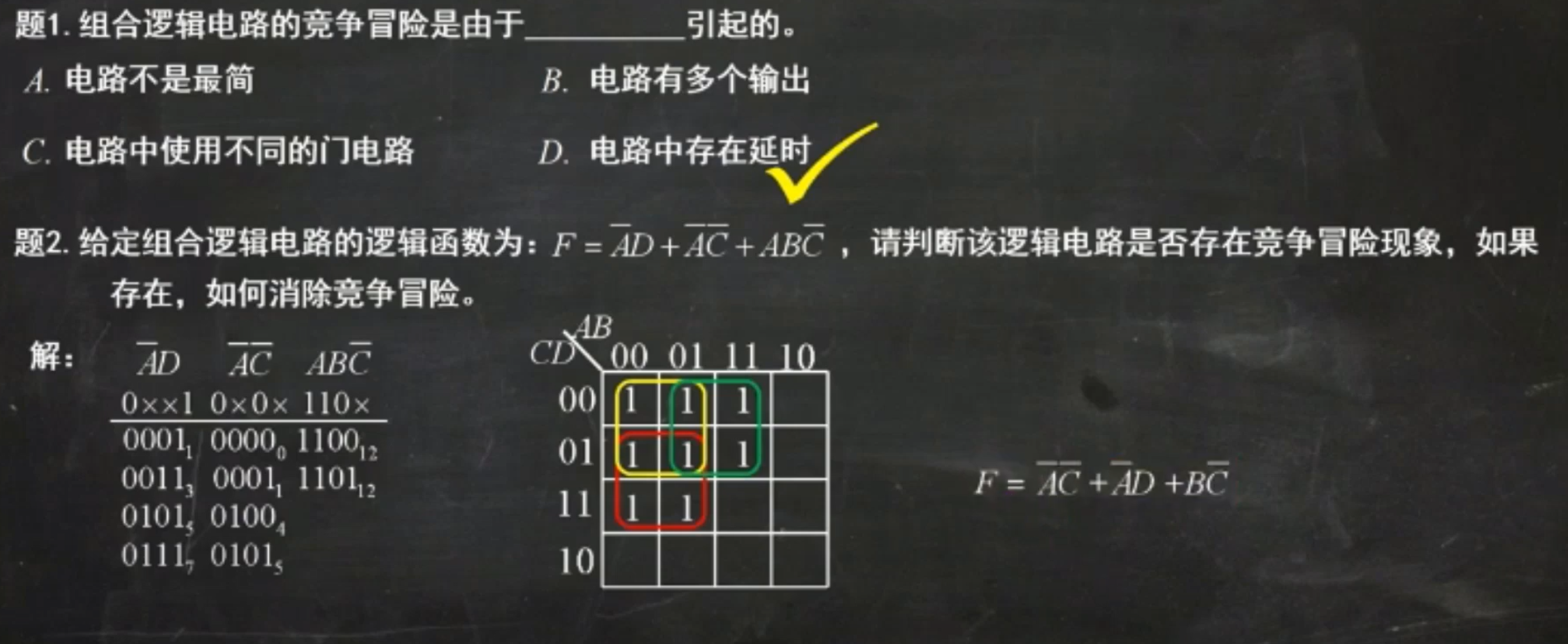

竞争与冒险

组合逻辑电路的竞争与冒险是由于电路中存在延时引起的。 当卡诺圈存在相切时,就存在竞争与冒险。 要消除竞争与冒险,就要把相切的部分给消除掉。变成相交。