Greenberg:AI、Chiplet 与 HBM(长文多图)

Greenberg:AI、Chiplet 与 HBM(长文多图)

全文按AI、Chiplet 、HBM 顺序依次介绍,

- • HBM是AI训练/计算加速场景,解决互联带宽瓶颈的重要组成部分。

- • 标量、矢量、矩阵、张量计算原理

- • 从数据增量理解HBM需求增长

- • Chiplet 作为热门的封装术语,随着AI场景而逐渐备受关注

- • 为什么需要Chiplet?

- • 什么是Chiplet ?

- • HBM的封装技术选型和方案探讨

- • HBM的微观结构、产品参数和市场趋势

AI

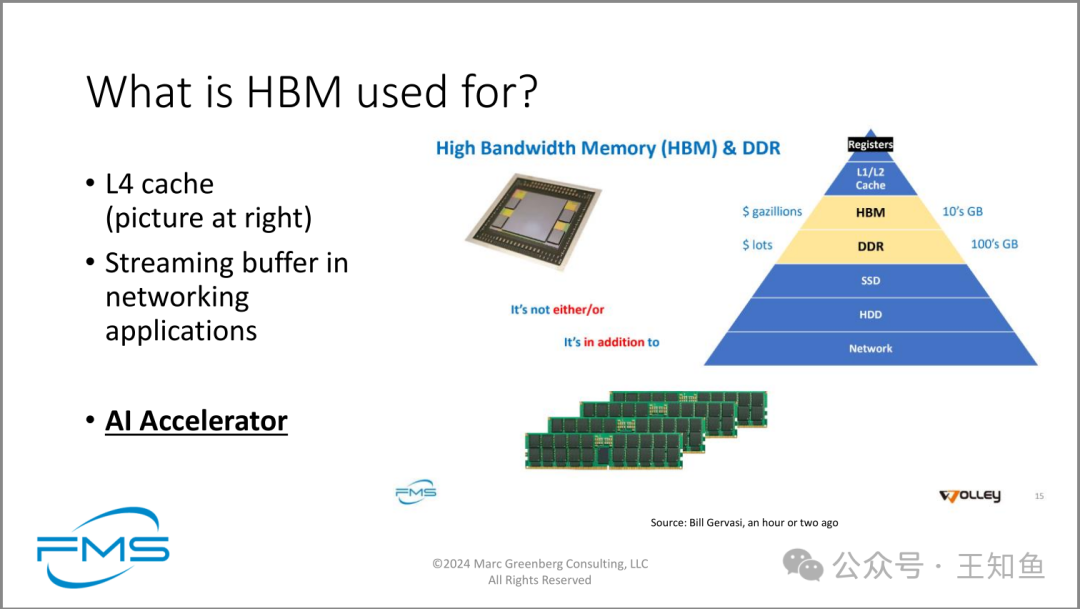

HBM 作为“L4”缓存,持久化网络信息流中的动态数据。

Note:关于L4的说法不必较真,只需了解HBM介于L1/L2 Cache 和DDR内存之间就好了。

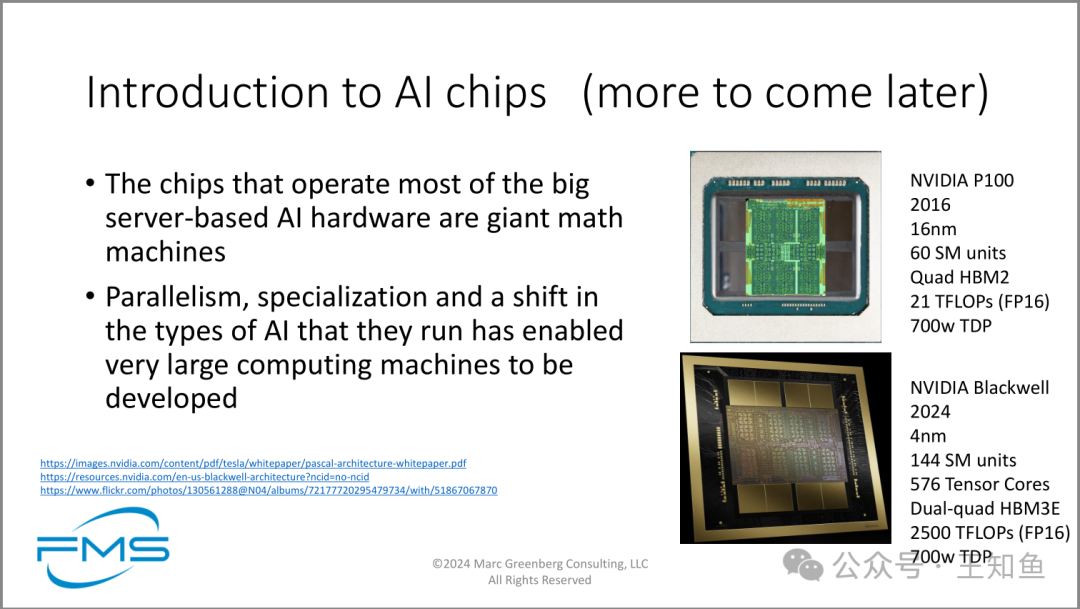

AI处理器快速发展,2016年发布的P100(图右上),到2024年发布的BH200(图右下)含576个张量核,性能从21TF攀升到2500TF。

- 1. 大多数大型服务器AI硬件所使用的芯片是“巨型数学机器”。

- 2. 并行处理、专用计算以及AI类型的变化使得非常大型的计算机器得以快速发展。

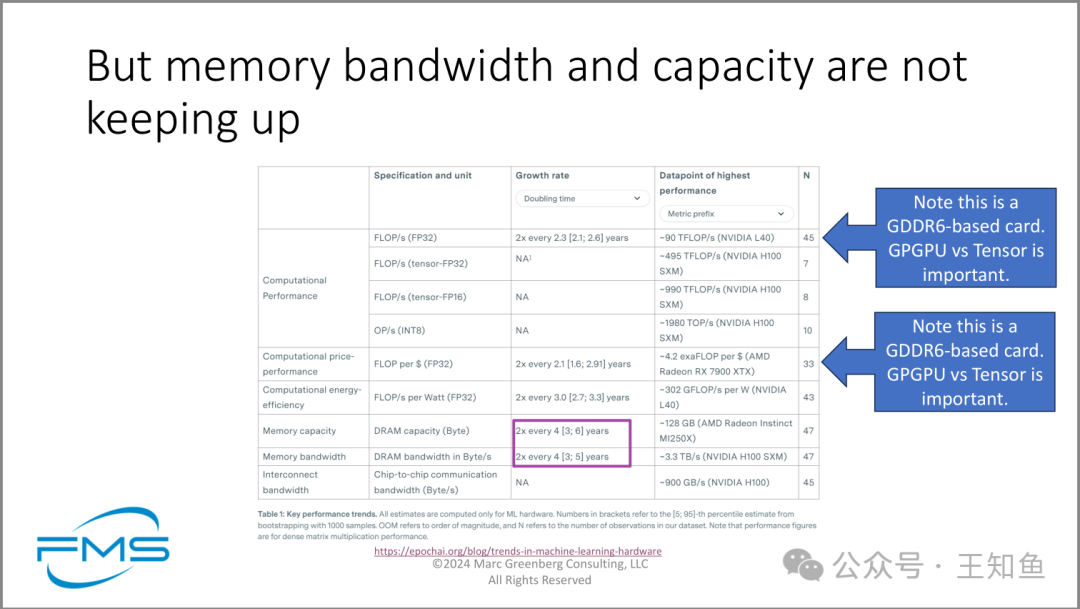

与GPU算力增长速度相比,内存容量、带宽增长速度相对缓慢,导致有效算力减少,内存带宽受限为高昂算力付出额外成本。

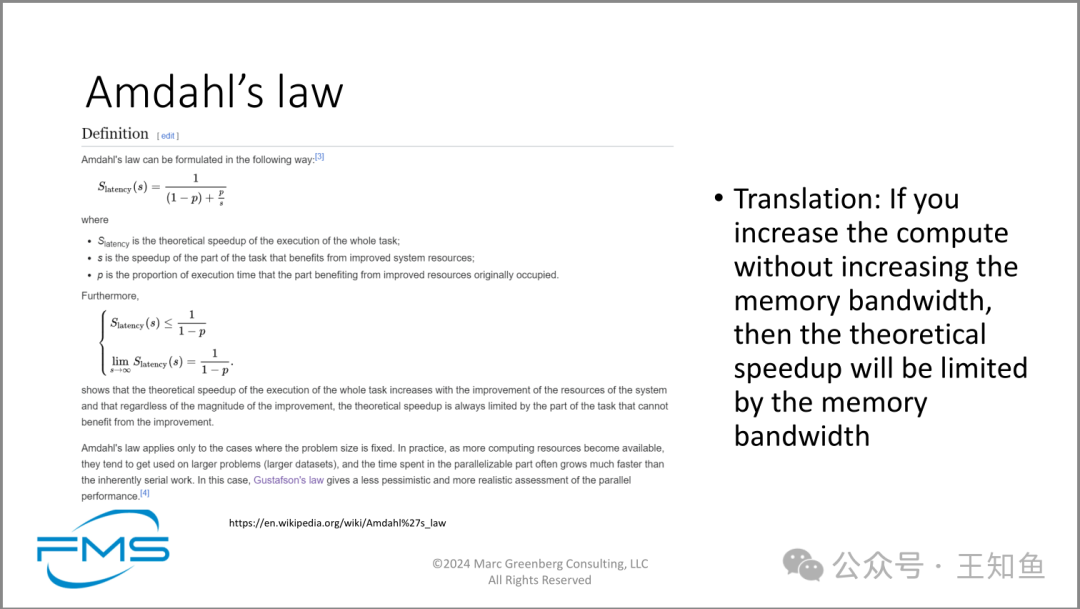

Amdahl 定律

如果增加计算能力而不增加内存带宽,那么理论加速比将受到内存带宽限制。

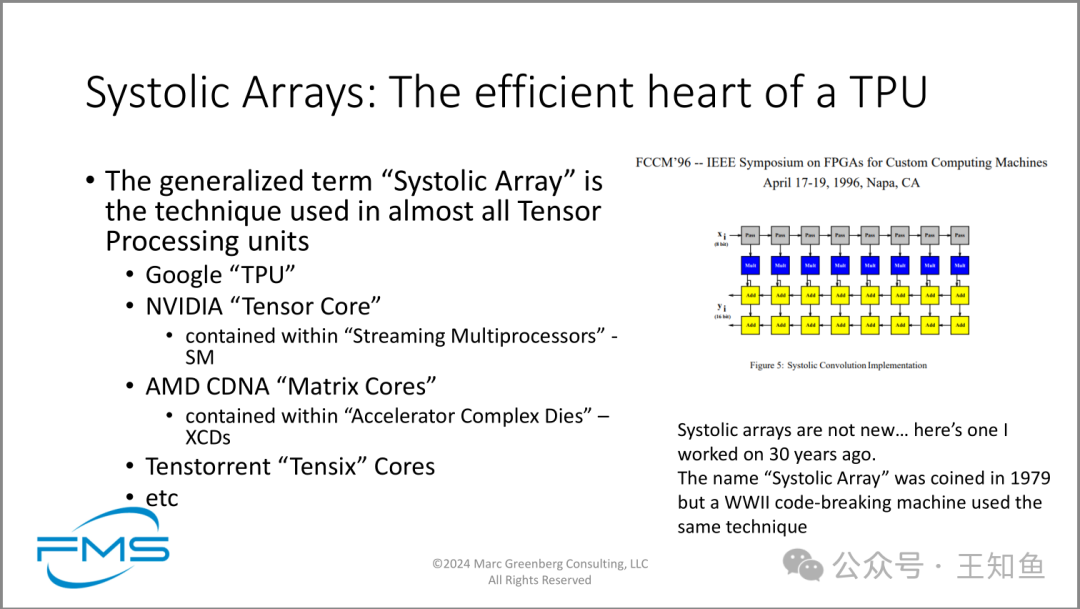

图主要介绍了脉动阵列技术在现代张量处理单元(TPU)中的应用及其历史渊源。

要点总结:

- 1. 脉动阵列是当前主流TPU的核心技术。

- 2. 多家大型科技公司(Google、NVIDIA、AMD、Tenstorrent)都在其AI加速器中使用了这种技术。

- 3. 脉动阵列技术虽然广泛应用于现代AI芯片,但其历史可以追溯到1979年,甚至更早的二战时期。

Systolic Arrays 为什么能在TPU中广泛使用?

① Simple and regular design:可以降低设计成本,通过模块化实现成本与性能成比例; ② Concurrency and communication:由于器件速度的限制,可通过大量并行和降低路由成本加快运算速度; ③ Balancing computation with I/O:I/O制约了最大运算速率,所以需要分解运算以减少I/O,平衡I/O需求、系统规模、存储大小之前的关系,探寻I/O带宽对速度的影响。

推荐阅读:

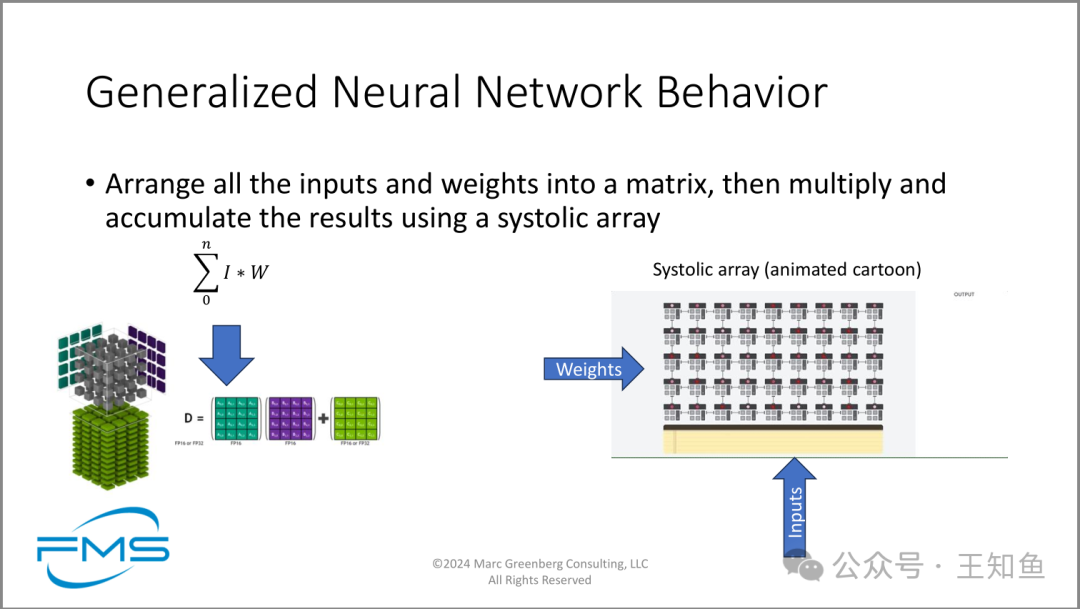

生成式神经网络行为。

凸显脉动阵列的计算框架优势,将所有输入和权重排列成矩阵,从而加速计算过程。

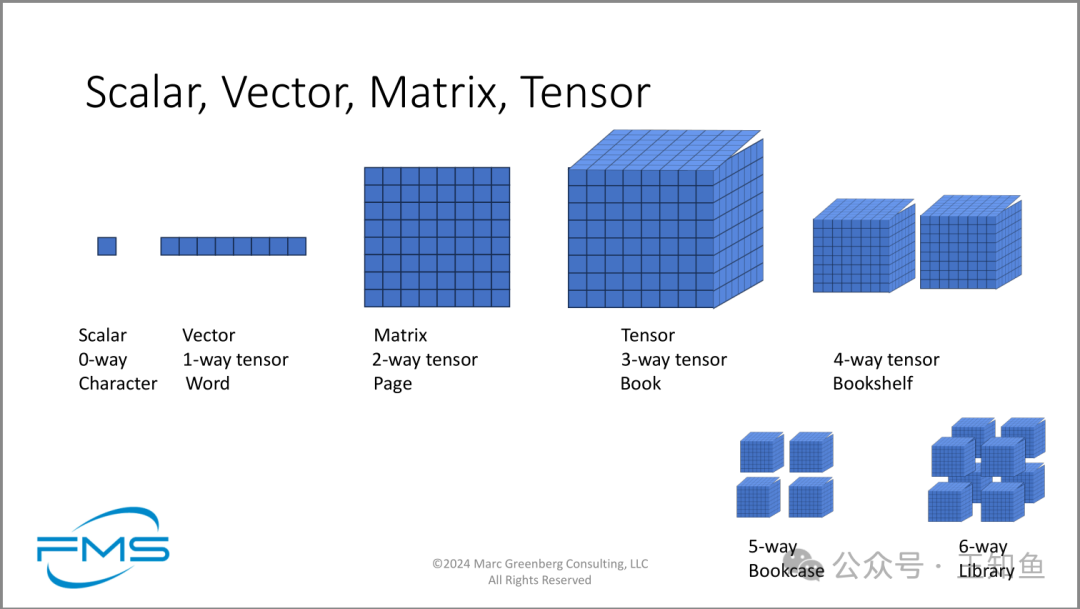

介绍科学计算领域数据的组织方式。

- 1. 标量(Scalar): 0维张量,类比为字符(Character)

- 2. 向量(Vector): 1维张量,类比为单词(Word)

- 3. 矩阵(Matrix): 2维张量,类比为页面(Page)

- 4. 张量(Tensor): 3维张量,类比为书本(Book)

- 5. 4维张量,类比为书架(Bookshelf)

- 6. 5维张量,类比为书柜(Bookcase)

- 7. 6维张量,类比为图书馆(Library)

图对理解数据科学、机器学习和深度学习中常用的数据结构非常有帮助,特别是在解释张量这一关键概念时更为直观。它强调了数据结构的多维特性,以及如何通过增加维度来组织和表示更复杂的信息。

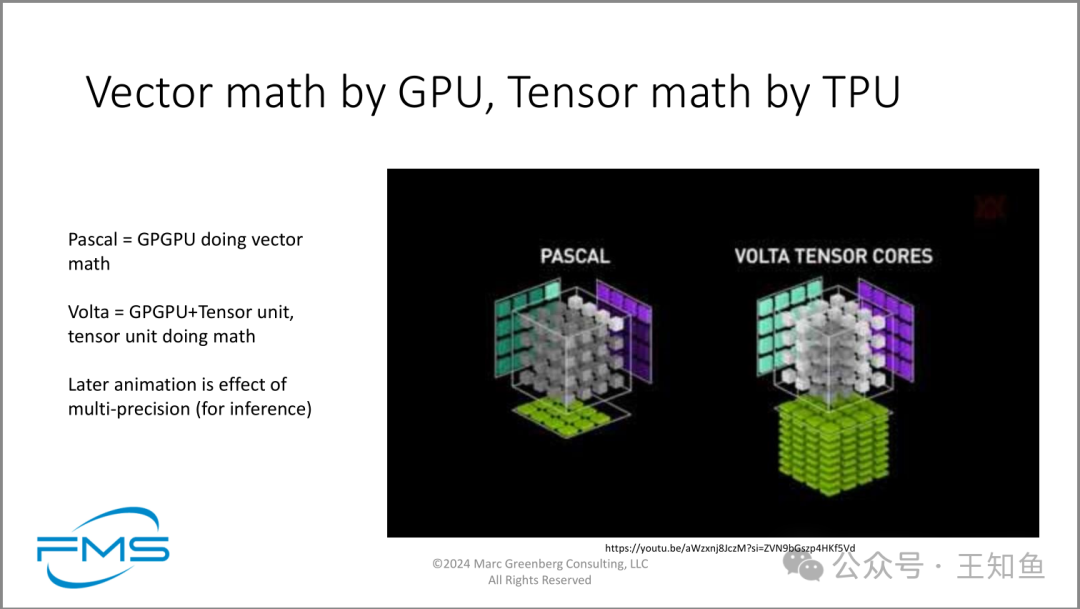

在科学计算领域,矢量计算使用GPU,张量计算使用TPU。

Note:作者似乎在隐喻:当前基于GPU的算力架构可能仅作为中间形态,随着半导体技术发展,基于张量的专用器件才是计算集大成者。

这和演讲人的投资事业相关,他有个TPU的创业公司,详见原材料。

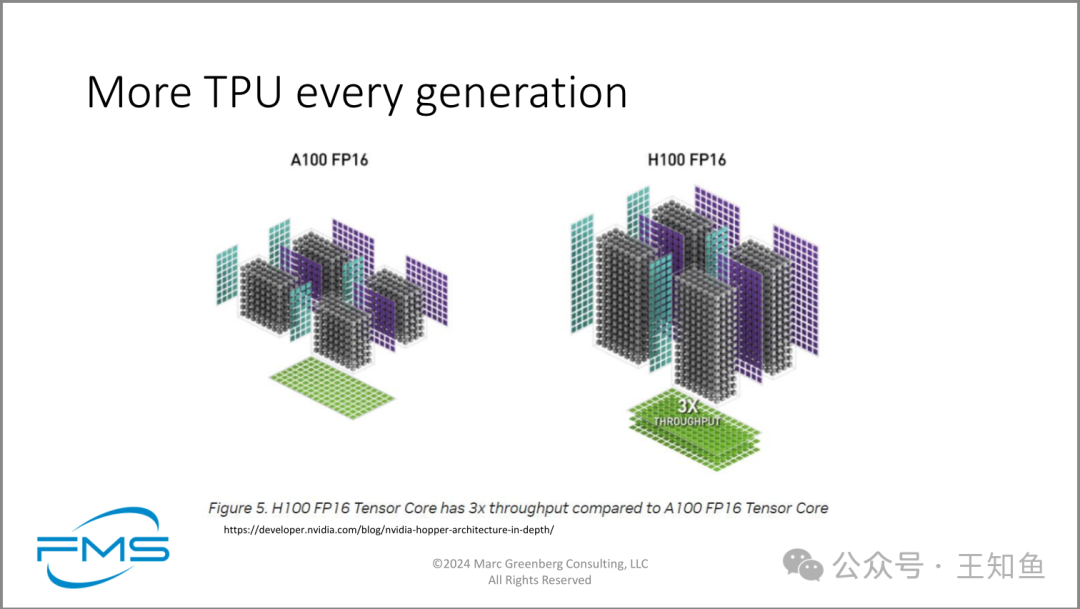

NV A100 和H100 在TPU数量上的差异

H100的TPU张量深度较A100增加,使得数据处理过程整体吞吐量增加为3倍。

主要表达了Google TPU(张量处理单元)从v3到v4版本的技术进步和性能提升。主要内容包括:

- 1. 制程优化:从16nm提升到7nm,使得芯片面积更小,晶体管数量增加。

- 2. 性能提升:峰值TFLOPS从123提高到275,时钟频率从940MHz提升到1050MHz。

- 3. 架构改进:矩阵乘法器数量翻倍,HBM内存带宽提升1.3倍。

- 4. 能效优化:性能/瓦特比有显著提升,其中40%来自工艺进步,其余来自设计优化。

- 5. 扩展性增强:最大规模配置从1024芯片扩大到4096芯片。

- 6. 专用优化:增加了稀疏核心数量,从每芯片2个增加到4个。

- 7. 内存结构优化:增加了片上内存容量和类型。

• AI中使用的处理器是强大的数学运算机器

• 矩阵乘累加(Matrix Multiply-Accumulate,MAC)是大多数AI/ML芯片架构中增长最快的部分

• 经常每一代翻倍

• 数学计算能力的显著增加推动了内存带宽需求的增加

• 生成式AI模型的规模和迭代推动了内存容量的增加

• HBM(高带宽内存)是当前解决内存带宽挑战的方案

Chiplet

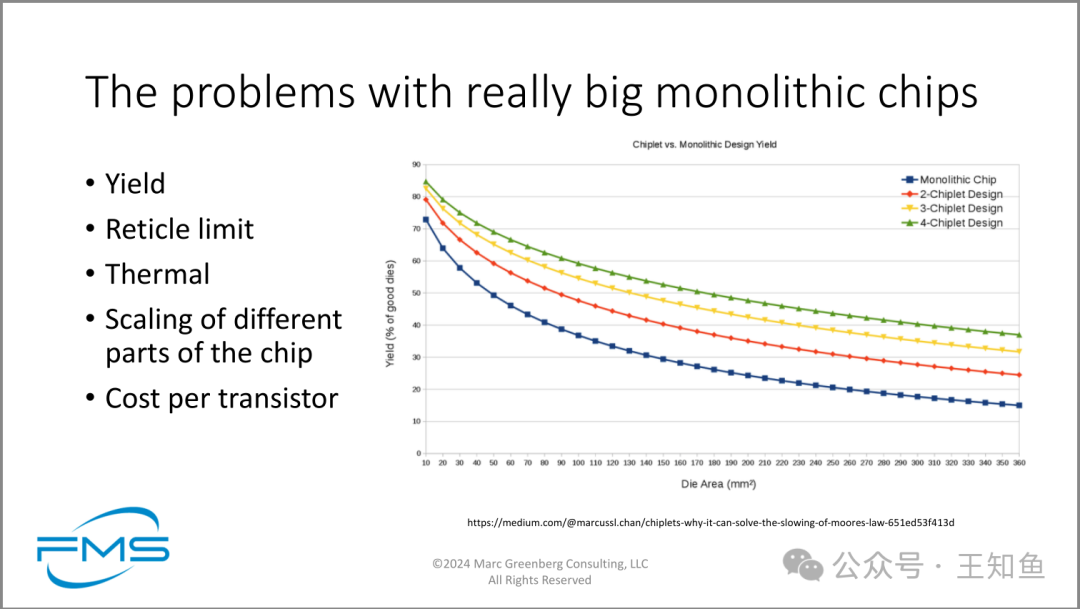

图主要表达了大型单片芯片面临的几个关键问题,并通过图表直观地展示了芯片设计方法对良率的影响。

- 1. 问题列举:图片列出了大型单片芯片面临的五个主要问题,包括良率、光罩限制、热量管理、芯片不同部分的缩放以及每个晶体管的成本。

- 2. 良率对比:图表清晰地展示了单片芯片设计与不同数量Chiplet设计在不同芯片面积下的良率比较。

- 3. 设计趋势:随着芯片面积的增加,所有设计方法的良率都呈下降趋势,但单片设计的下降速度最快。

- 4. Chiplet优势:图表显示,采用Chiplet设计(将大芯片分割成多个小芯片)可以显著提高良率,特别是在大面积芯片中。

- 5. 可扩展性:Chiplet设计展现出更好的可扩展性,随着Chiplet数量的增加,大面积芯片的良率得到进一步提升。

Chiplet是组装/生产大型芯片的可靠方法。

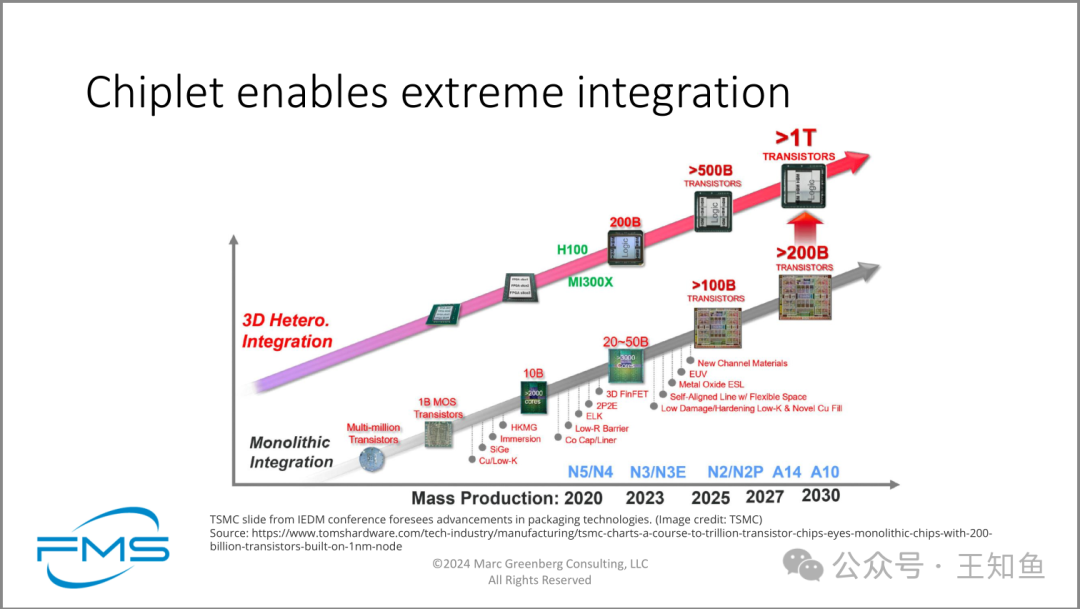

图清晰地展示了芯片集成技术的演进路线,重点强调了以下几个方面:

- 1. 技术演进:从传统的单片集成向3D异构集成的转变,体现了芯片设计和制造的革命性进步。

- 2. 晶体管密度提升:从2020年的10亿晶体管,预计到2030年将突破5000亿,甚至达到万亿级别,显示了摩尔定律的持续推进。

- 3. 制程节点进展:从N5/N4到A10,每个节点都伴随着晶体管数量的显著增加和新技术的引入。

- 4. 关键技术突破:图中列举了多项创新技术,如EUV光刻、3D FinFET、新型沟道材料等,这些都是推动芯片性能提升的关键因素。

- 5. 时间线预测:给出了从2020年到2030年的具体技术发展时间表,为业界提供了清晰的发展路径。

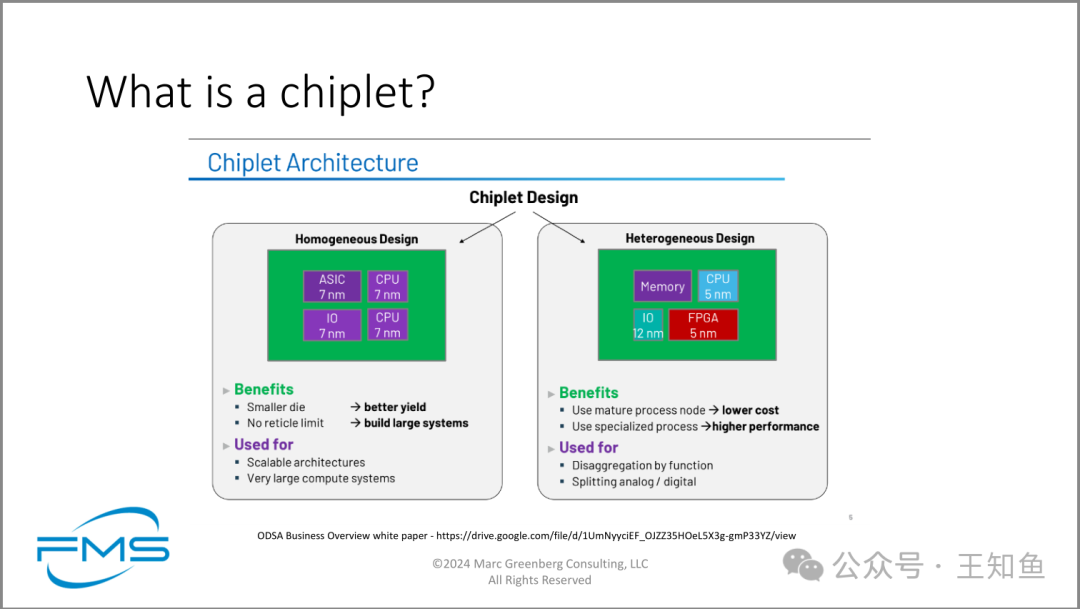

图解释了芯粒(Chiplet)的概念和架构。芯粒是一种新兴的半导体设计方法,将大型复杂芯片分解成较小的功能模块。图片展示了两种主要的芯粒设计方法:同质设计和异质设计。

- • 同质设计使用相同的制程工艺(如7nm)制造所有组件,优势在于更小的芯片面积和更好的良率,适用于构建大型可扩展系统。

- • 异质设计则允许不同组件使用不同的制程工艺,如内存、IO、CPU和FPGA各自采用最适合的工艺节点。这种方法的优势在于可以降低成本(使用成熟工艺)和提高性能(使用专用工艺)。

芯粒技术的主要目的是提高半导体设计的灵活性和效率。同质设计适合大规模计算系统,而异质设计则更适合功能分解和模拟/数字分离的应用场景。

这种设计方法代表了半导体行业应对摩尔定律放缓的一种创新解决方案,使得设计者能够更灵活地组合不同功能模块,优化性能、成本和能耗。

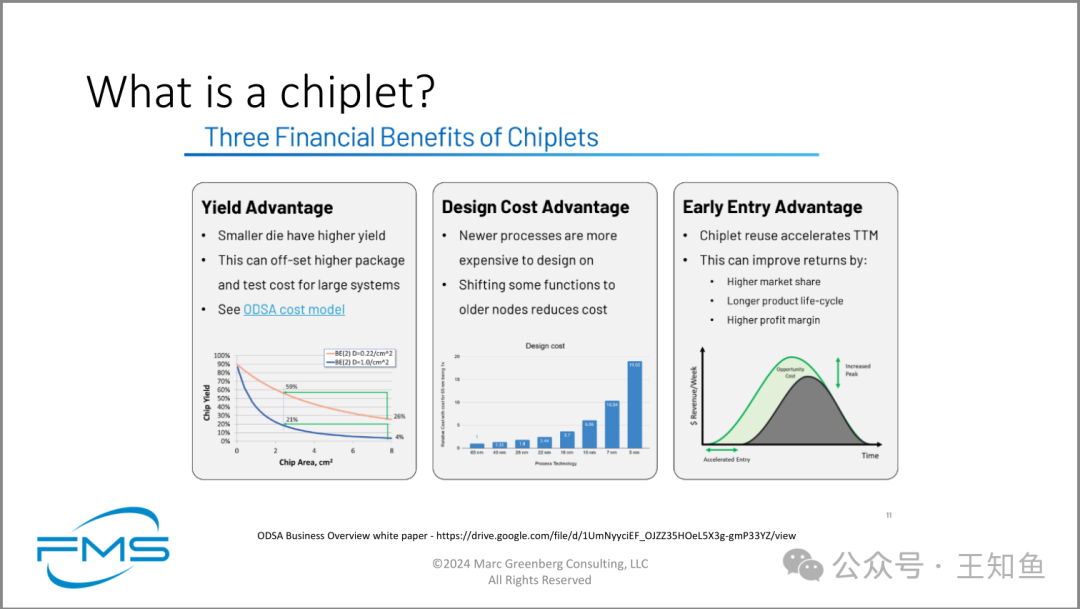

使用芯片小块(Chiplets)技术的三大经济收益:

- 1. 良率优势:较小的芯片具有更高的良率,这可以抵消大型系统中更高的封装和测试成本。良率随着芯片面积的增加而显著下降。

- 2. 设计成本优势:新工艺节点的设计成本较高,而将部分功能转移到较旧的工艺节点可以降低整体设计成本。图表清晰地展示了不同工艺节点的设计成本差异。

- 3. 早期进入市场优势:芯片小块的重用能加快产品上市时间(TTM),从而带来更高的市场份额、更长的产品生命周期和更高的利润率。

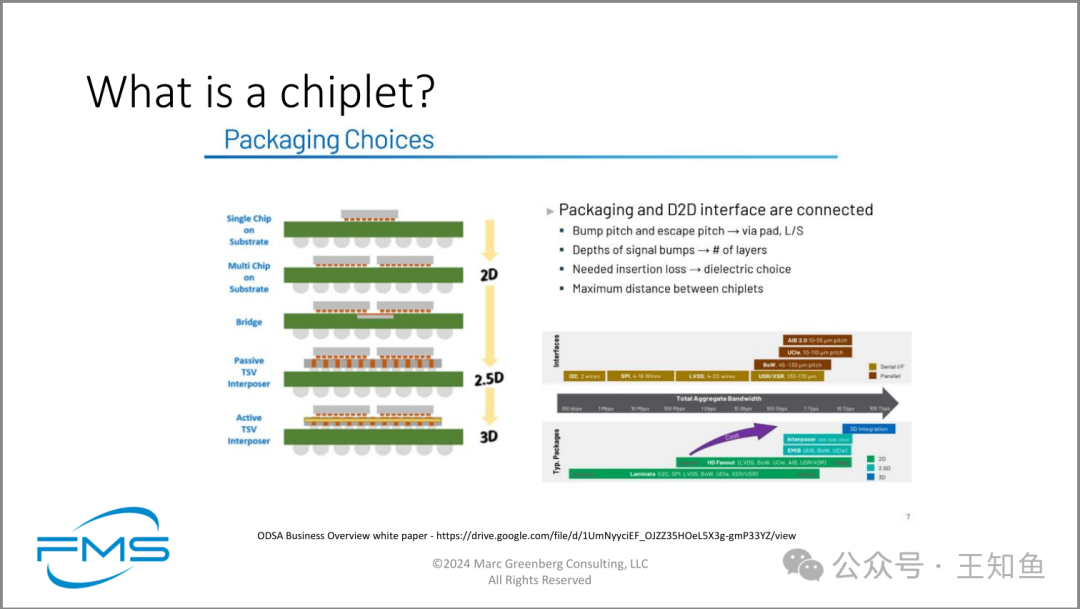

图左 Chiplet 的封装技术路径,从早期的2D横向集成,经过2.5D过渡阶段,到当前3D方案。过程中Package(右下)和接口(右中)尝试了大量新技术。

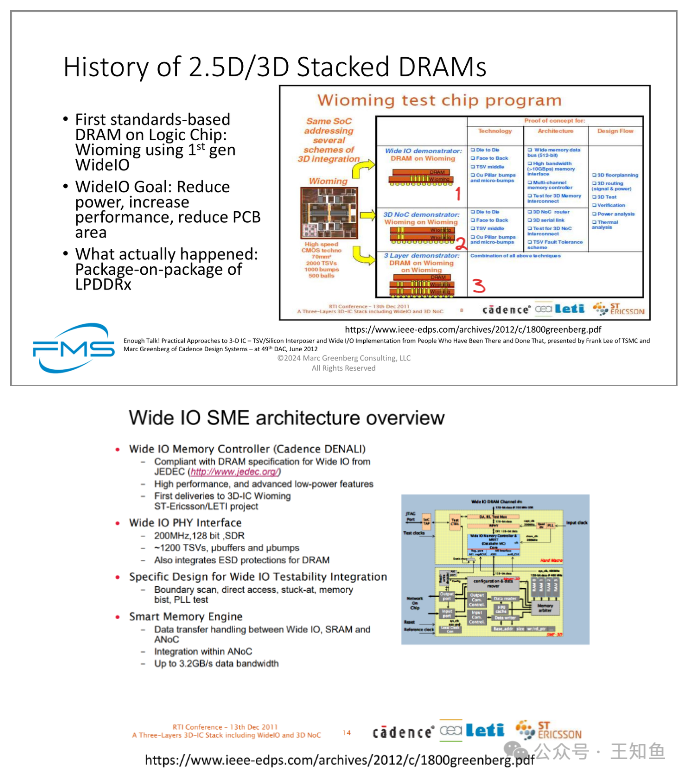

上图,DRAM堆叠技术发展历史(2.5D/3D)

芯片DRAM封装,最早使用的是第一代WideIO技术,即Wioming。过程中经历:

- • WideIO 架构,DRAM on Wioming

- • 3D NoC 架构,Wioming on Wioming

- • 3层架构,DRAM on Wioming on Wioming (结合前两代优势)

关于WideIO WideIO(宽I/O)是一种专为移动设备和嵌入式系统设计的芯片封装技术。它强调的是通过增加I/O接口的宽度来提升数据传输效率和系统性能。

- 1. 宽I/O接口:WideIO技术的核心在于其宽广的I/O接口,这大大增加了数据传输的并行度,从而提高了整体传输速率。对于需要快速读写大量数据的移动设备和嵌入式系统来说,这一点尤为重要。

- 2. 低延迟:由于WideIO采用了更直接的连接方式,减少了数据传输过程中的跳转和转换环节,因此能够显著降低数据传输的延迟时间。这对于提升系统的实时响应能力和用户体验至关重要。

- 3. 节省空间:WideIO技术通过优化封装结构和布线设计,实现了在有限的空间内集成更多的I/O接口。这不仅提高了芯片的集成度,还有助于减小整体设备的尺寸和重量。

下图 是WideIO SME 架构的整体架构图。

WideIO目标:降低功耗,提高性能,减少PCB面积。

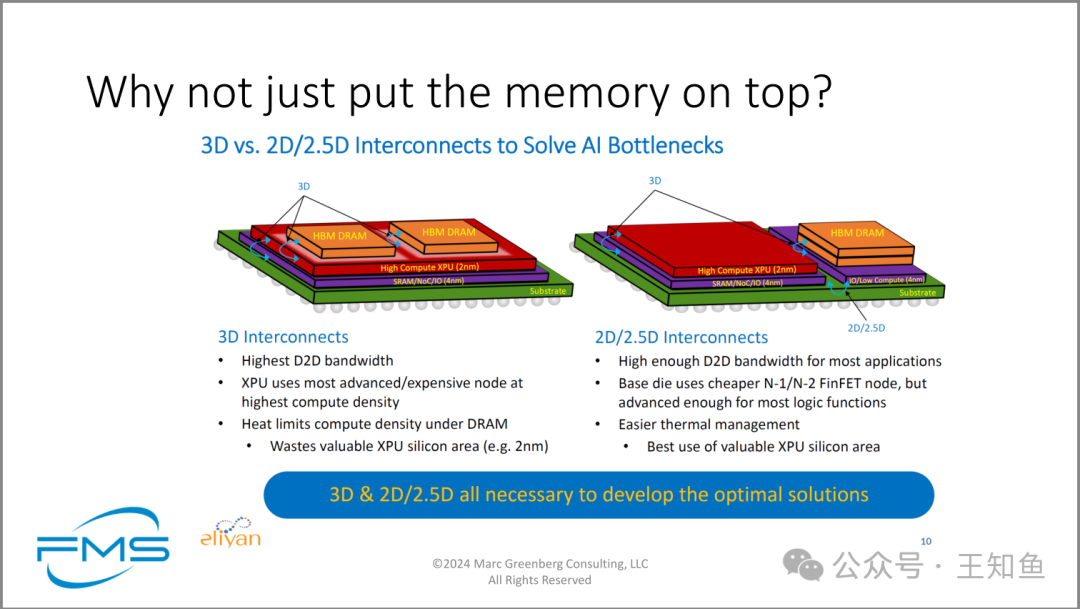

图示 3D(HBM在xPU顶部)与2D/2.5D(HBM 与xPU平行)封装技术对比。

详细描述如下:

3D互连特点: • 最高的D2D带宽 • XPU使用最先进/昂贵的节点,实现最高计算密度 • 热量限制了DRAM下的计算密度 • 浪费宝贵的XPU硅面积(如2nm)

2D/2.5D互连特点: • 对大多数应用来说,D2D带宽足够高 • 基础芯片使用更便宜的N-1/N-2 FinFET节点,但对大多数逻辑功能来说已足够先进 • 更容易进行热管理 • 最佳利用宝贵的XPU硅面积

3D和2D/2.5D两种封装技术,各有优缺点,核心是区分业务场景。对于带宽密集的AI训练场景,3D互联能提供最佳带宽,但HBM的热量也导致计算单元算力无法充分发挥。 相比之下,2D/2.5D能满足常规场景下的带宽需求。

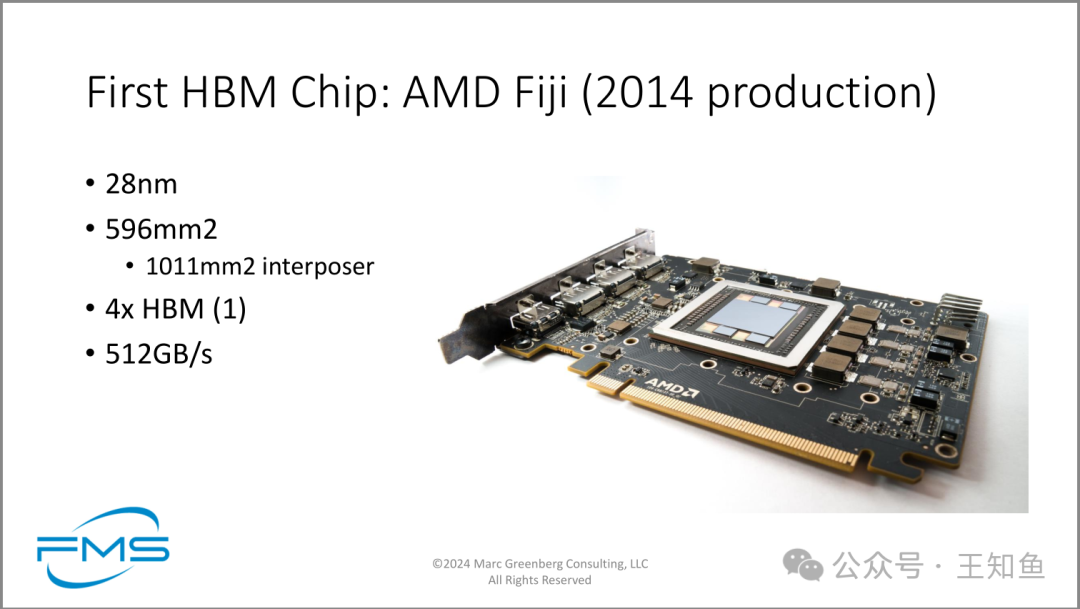

业界首款 HBM芯片 AMD Fiji。

主要特点包括:

- 1. 制程工艺:采用28纳米工艺

- 2. 芯片尺寸:596平方毫米,配备1011平方毫米的中间层(interposer)

- 3. 内存配置:使用4个第一代HBM内存堆叠

- 4. 内存带宽:高达512GB/秒

关于 中间层(interposer)

- 1. 定义:中间层是一种硅基或有机材料制成的薄层基板,置于主芯片(如GPU)和内存芯片(如HBM)底部(下数第3图可见)。

- 2. 功能:

- • 连接桥梁:它作为主芯片和HBM内存之间的互连平台,提供高密度、短距离的电气连接。

- • 信号传输:通过中间层上的微小导线,实现GPU和HBM之间的高速、低延迟数据传输。

- • 热管理:有助于分散和管理芯片产生的热量。

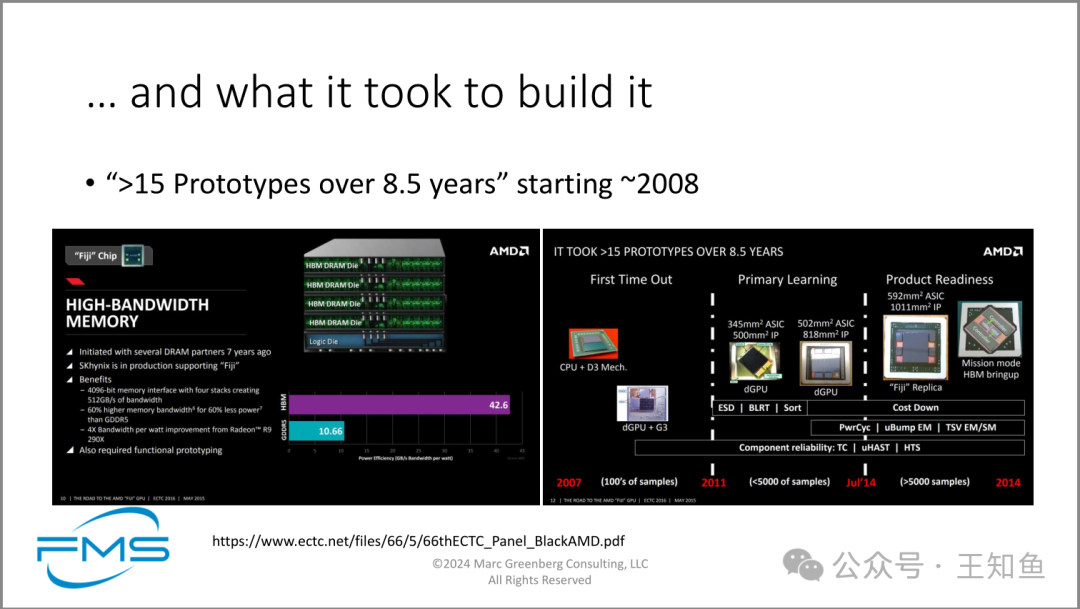

历经8.5年15次原型设计。

提供高效传输带宽的背后,HBM研发设计需要大量投入,右图展示15次流片过程的GPU。

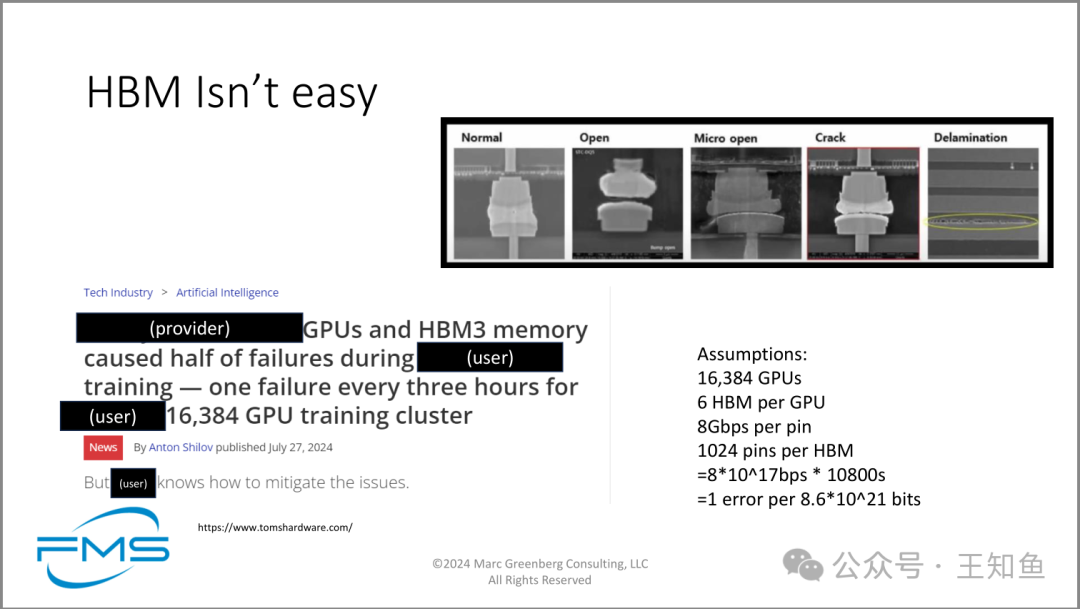

HBM的设计、生产并不容易。

图主要表达了高带宽内存(HBM)技术在实际应用中面临的挑战和可靠性问题。具体来说:

- 1. 可靠性问题:图片顶部展示了HBM芯片可能出现的各种物理损坏状态,从正常到完全分层,说明HBM在使用过程中可能遇到的结构性问题。

- 2. 实际案例:新闻标题揭示了一个大规模GPU训练集群中,GPU和HBM3内存导致了频繁的故障,平均每三小时就有一次。

- 3. 规模和复杂性:假设部分列出了集群的规模(16,384 GPUs)和HBM的详细参数,突出了系统的复杂性和潜在的故障点。

HBM

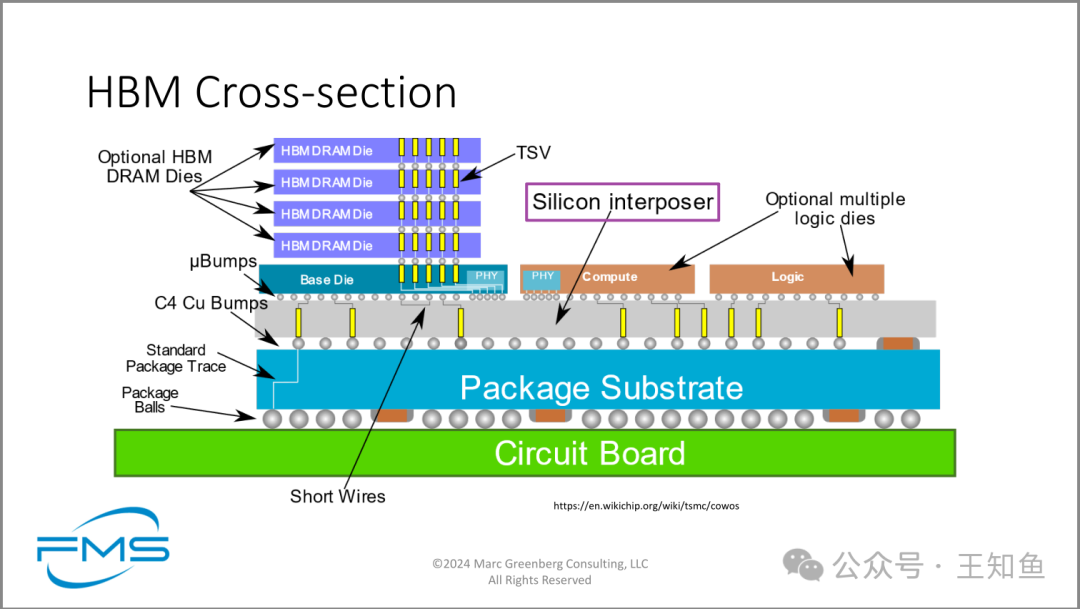

HBM断面结构示意图。

在大芯片上通过Chiplet工艺集成HBM、计算、逻辑单元,留意图中框出的 interposer 中间层。

结合前面的介绍,示意图采用的是2D/2.5D封装技术。

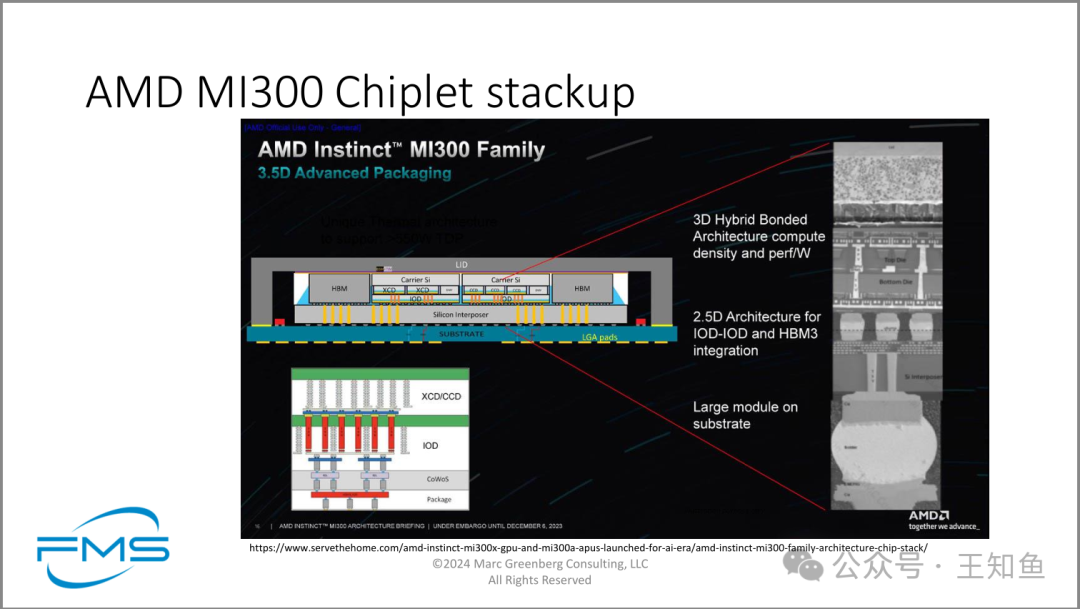

AMD MI300 截面电子显微图。

足见高端芯片内部复杂结构,需要大量材料和制造工艺创新。

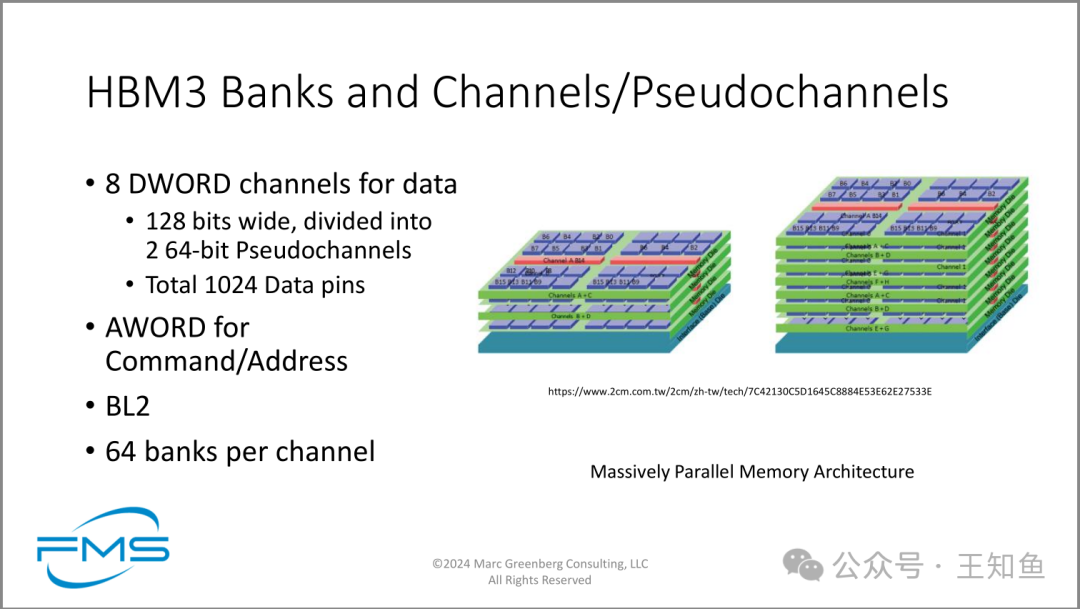

图主要表达了HBM3(High Bandwidth Memory 3)的内部结构和特性:

- 1. 通道结构:HBM3采用8个DWORD(双字)通道来传输数据,每个通道128位宽,进一步分为2个64位的伪通道(Pseudochannels)。

- 2. 数据传输能力:总共提供1024个数据引脚,这意味着巨大的并行数据传输能力。

- 3. 命令和地址传输:使用AWORD专门用于传输命令和地址信息。

- 4. 突发长度:采用BL2(Burst Length 2)模式,这有助于提高数据传输效率。

- 5. Bank数量:每个通道包含64个banks,这种大规模的bank并行性能够显著提高内存访问效率。

- 6. 架构特点:图中强调了"大规模并行内存架构",这是HBM3的核心设计理念。

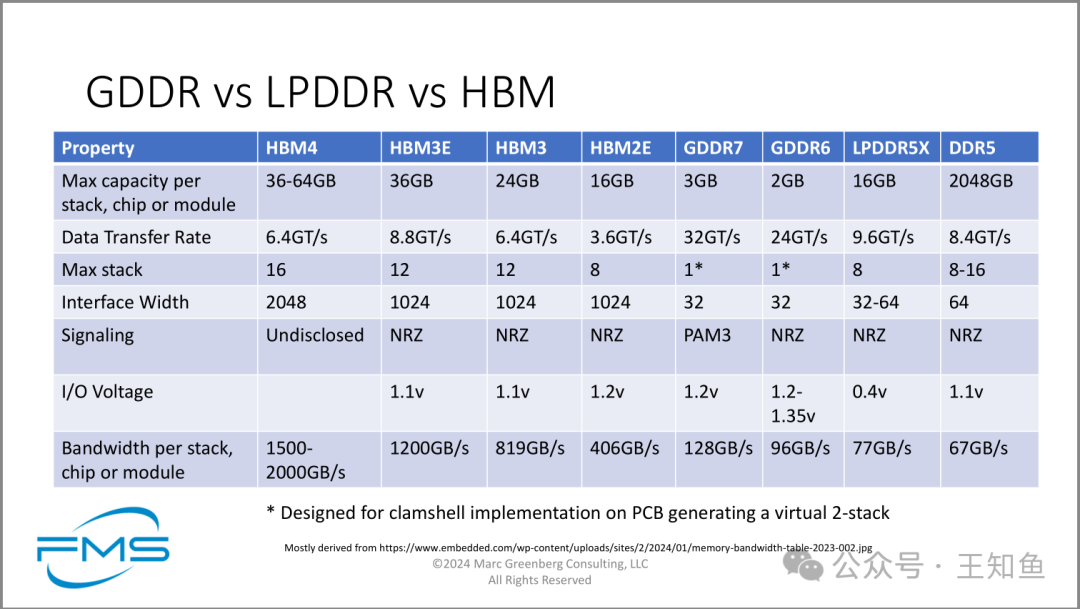

HBM与GDDR/LPDDR/DDR参数对比

- • HBM单位引脚的数据传输速率不及其他DDR,但 Interface Width(2048) 明显高出其他使得总带宽显著领先(这也是为什么在HBM领域,先进封装技术尤为重要,其他DDR产品是通过PCIe外联引脚接入xPU单元)。

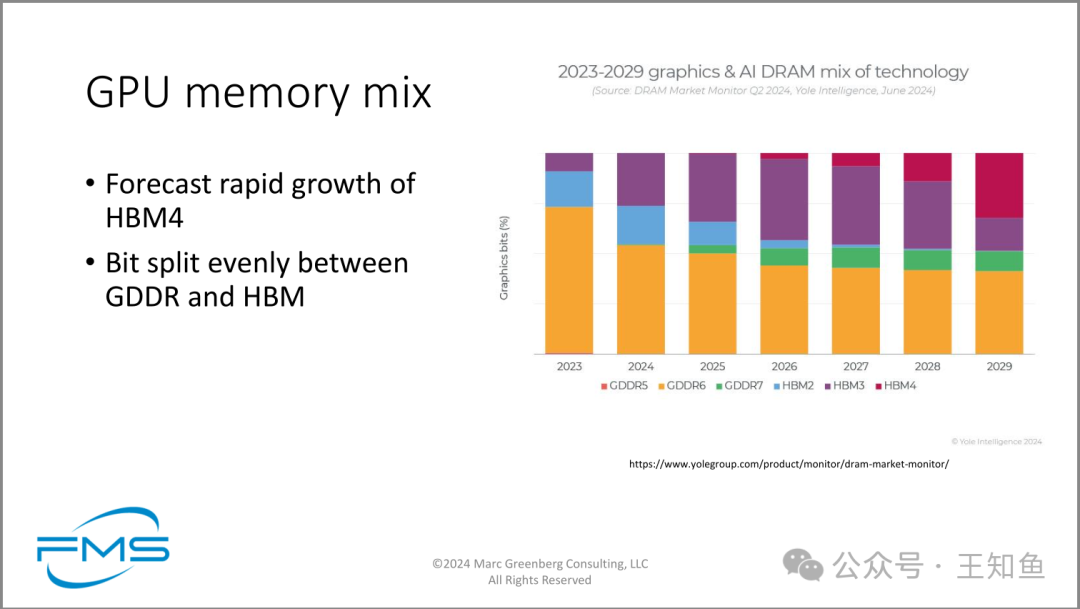

未来GPU内存市场预测

- 1. HBM4技术的快速增长:正如图中所述,HBM4技术预计将在未来几年内快速增长。从2027年开始出现,到2029年已占据相当大的市场份额。

- 2. 内存技术多样化:图表显示了多种GPU内存技术并存的情况,包括GDDR5、GDDR6、GDDR7以及不同代的HBM技术。

- 3. GDDR和HBM技术的平衡:图中提到"位分割在GDDR和HBM之间均匀分布",这表明这两种主要的GPU内存技术将在市场中保持相对平衡的地位。

- 4. 技术迭代:可以观察到较旧的技术(如GDDR5)逐渐被淘汰,而新技术(如GDDR7和HBM4)逐步引入和普及。

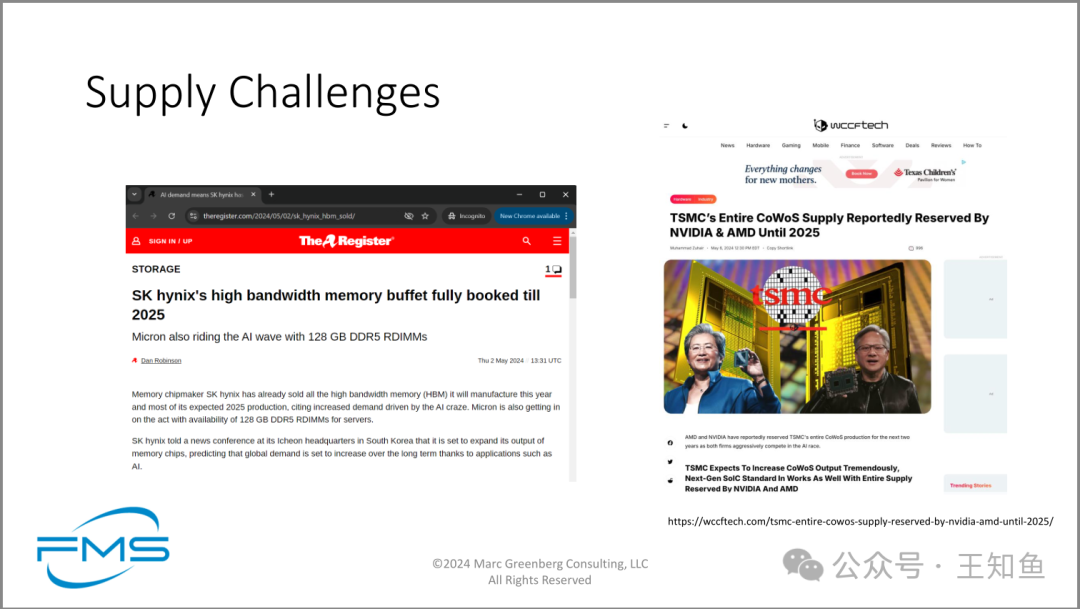

供应链挑战

- • 左图显示SK hynix的高端HBM产能已全被预定,直到2025年。

- • 台积电 CoWoS产能被Nvidia和AMD全揽

总结

- 1. AI场景HBM需求:数学计算能力的显著增加推动了内存带宽需求的增加;生成式AI模型的规模和迭代推动了内存容量的增加;HBM(高带宽内存)是当前解决内存带宽挑战的方案

- 2. Chiplet与HBM封装选型:采用Chiplet设计(将大芯片分割成多个小芯片)可以显著提高良率,特别是在大面积芯片中;对于带宽密集的AI训练场景,3D互联能提供最佳带宽,但HBM的热量也导致计算单元算力无法充分发挥。

- 3. HBM发展趋势:专用计算高速带宽需求不断增加,HBM技术快速发展,先进生产能力掌握在SKhynix及TSMC等有限厂商手中。