IMEC:300mm硅光平台的64Gb/s O波段GeSi电吸收调制器EAM

IMEC:300mm硅光平台的64Gb/s O波段GeSi电吸收调制器EAM

光芯

发布于 2025-04-08 20:53:38

发布于 2025-04-08 20:53:38

IMEC最近在JLT发了个文章,介绍了他们在300 mm硅光平台上的O波段GeSi QCSE EAM的进展。高速EAM是CPO/OIO调制方案的一个重要选项,比MZ小,带宽密度大,比微环稳定,控制简单。但目前做得比较好的单次外延GeSi EAM都只能工作在L波段,与短距O波段标准不兼容,而通过多层堆叠的Ge/GeSi多量子阱结构,利用量子斯塔克效应实现光吸收边带实现强烈的光谱漂移,可以实现工作在O波段的GeSi EAM,但技术难度也挺大的。

imec是做GeSi EAM最厉害的了,无论是L波段的还是O波段的,但也还没大规模应用。最新的这篇O波段EAM文章本身来说实现的指标一般,插损、消光比和工作波长范围都还达不到实用要求。只不过发现作者列表里边,单位竟然有Lightmatter和Nubis这两家光互连初创公司的当红炸子鸡,招募了imec在O波段GeSi EAM上经验丰富的两个博士。而另一家出名的光互连初创Celestial AI公司更是坚定的EAM支持者,imec也投资了,前段时间还有一个报道是Celestial AI购买了Rockley的一些专利,也包含了EAM相关的。Rockley针对O波段应用的EAM,有一个异质集成III-V EAM的方案,同步他们其实也有在跟南安普顿大学合作探索氮化硅集成的GeSi QCSE EAM。虽然这些可能都只是巧合😂,但这可能也是个潜在的方向吧,先做个记录。

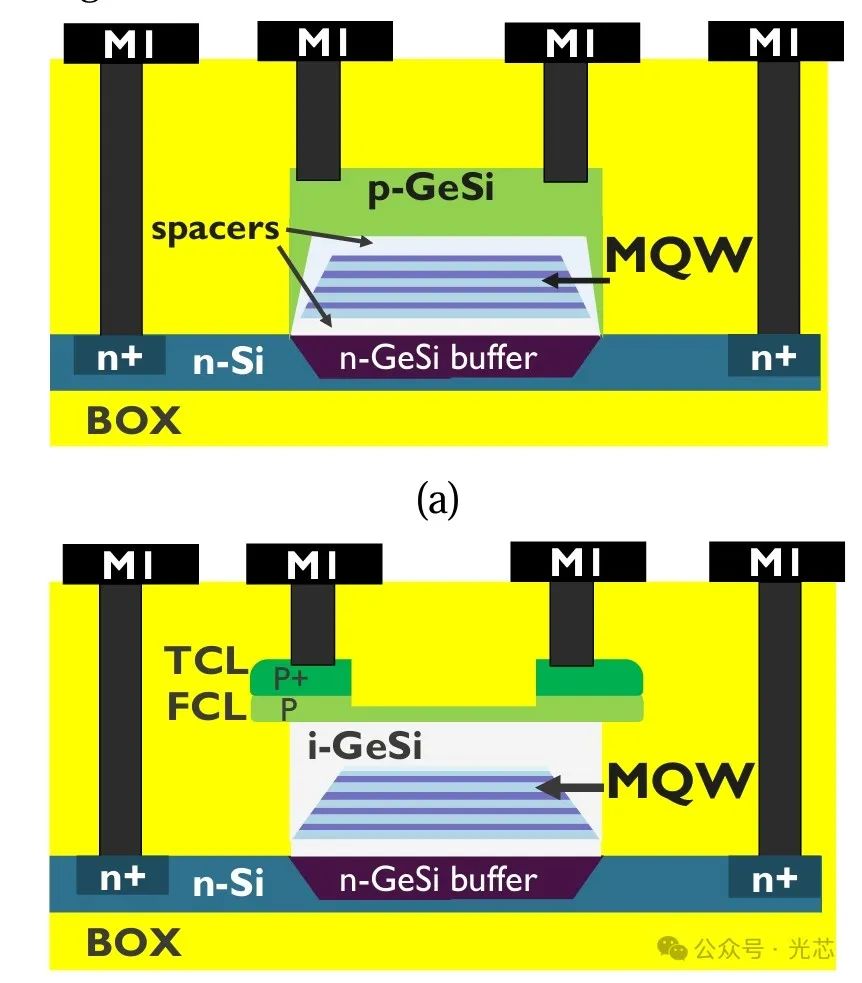

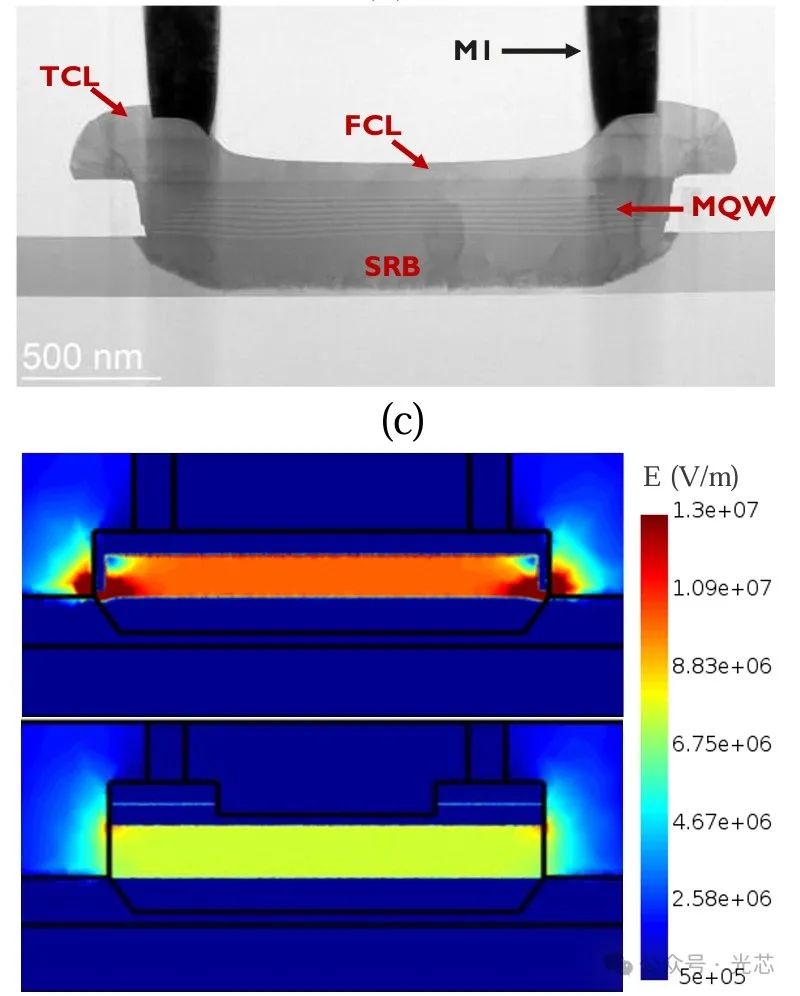

◆ 器件结构设计 这个文章采用的QCSE EAMs采用垂直p - i - n二极管结构,这种结构是为了有效地实现对光信号的调制。其中,器件的顶部和应变弛豫缓冲层分别作为二极管的p区和n区,它们的作用是形成一个电场,并且将这个电场限制在由MQW(多量子阱)构成的本征区内。薄间隔层则起到了将本征区与掺杂区隔离开的作用,这有助于控制载流子的运动和电场的分布,从而实现对光吸收的调制。相比他们之前的结构(图a),新的结构设计(图b)做了几点优化和改进:

1. 抑制p型掺杂:在紧邻MQW的区域抑制p型掺杂是一个重要的改进。这样做的目的是限制MQW两端区域的高电场,因为电场不均匀可能会导致可靠性问题,例如可能会引起材料的损坏或性能的下降。此外,减少该区域的p型掺杂还可以降低自由载流子吸收(FCA)带来的光损耗,提高调制器的效率。 2. p区结构调整:将二极管的p区移到器件顶部并分为两层,即场限制层(FCL)和顶部接触层(TCL)。TCL采用高掺杂,这有助于降低接触电阻,从而实现高速性能。因为在高速信号传输过程中,低接触电阻可以减少信号的损耗和延迟。FCL则采用适度掺杂,一方面可以减少FCA,另一方面可以使电场在MQW上分布更加均匀,进一步优化调制器的性能。 3. 减少金属的吸收损耗:通过部分蚀刻TCL,可以减少金属与光的相互作用,从而降低金属诱导的光损耗。这是因为金属在光传播过程中可能会吸收或散射光,导致光信号的损失,通过蚀刻TCL可以减少这种影响,提高光信号的传输效率。

通过对比新旧架构在-1V偏压下二极管本征区的电场分布,可以看出新架构的优势。新架构在整个MQW区域呈现出均匀的电场分布,这对于实现稳定和高效的光调制非常重要。而旧架构由于顶部区域的掺杂,在边缘处出现了电场尖峰,这种不均匀的电场分布可能会导致光吸收的不均匀,从而影响调制器的性能。需要注意的是,在相同的偏压下,新架构的场强小于旧架构,这是由于本征区厚度的差异导致的。本征区厚度的变化会影响电场的分布和强度,新架构通过调整本征区的结构和掺杂情况,实现了更均匀的电场分布和更优化的性能。

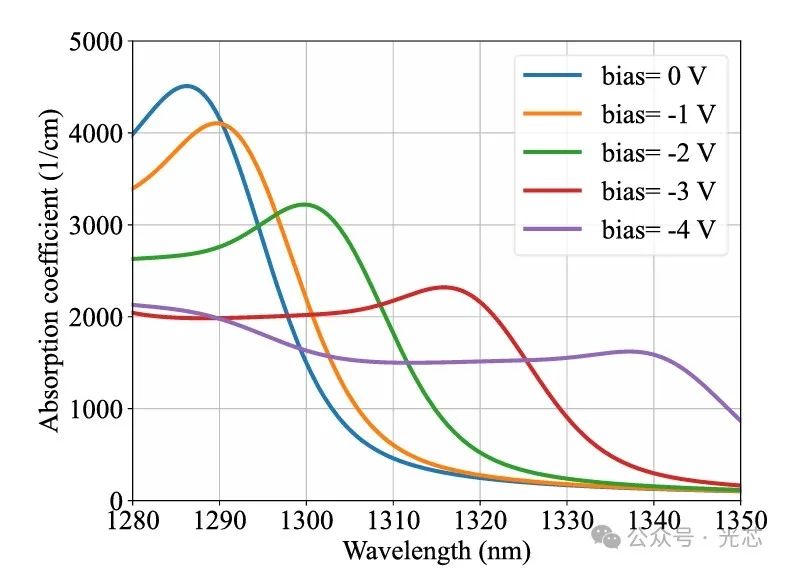

为了使QCSE MQW在O波段工作,需要对其吸收光谱进行设计。通过使用Ge0.98Si0.02量子阱(QWs)并优化其厚度,使得吸收光谱的吸收边在波长接近1.31μm处,符合O波段的工作要求。同时,选择合适的势垒厚度和Ge含量,以实现电子在导带和空穴在价带的有效限制,并在Gamma点实现Ⅰ型能带排列,这有助于提高光吸收效率。

此外,为了确保生长出的结构具有良好的稳定性,对MQW(QWs + barriers)进行了优化,使其成为应变平衡结构,即量子阱中的压应变由势垒中的张应变补偿,这样可以避免结构在生长过程中出现缺陷或变形。最后,使用nextnano软件和8带K.P方法对MQW QCSE堆叠的近边吸收进行了模拟,这有助于进一步了解和优化调制器的性能。

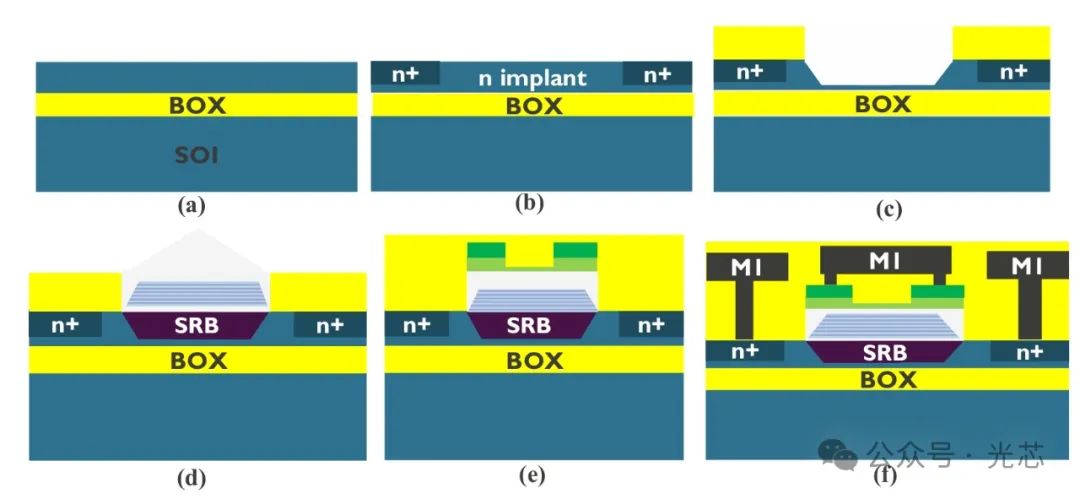

◆加工流程

1. 衬底掺杂和平坦化 - SOI晶圆进行磷离子(P)注入形成n型掺杂的底部接触层。 - 沉积二氧化硅(SiO₂)并进行平坦化处理,之后通过湿法蚀刻在硅波导中制造出腔体结构。该腔体作为后续外延生长各类功能层的“容器”,其精准成型对各功能层的生长质量、位置精度以及最终器件性能有决定性影响,比如合适的腔体尺寸能保障外延层厚度均匀、避免边缘效应等问题。 2. 外延生长与处理 - 晶圆经清洗后被置入ASM Intrepid™化学气相沉积(CVD)反应器中。先是在850°C进行短暂的外延生长前烘烤,优化晶圆表面状态,提升后续外延层生长质量,减少缺陷生成概率。 - 随后利用RPCVD技术与常规Ge和Si前驱体,选择性地在硅波导腔体内生长不同外延层。按顺序先是生长170nm厚、n型掺杂的Si₀.₁₅Ge₀.₈₅ SRB层(以PH₃作为掺杂源),生长后进行退火处理,降低线位错密度,减少晶格缺陷,提升晶体质量。 - 接着生长20nm厚的本征Si₀.₁₅Ge₀.₈₅底部间隔层,起到隔离缓冲作用,隔开SRB层与后续MQW结构,避免不同层间不良相互作用影响MQW性能;之后生长MQW结构,严格把控各量子阱与势垒的厚度、成分,保证整个外延结构应变协调稳定,防止因应变积累导致的材料开裂、性能劣化等问题。 - 再生长60nm厚本征Si₀.₁₅Ge₀.₈₅作为顶部间隔层,并且特意控制生长时间使其过量生长,确保能完全填充腔体,维持结构完整性与平整度,为后续工艺步骤提供良好基础。 3. 表面平整与p掺层生长: - 利用化学机械抛光(CMP)工艺将顶部表面处理至与周边氧化物平齐,保证表面平整度,利于后续光刻、沉积等工艺操作,减少因表面起伏导致的工艺误差与器件性能偏差。 - 450℃低温生长p型掺杂的Si₀.₅₀Ge₀.₅₀双层(FCL + TCL,场限制层 + 顶部接触层),且在工艺流后续阶段对TCL在腔体中心区域进行蚀刻处理,调整其结构与电学光学特性,减少光损耗等。 4. 电极加工

◆ 器件静态测试结果

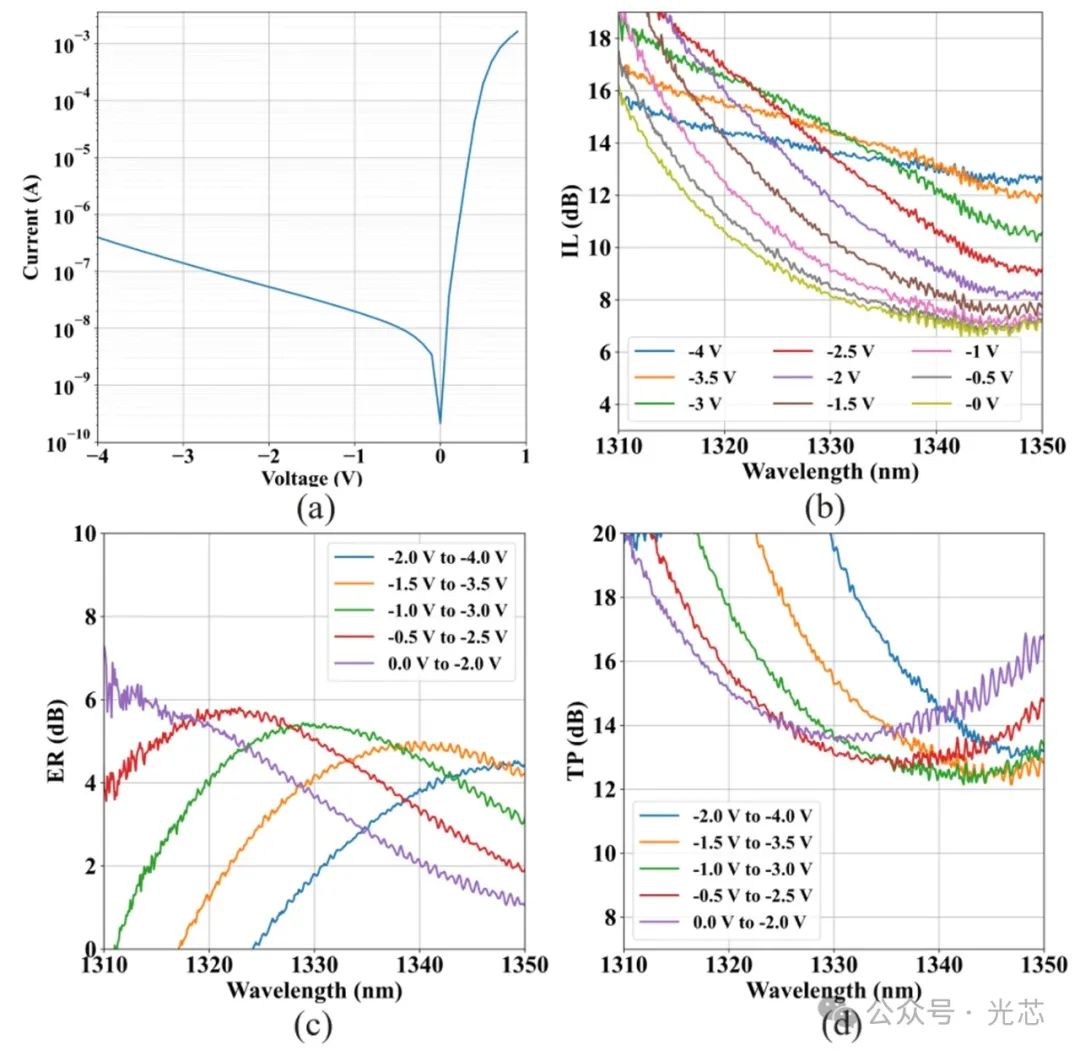

图4(a)展示了一个宽2μm、长36.8μm器件的测量IV特性曲线。在 -1V和 -4V偏压下,分别测量到20nA和0.4μA的暗电流。

图4(b)呈现了在25℃下,对于TE偏振光,输入光功率为 -1dBm,偏压从0V到 -4V以0.5V步长变化时,从1310nm到1350nm波长范围内测量到的插损IL。IL主要包含两部分贡献:一是硅波导与锗硅波导之间的耦合损耗CL,二是沿器件长度方向的传播损耗PL。

传输损耗涵盖了多种因素导致的损耗,包括来自顶部金属触点的金属诱导损耗、二极管掺杂区域中自由载流子吸收(FCA)引起的损耗、残余背景损耗(如锗硅中的间接带隙吸收、散射损耗、缺陷诱导损耗)以及量子阱的吸收损耗。

图4(c)展示了不同偏压摆幅下的消光比ER。在波长为1340nm,Vpp为2V(在 -1V和 -3V之间)时,ER约为5dB,相应的IL为7.5dB。加起来的发射机代价TP就有12.5dB了。

图4(d)展示了发射机的工作带宽范围。在1340nm附近, -1V偏压和2V摆幅时,获得了约12dB的最小TP,相应的1dB带宽约为20nm(1330nm - 1350nm)。与优化的C波段GeSi FK EAM相比,该TP值要差几dB(优化后的C波段器件在2Vpp时TP为8.5dB)。若要将中心波长向1310nm移动,需要调整MQW设计,比如将量子阱厚度减小到9nm或降低量子阱中的锗含量到97%,这两种方法都会因带隙减小导致激子吸收峰蓝移。

◆晶圆级静态测试分析

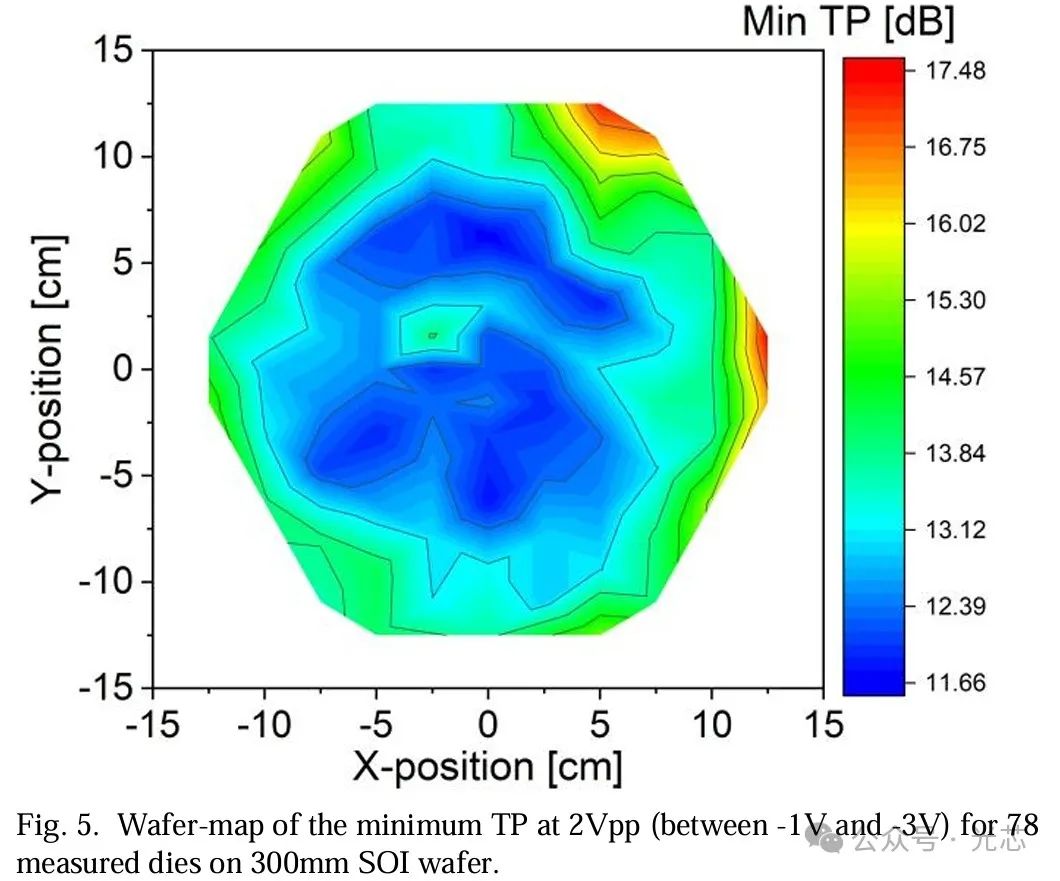

对300mm晶圆上的78个芯片进行了测量,图5展示了在2Vpp(在 -1V和 -3V之间)下提取的TPmin的晶圆图。TPmin的中位数为13.1dB,标准差为1.31dB。TPmin的最佳值大多位于晶圆中心,最差值位于晶圆边缘。

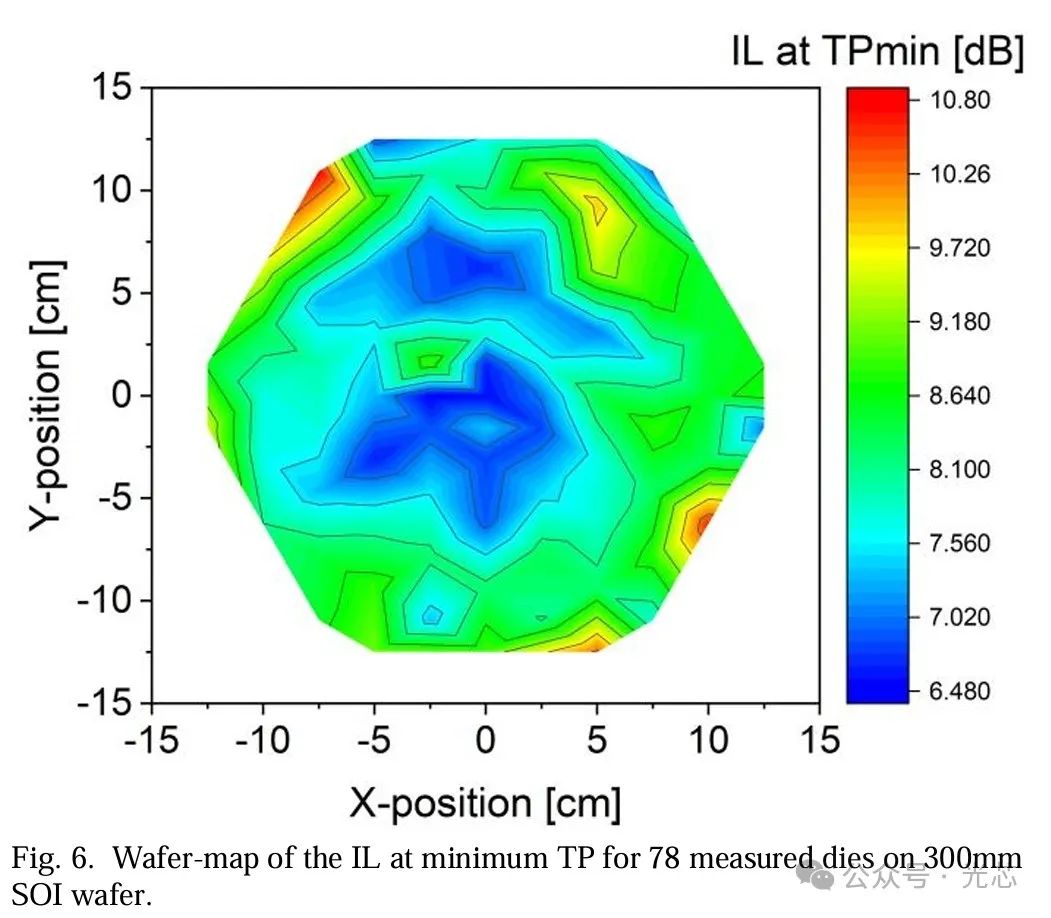

图6展示了测量的IL的晶圆图,中位数为7.9dB,标准差为0.98dB。最低IL值在晶圆中心测量到,与具有最低TPmin的芯片位置重合。

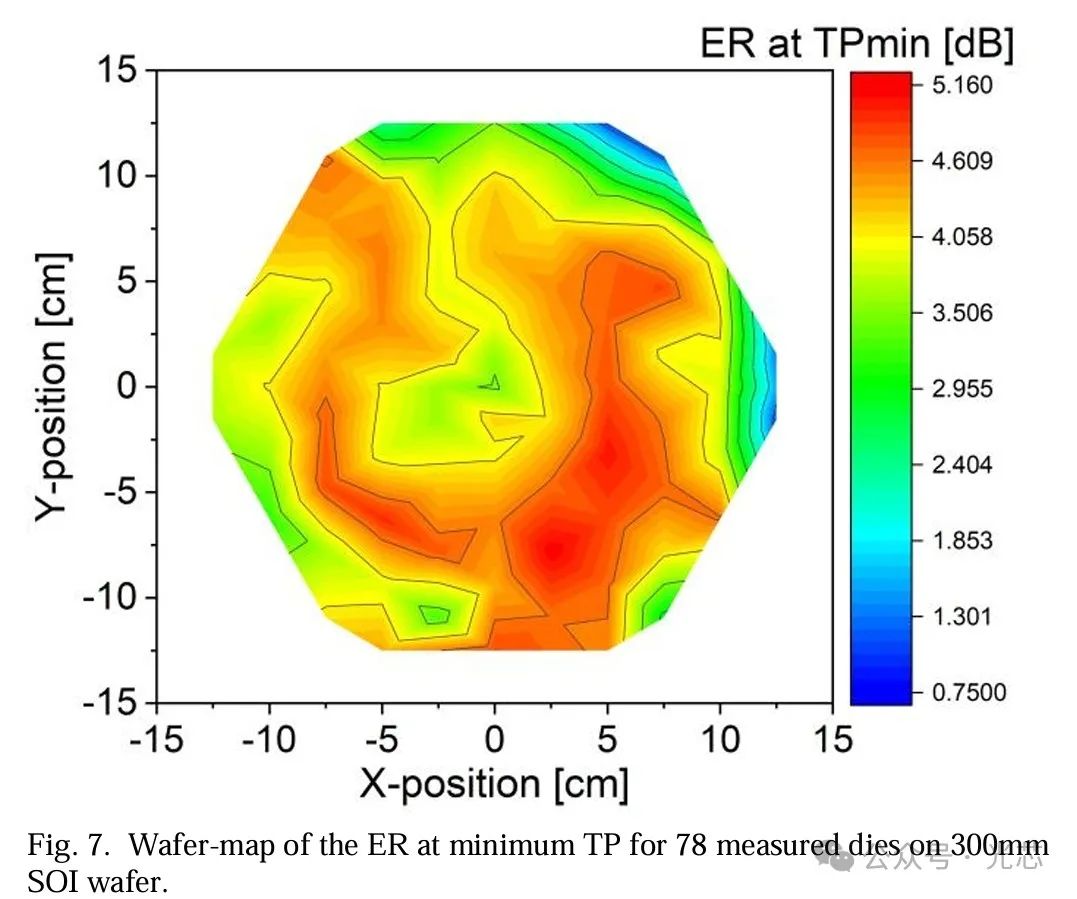

图7展示了在2Vpp(在 -1V和 -3V之间)下与TPmin相对应的ER的晶圆图。ER的中位数为4.13dB,标准差为0.89dB。低ER值位于晶圆边缘,与高TPmin的位置相同。因此,晶圆边缘芯片测量到的高TPmin值是由于这些器件的ER有限所致。

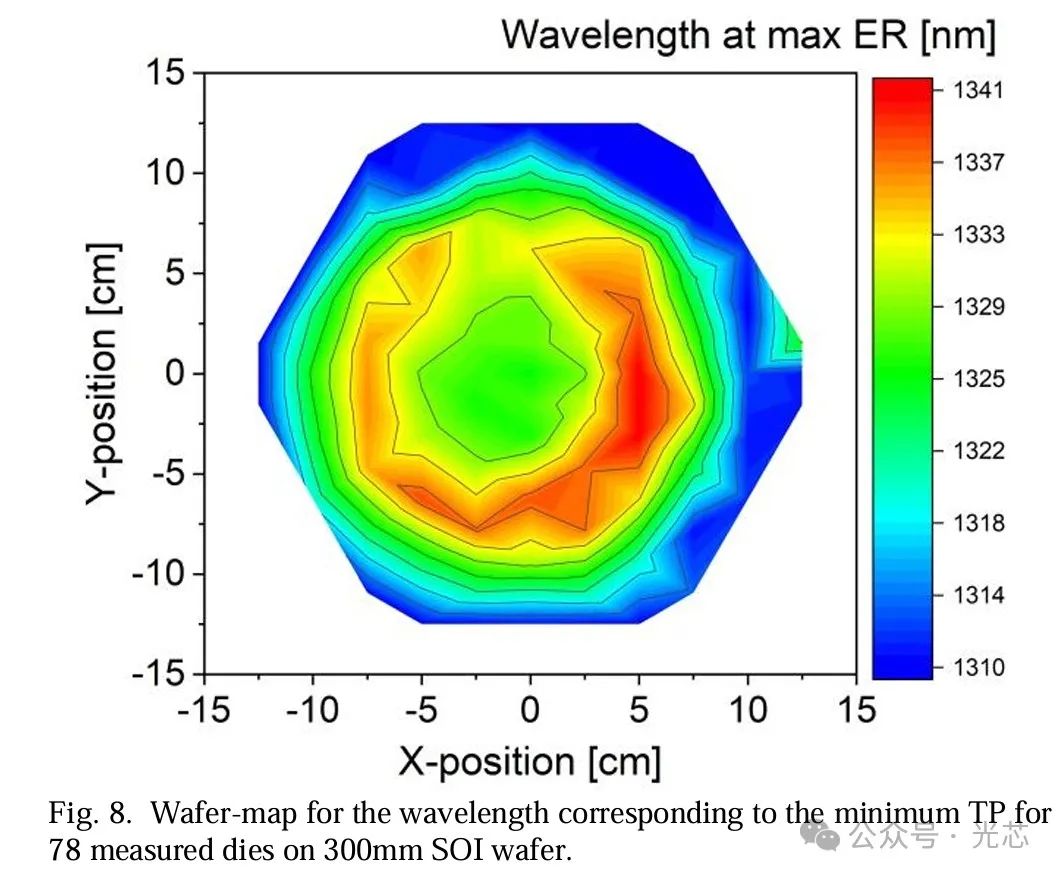

图8展示了在2Vpp(在 -1V和 -3V暗指在 -1V和 -3V之间)下最大ER波长的晶圆图,波长范围在1310nm至1341nm之间,标准差为10nm。观察到从晶圆中心到边缘的变化,这可能是由于晶圆上量子阱厚度和/或量子阱锗含量的变化引起的。通过改善QCSE堆栈在晶圆内的变化性,可能获得更窄的最佳工作波长范围。

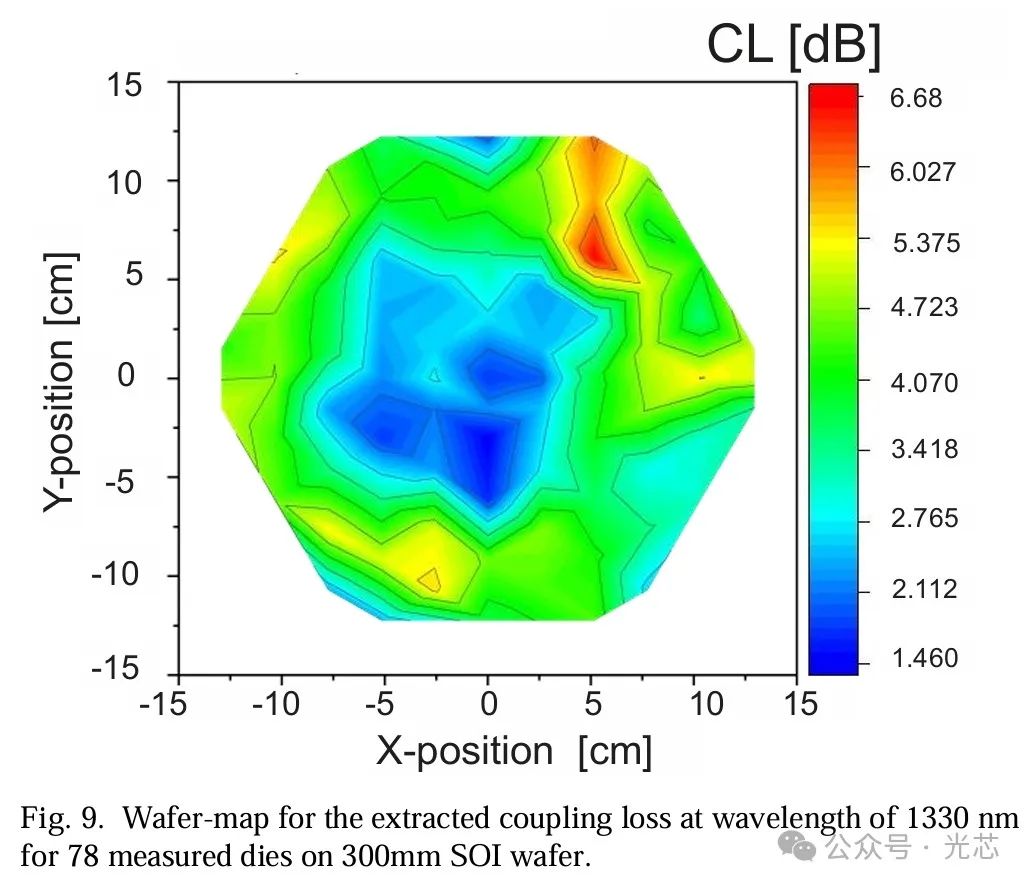

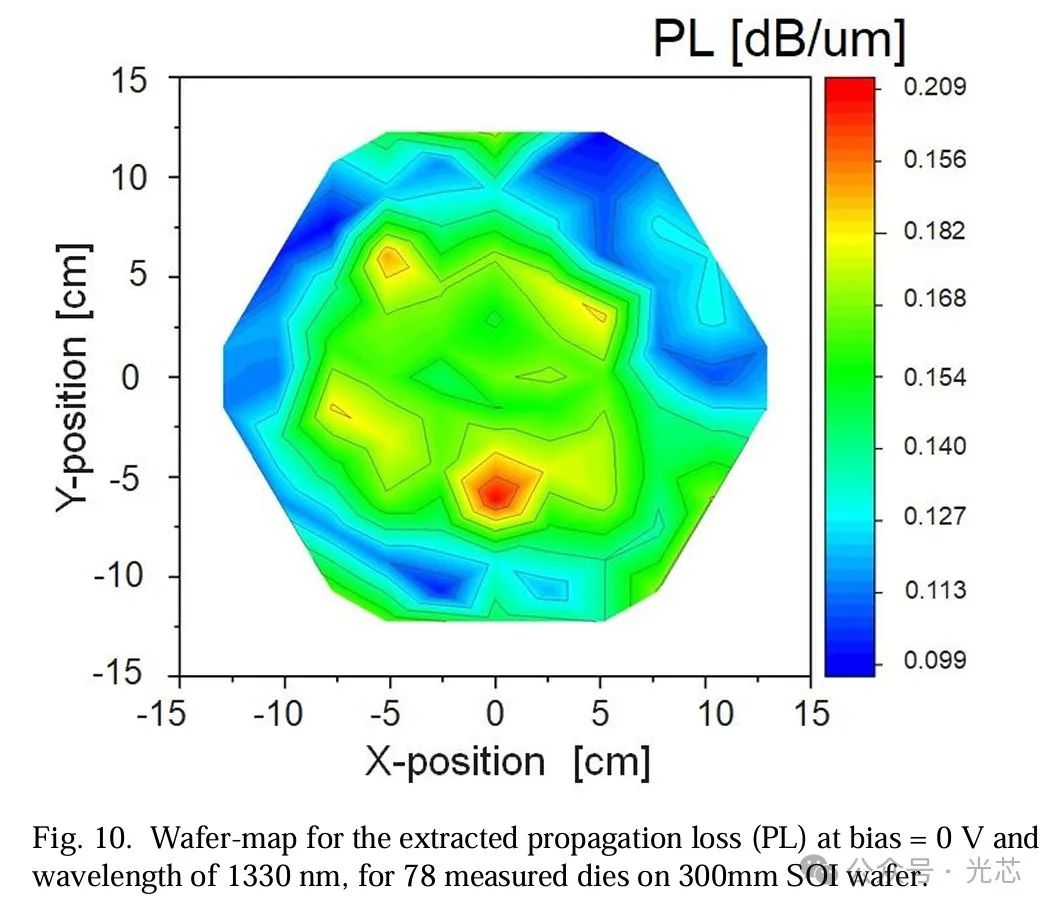

为了分析调制器的IL,将其分解为耦合损耗CL和传输损耗PL两部分。图9展示了在波长为1330nm时提取的耦合损耗的晶圆图,中位数约为4dB,标准差为1.19dB。低CL(<2dB)的芯片位于晶圆中心。图10展示了在1330nm时传输损耗的晶圆图,中位数为0.15dB/μm,标准差为0.02dB/μm。PL是如前文所述多种因素共同作用的结果。

晶圆级分析表明,具有最佳性能(最小TP、最小IL和最大ER)的器件位于晶圆中心。通过降低IL和提高ER可以提高器件的整体性能。要改善耦合,需要改进工艺流程以减轻在多晶硅/EAM界面发生的任何问题。在未来工作中,降低传输损耗的可能途径包括减少来自Si₀.₁₅Ge₀.₈₅层掺杂和间接带隙吸收,即考虑采用在SRB、势垒和间隔区域具有较低锗含量的QCSE量子阱。

◆ 高频性能测试

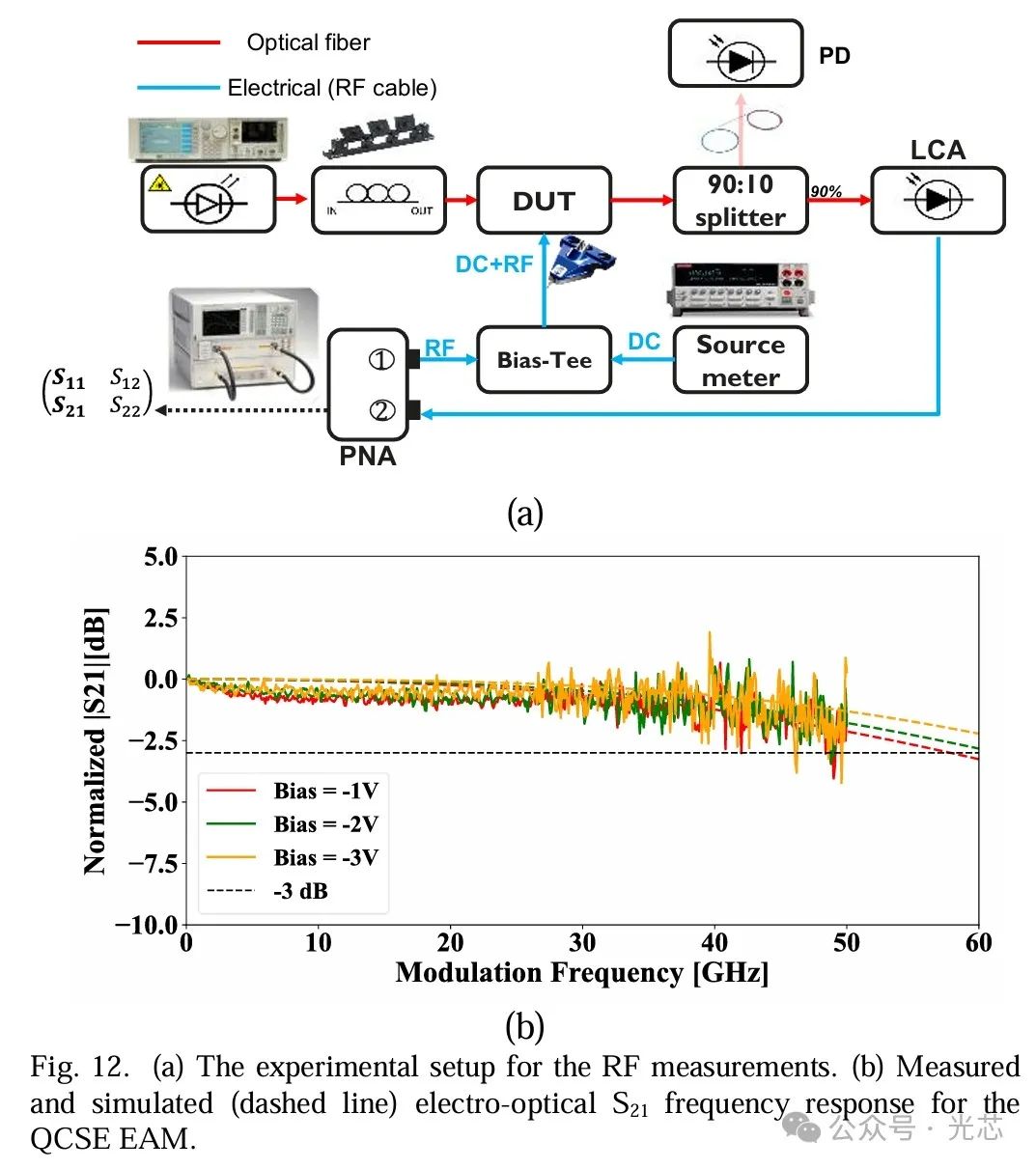

在工作波长为1320nm、输入光功率为1dBm时,不同反向偏压水平下的典型S21电光频率响应如下图,QCSE EAM的3dB带宽大于50GHz。在反向偏压下,PIN结的本征区厚度因耗尽而增加,较大的本征区会产生较小的结电容,因此随着偏压的升高,器件的速度会增加,这在图12(b)中可以明显看出。

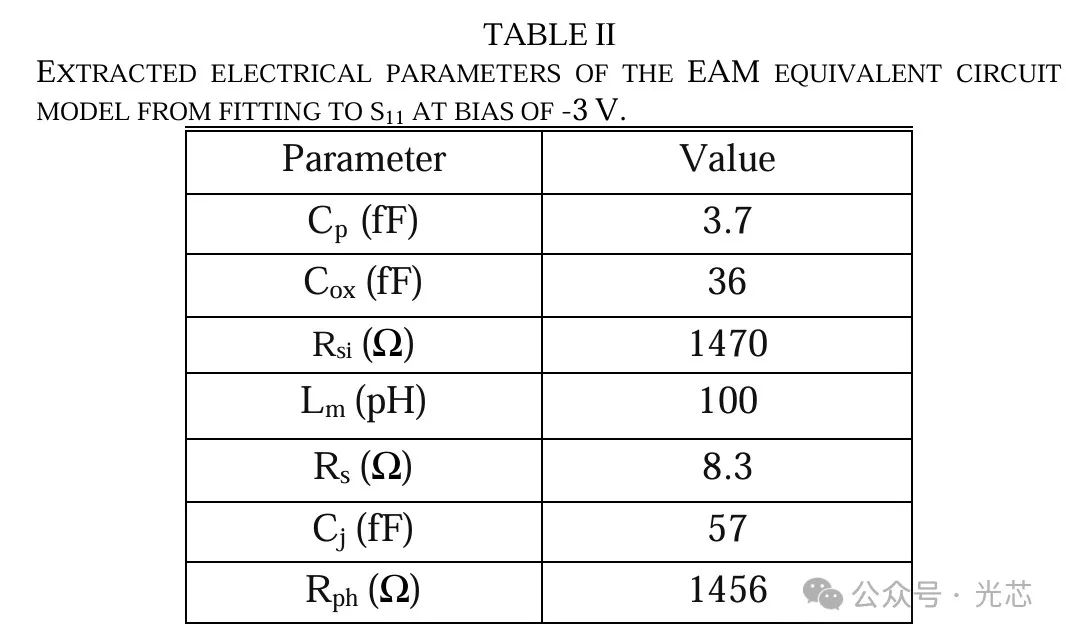

为了更深入地了解器件性能,考通过对器件进行单独的S11测量,提取出焊盘的参数,并在器件拟合过程中固定其值,从而从器件中去除焊盘的影响。核心器件的参数如下表,由四个部分组成:(1)金属线阻抗Lm;(2)器件的串联电阻Rs,它考虑了不同器件层的电阻以及电极处的欧姆接触电阻;(3)器件的结电容Cj;(4)由于本征区内的光吸收而在器件中产生的光电流。光电流表示为一个电流路径,其阻抗可以用与结电容并联的电阻(Rph)来表示。

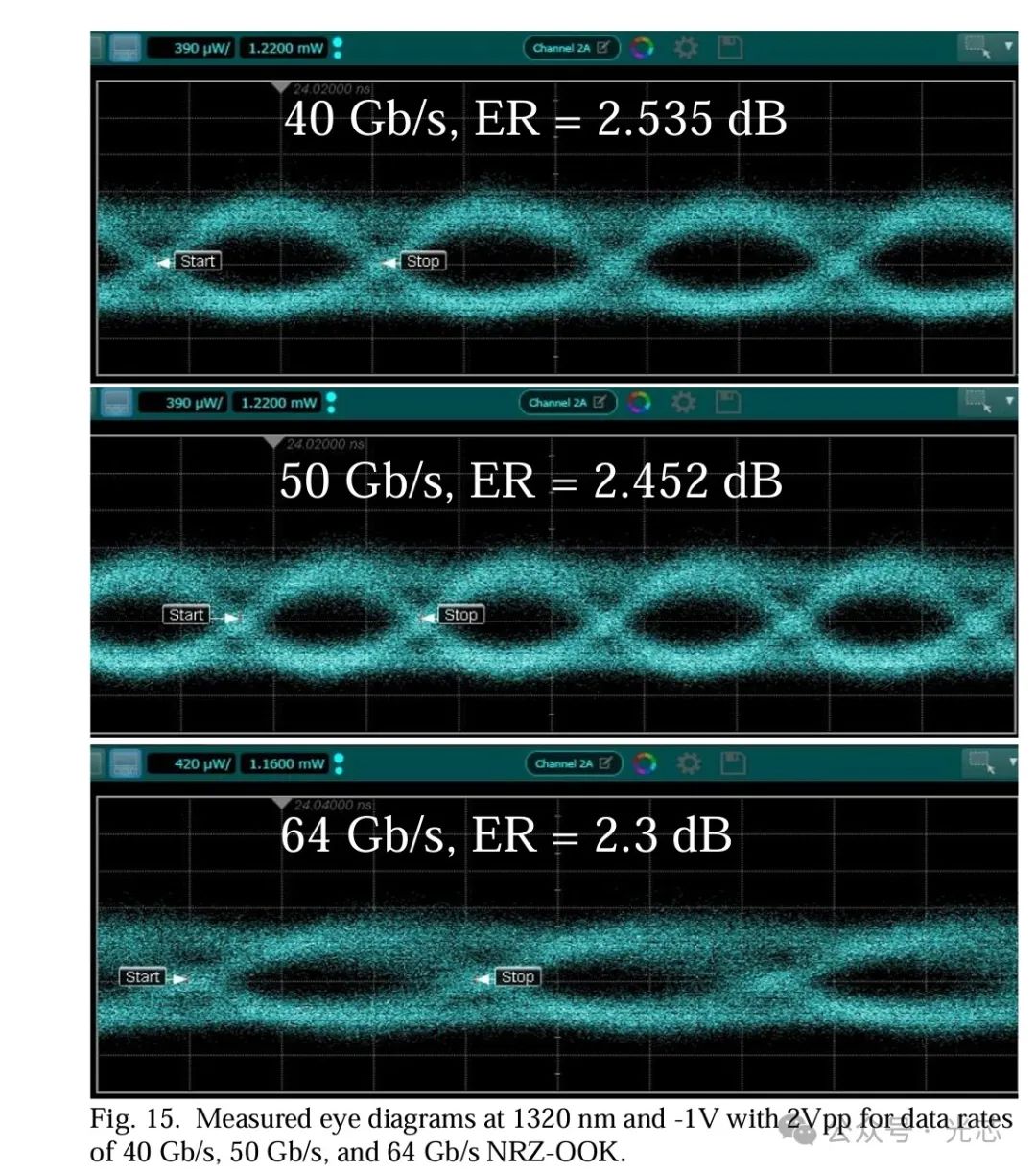

图15展示了器件的大信号调制性能。在1320nm波长、输入光功率为0dBm和偏压为 -1V的条件下,测量得到了在40Gb/s、50Gb/s和64Gb/s时的眼图,动态消光比分别为2.535dB、2.452dB和2.3dB(2Vpp)。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-11-27,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读