Alphawave Semi的CPO报告(三):CPO的机遇与挑战

搬运一个Alphawave Semi公司首席技术官Tony Chan Carusone在2023年的关于CPO的报告,这家公司本身是做高速Serdes和Chiplet的,这个报告也类似于Tutorial的性质,不过介绍得蛮清楚的,把CPO的发展和演进及未来挑战都做了客观的呈现。以下是直接将演讲者的发言原文直接翻译,分成四个部分,分别介绍背景,CPO的应用场景、机遇与挑战以及光/电/封装的协同优化。以下为第三部分的翻译。

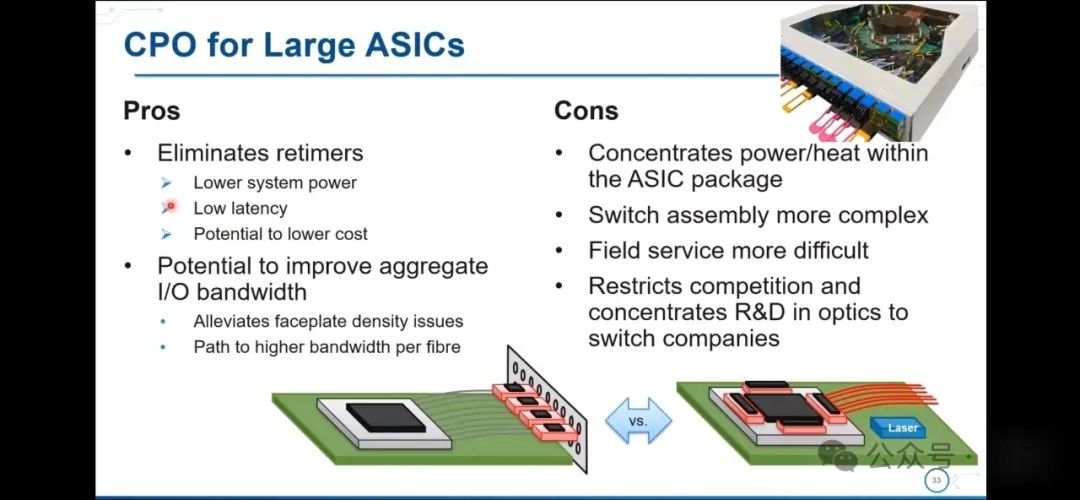

我们先讲讲针对这些大型专用集成电路的共封装光学器件的情况。我们已经讲过它带来的一些好处,从高层次、很明显的角度来看,它有望消除我之前提到的数据漫长传输过程中那些中继器、额外的电链路环节,这有望降低整个系统的功耗,能减少延迟,因为每次接收和重新传输都会引入一点延迟,而且还有可能降低成本,毕竟如果少了一个芯片,少了一个重新发射器,那就意味着少买一个部件,成本应该会降低,它还有可能提高输入输出总带宽,要知道光学器件本身在输入输出带宽方面有巨大的潜力,它们就像是能承载大量数据的神奇波导,问题只是如何利用好它们,不过这也面临很多挑战。

首先,把这些功能都整合到同一个封装里,会使功耗更加集中,从而在小体积内产生大量热量,而且顺便说一下,这会把系统中最大的单一热源,也就是主处理引擎 ASIC,放到了那些可能对温度最敏感的部件,也就是光学器件旁边,所以这可能会带来一些必须要解决的热管理方面的挑战。另外,系统的组装也是个问题,这是我从思科 “SiliconOne” 的发布中截取的一张图,大家可以想象一下,如果有一个带有数百根光纤尾纤的交换机,那就得有人进去把每一根都连接好,而且要确保这些链路都能正常工作,不能有灰尘等等,再对比一下可插拔的环境,基本上就是有人用手插拔一下就行了,如果有一根坏了,派人过去换一下就行,这差别可太大了,想象一下有一根链路出故障了,诊断报告发送给数据中心的运维人员,那得有人去把这个交换机拔出来,而且这么做的话,与之相连的大量计算资源都会受到影响,还得打开交换机,进去排查故障原因,我的意思是,和可插拔环境相比,这差别可太大了,可插拔环境里知道是哪根链路出问题了,换个插头就行,一切就恢复正常了,对于这些运维人员来说,这可是个大麻烦。

另一个重要问题是,它实际上限制了竞争,使得光学链路的研发集中到了那些制造交换机的公司手里,因为现在整个产品基本上就是一个芯片,虽然是由多个小芯片组成的,但整个系统都集成在那里了,而在目前大多数网络交换机依靠可插拔光器件的模式下,有很多不同的公司在针对不同的可插拔模块、不同的技术进行创新,把硅光子学技术融入进去,采用不同的激光技术来降低功耗并相互竞争,能制造出 50 Tbps、100Tbps交换机的公司非常少,屈指可数,而在这种新模式下,还是这几家公司,它们也将负责所有的光学研发工作,所以这就增加了创新的门槛,可能会在某些方面拖慢进展,大家可以看到市场动态在这里是如何发挥作用的,对不同的公司来说,这既是挑战也是机遇。

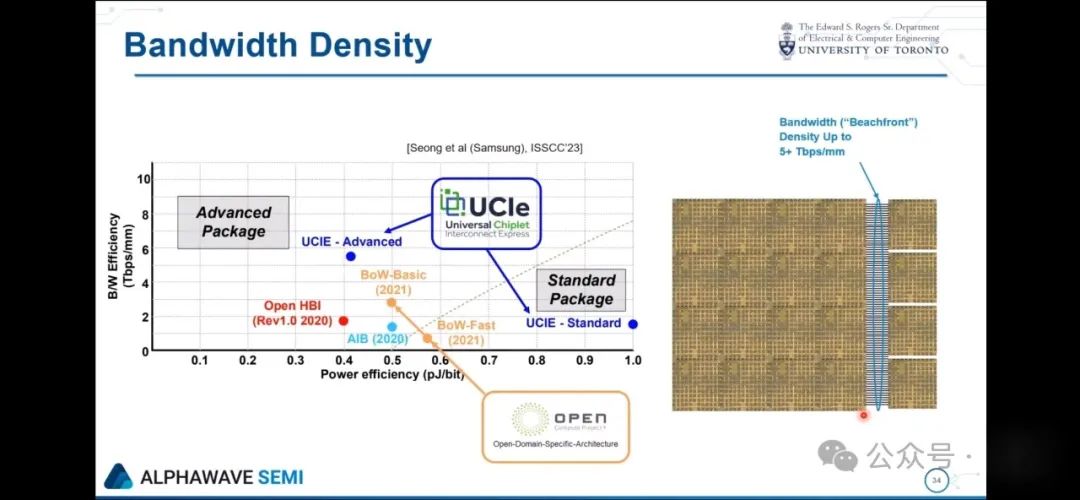

我还想谈谈带宽密度这个作为共封装光学器件面临的挑战和机遇的方面。从根本上来说,由于数据的端点总是硅芯片,就存在这样一个问题,就是如何让数据进出芯片边缘,芯片尺寸受到制造设备以及可实现的良率限制,因为硅片上会有缺陷,芯片尺寸就是那么大,哪怕是最大的芯片也是如此。所以我们现在经常用带宽密度或者叫边缘密度(有时候也叫海岸线密度)来衡量芯片连接性能,也就是每毫米芯片边缘能传输多少吉比特或太比特每秒的数据。如果在这里利用小芯片范式,有两个小芯片被封装在一起,间隔1mm甚至更小,通过先进的封装技术实现非常密集的布线,就能实现5 Tbps/mm甚至更高的数据传输速率。这里有一篇23年 2 月,来自三星一位作者发表的论文,突出展示了能达到的一些数据,同样也是利用了 UCie 标准的数据点(这里用蓝色突出显示了),能实现Tbps/mm的带宽密度,这足以满足计算和处理需求,而且在一段时间内都够用。当然,封装技术需要不断发展来跟上这个需求,这是好事,意味着这个芯片间链路缓解了瓶颈问题,其他瓶颈问题才会成为限制因素,这是好的方面。

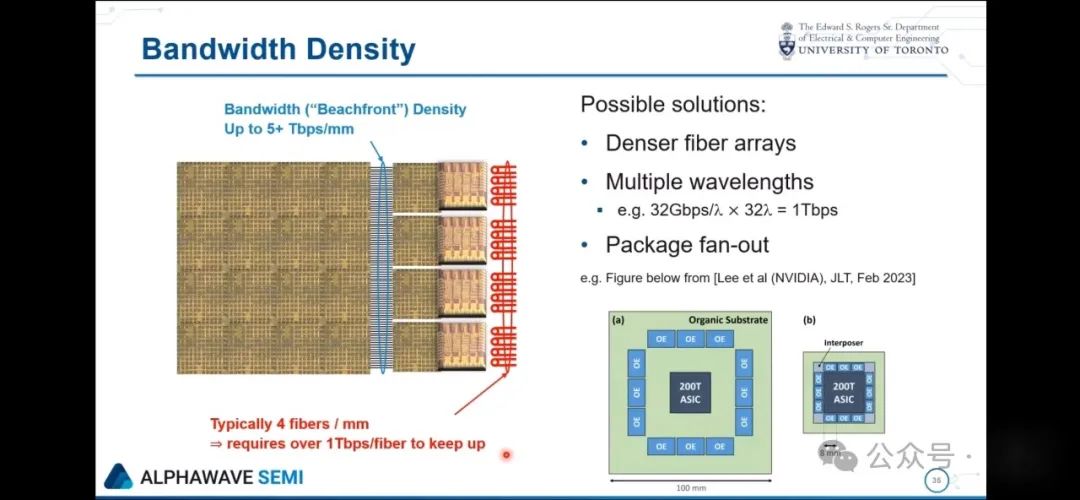

但共封装光学器件存在的问题是,通常光纤是每毫米布置 4 根左右,如果要跟上这种进出专用集成电路能达到的5Tbps/mm的带宽密度,那每根光纤就得每秒传输 1 Tbps的数据才能跟得上。虽然这不是说就一定会造成瓶颈,不过有点讽刺的是,共封装光学器件原本是为了解决进出芯片的总带宽挑战的,却在这种模式下可能变成了限制因素,这并不是说没有正在大力研究的解决方案,有些方案是显而易见的,比如也许可以想办法让光纤排列更密集,或者可以利用每根光纤的多个波长,又或者可以采用像英伟达一位作者刚发表的一篇论文里展示的方法,也就是做一些扇出,使用更大的封装,开始把链路布线延伸得更远一点,这样芯片间链路就得变长,在这方面还需要一些研发工作,但这并不是说这个问题无法解决,只是说这仍然是一个有待攻克的挑战,还在摸索合适的解决办法。

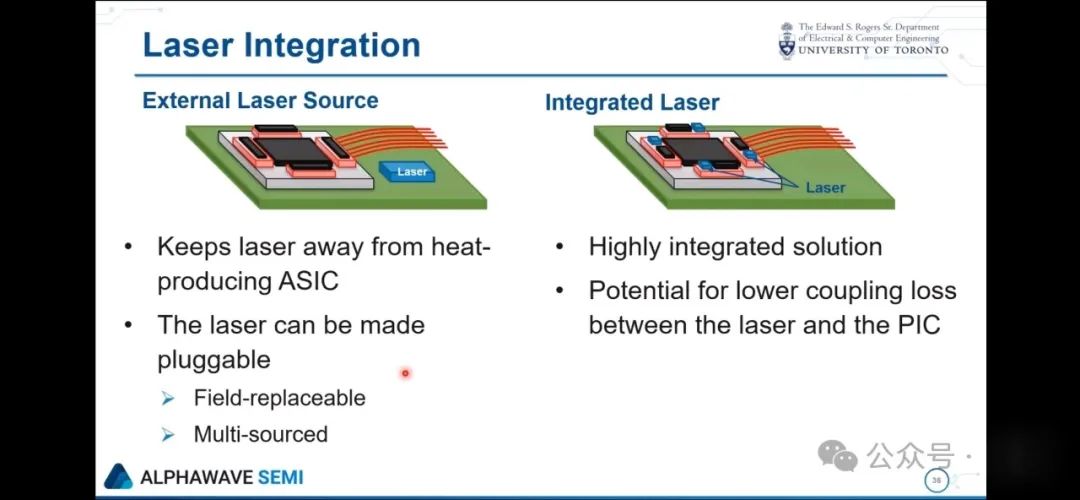

还有一个有意思的领域,会有更多的研发投入和创新继续产生效益,那就是激光集成的问题,也就是激光应该放在哪里。目前更主流的思路是采用外部激光源,也就是激光不在封装内部,有时候简称 ELS,这样做的好处是能让激光远离产生热量的专用集成电路,激光器是那种寿命会受到高温高热影响的部件,而且现在甚至已经有了针对外部激光源的标准或者至少是多源协议,使得它们可以做成可插拔的形式,基本就是把它们做成和可插拔模块一样的外形尺寸,只是里面放的是激光,这样如果激光出故障了,又可以有人去插拔一下,把激光换掉,所以这使得激光可以现场更换,而且可以从不同供应商那里获取,有助于降低成本。

但另一方面,也有一些已经得到验证并且日益成熟的技术,可以把激光集成到封装内部,甚至直接集成到硅光子学芯片上,这显然是一种非常简洁、高度集成的解决方案,它还有可能降低激光与硅光子学芯片之间的耦合损耗,而且实际上,如果激光连接做得很稳固,有人认为尽管存在额外的热量问题,但它其实更稳定,长期可靠性更好,所以看看这方面后续如何发展会很有意思,但这就是一些权衡取舍的情况,我觉得在集成激光技术证明其成熟性之前,我们最初会看到更多侧重于外部激光源的解决方案。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-12-23,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读