从0和1到复杂计算:计算机是如何「思考」和处理信息的?

从0和1到复杂计算:计算机是如何「思考」和处理信息的?

用户1493530

发布于 2026-05-06 21:37:08

发布于 2026-05-06 21:37:08

作为一个写了快十年代码的人,我一直觉得这个问题特别有意思。因为大多数程序员(包括曾经的我)日常工作都停留在高级语言这一层,写 Swift、写 Python、调 API,对底层发生了什么其实是模糊的。真正让我把这条链路想通的契机,是读研期间啃《计算机组成与设计》(Patterson & Hennessy)和 Charles Petzold 的《编码》。读完之后有一种「原来如此」的通透感,从那以后看代码的视角完全变了。

今天就把这条从沙子到智能的完整路径捋一遍。放心,不会变成教科书复读机,我尽量用人话讲清楚每一层到底在干什么,以及它们之间是怎么咬合在一起的。

为什么是二进制?这是物理决定的

很多科普文章一上来就说「计算机用二进制」,但很少解释为什么。说白了,这不是数学家的偏好,是电子工程的物理必然。

晶体管(现代芯片用的是 MOSFET)本质上就是一个电压控制的开关。给栅极施加电压,导通,代表 1;移除电压,截止,代表 0。两种状态,清清楚楚。如果你非要搞三进制、十进制,就意味着电路需要精确区分三个甚至十个电压等级,对噪声的容忍度会急剧下降。5V CMOS 标准下二进制的噪声容限高达 1.45V,也就是说信号被近 1.5 伏的干扰污染了,电路照样能正确判断是 0 还是 1。换成三进制,这个容限直接砍半。在芯片内部数十亿个晶体管高速翻转、电磁干扰无处不在的环境下,这点容错空间就是生命线。

另一个关键原因是布尔代数的存在。George Boole 在 1854 年搞出了一套只用 TRUE/FALSE 做运算的代数体系,跟二进制天然一一对应。1937 年,21 岁的 Claude Shannon 在 MIT 硕士论文里证明了布尔代数可以直接映射到电路设计上,串联开关就是 AND,并联开关就是 OR。这篇论文后来被评价为「本世纪最重要的硕士论文」。从那一刻起,数学和电路之间的桥就搭好了。

Petzold 在《编码》里有一句特别精辟的话,大意是:二进制是最简单的可用数制,再简单就只剩 0 了,而一个 0 什么也干不了。

万物皆可编码:数字世界的「通用货币」

有了 0 和 1,下一步就是用它们表示世间万物。

整数用补码(Two's Complement)编码,这是冯·诺依曼 1945 年首次建议、IBM System/360 在 1964 年确立的工业标准。补码最妙的地方在于加减法统一:A−B 直接变成 A + (B 的补码),硬件上只需要一个加法器就搞定,不用再单独做减法电路。8 位补码能表示 −128 到 +127,而且零只有唯一表示 00000000,没有原码那种「+0 和 −0 并存」的尴尬。

浮点数遵循 IEEE 754 标准。单精度 32 位由 1 位符号 + 8 位指数 + 23 位尾数组成,利用「隐含前导 1」的技巧获得等效 24 位精度。顺便提一下很多新手踩过的坑:0.1 + 0.2 ≠ 0.3,几乎所有编程语言都是这样。原因就是 0.1 在二进制里是无限循环小数,无法精确表示。

图像中每个像素由 RGB 三通道各 8 位组成,共 24 位约 1678 万色。音频(CD 品质)采用 44.1kHz 采样率、16 位量化。视频就是图像帧按 24/30/60fps 高速播放,未压缩数据量极大,所以 H.264/H.265 压缩编码必不可少。说白了,无论文字、图片、声音还是视频,进入计算机的那一刻全都变成了 0 和 1 的序列,区别只在编码规则。

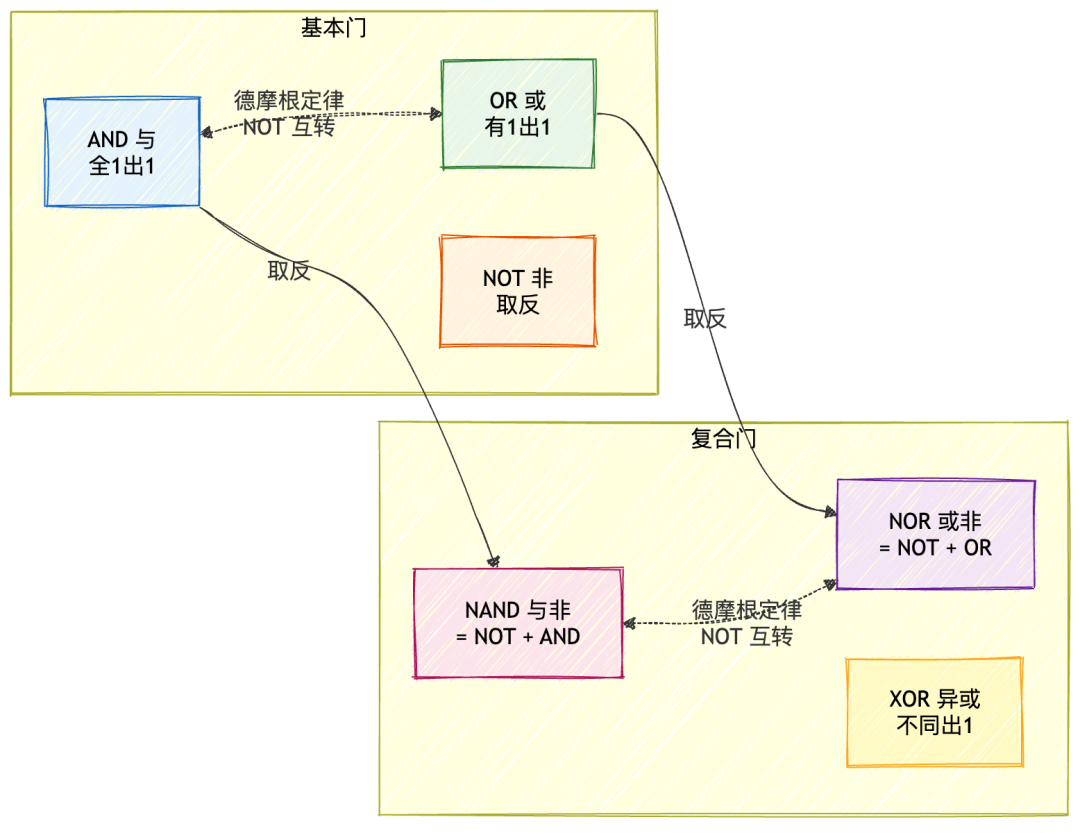

逻辑门:数学变成电路的关键一跳

布尔代数提供了六种基本运算,每一种都对应一种「判断逻辑」,理解它们最好的方式是把 1 想成「真/通电」,0 想成「假/断电」。

AND(与):两个输入都为 1,输出才为 1。生活中的类比就是串联电路,两个开关都按下灯才亮。写代码的人天天用,if (age > 18 && hasID) 里的 && 就是 AND。

OR(或):只要有一个输入为 1,输出就为 1。对应并联电路,按下任意一个开关灯就亮。代码里的 || 就是 OR。

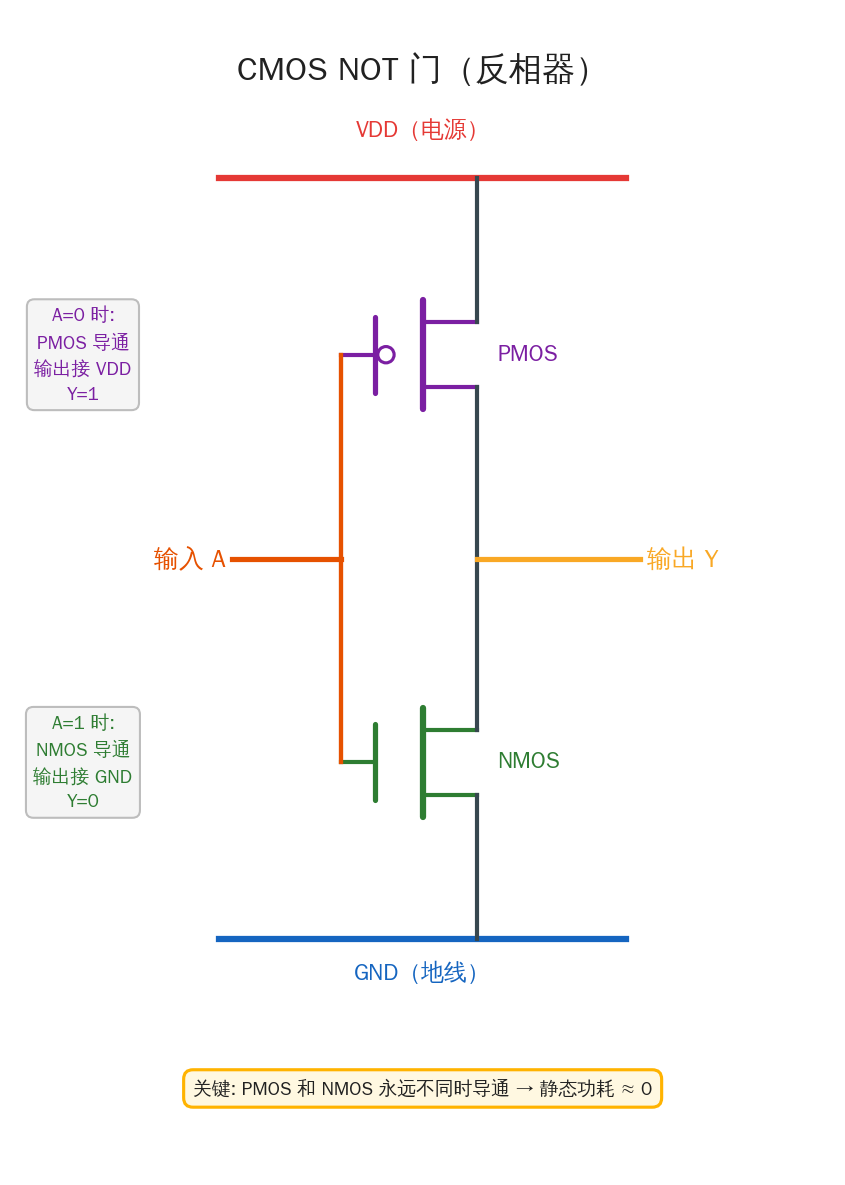

NOT(非):唯一的单输入运算,把 0 变 1、把 1 变 0,纯粹的取反。代码里的 ! 就是 NOT。在硬件层面 NOT 是最简单的门电路,只需要两个晶体管,具体怎么实现后面讲 CMOS 的时候会拆解。

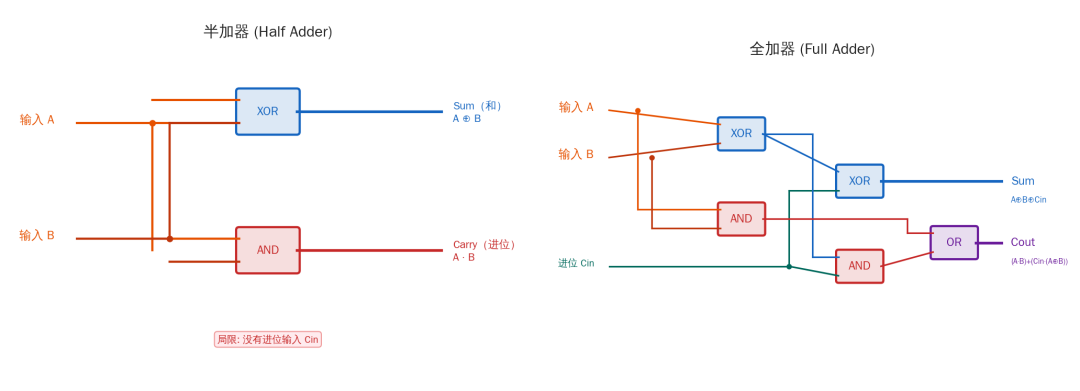

XOR(异或):两个输入不同时输出 1,相同时输出 0。名字里的「异」就是「不一样」的意思。XOR 在计算中的地位极其特殊:它天然就是不带进位的 1 位加法(0+0=0, 0+1=1, 1+0=1, 1+1=0,进位丢掉),所以半加器的 Sum 输出就是一个 XOR 门。此外 XOR 还有一个妙用,对同一个值异或两次等于没操作(A⊕B⊕B = A),这是很多加密算法和数据校验的基础。

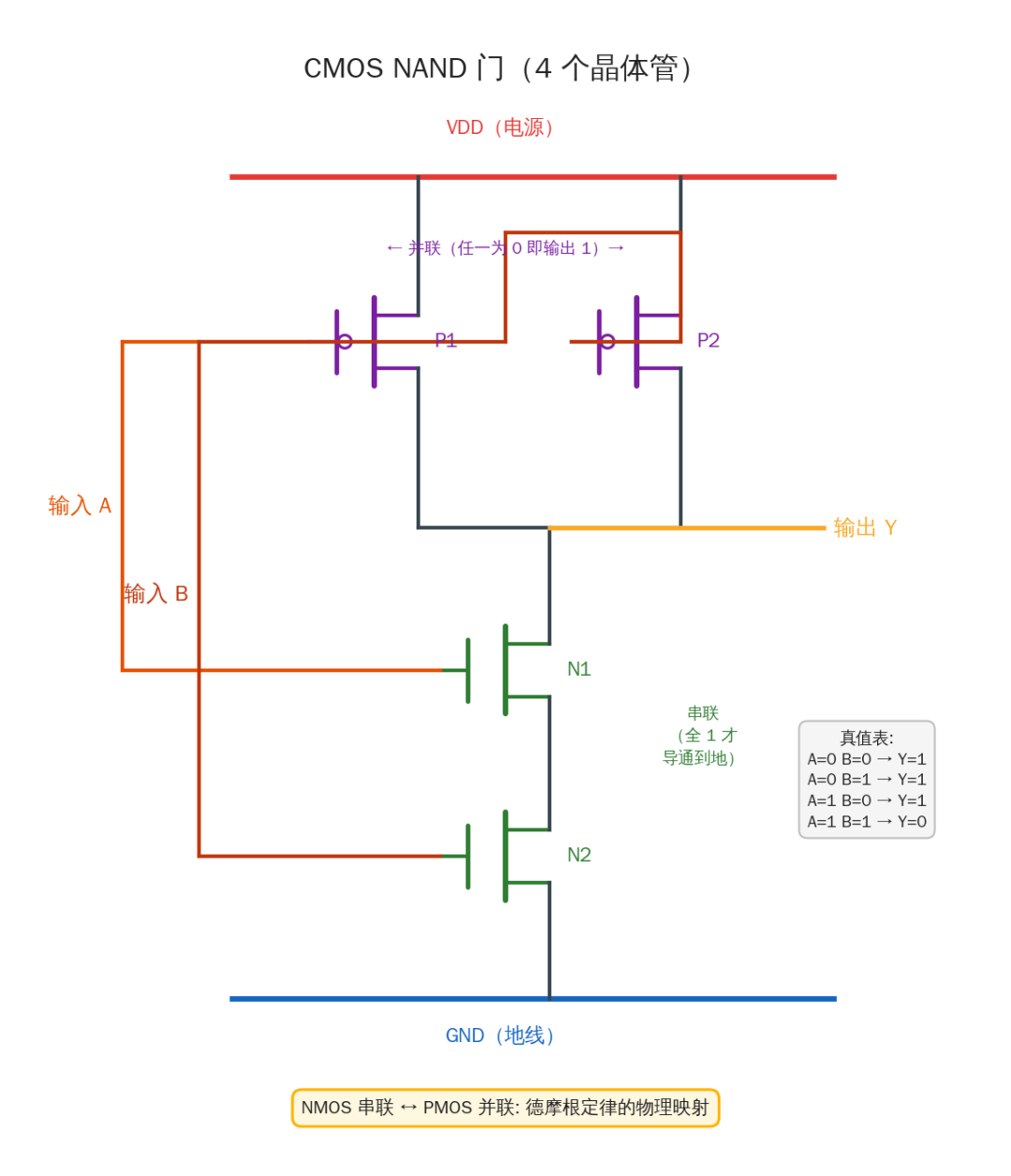

NAND(与非):AND 的结果取反。说白了就是「不全为 1 则输出 1」。看起来只是 AND 加个 NOT,但它在整个数字电路体系中的地位极其特殊,后面单独说。

NOR(或非):OR 的结果取反,「全为 0 才输出 1」。和 NAND 一样,NOR 单独也是功能完备的,但由于 CMOS 工艺中 NMOS 速度快于 PMOS,NAND 门的性能优于 NOR 门,所以工业界普遍选择 NAND 作为基础构建块。

这六种运算之间有一套优雅的数学关系,其中最关键的是**德摩根定律**:NOT(A AND B) = (NOT A) OR (NOT B),反过来 NOT(A OR B) = (NOT A) AND (NOT B)。说白了,AND 和 OR 可以通过 NOT 相互转化。这条定律在电路优化中用得极其频繁,工程师可以只用一种门类型(比如 NAND)加上适当的取反组合,来替代所有其他逻辑门。

这里面有一个深刻的数学事实叫功能完备性:如果一组逻辑运算能表达所有可能的布尔函数,就称其功能完备。{AND, OR, NOT} 是功能完备集,但更厉害的是,{NAND} 单独就是功能完备的。Henry M. Sheffer 在 1913 年证明了这一点。只用 NAND 门就能造出 NOT(两个输入短接)、AND(NAND 后再 NAND)、OR(先各自取反再 NAND),进而搭出任何数字电路。

这也是希伯来大学「Nand to Tetris」课程的灵感来源,从一个 NAND 门出发,一路造到能跑俄罗斯方块的完整计算机。

▶晶体管如何实现逻辑门:CMOS 技术

那晶体管怎么实现逻辑门?这就要从 MOSFET(金属氧化物半导体场效应晶体管)说起。

MOSFET 有三个引脚:源极(Source)、漏极(Drain)、栅极(Gate)。栅极是控制端,给它施加电压,源极和漏极之间的沟道就导通,电流得以通过;撤掉电压,沟道关闭,电流截断。说白了就是一个用电压控制的微型开关,没有任何机械部件,切换速度可以到纳秒甚至皮秒级别。

MOSFET 分两种类型,特性恰好互补:

NMOS(N 型):栅极施加高电压时导通,低电压时截止。NMOS 擅长把输出「拉向地线(0V)」,也就是输出逻辑 0。可以理解为「给信号就通,输出 0」。

PMOS(P 型):跟 NMOS 完全相反,栅极施加低电压时导通,高电压时截止。PMOS 擅长把输出「拉向电源(VDD)」,也就是输出逻辑 1。可以理解为「不给信号才通,输出 1」。

现代芯片几乎 100% 采用 CMOS(互补 MOS)技术,核心思想就是让这两种晶体管搭配干活:PMOS 组成上拉网络(连接电源 VDD,负责输出 1),NMOS 组成下拉网络(连接地线 GND,负责输出 0),二者互补工作,在任何稳定状态下有且只有一个网络导通。

理解了这个原则,NOT 门(反相器)的实现就水到渠成了:

当输入 A = 1(高电压)时,NMOS 导通把输出拉到 GND,PMOS 截止;输出 Y = 0。当输入 A = 0(低电压)时,PMOS 导通把输出拉到 VDD,NMOS 截止;输出 Y = 1。输入 0 输出 1,输入 1 输出 0,完美的取反。而且因为 PMOS 和 NMOS 永远不会同时导通,VDD 到 GND 之间没有直通路径,静态功耗几乎为零。这就是为什么 CMOS 技术能把数十亿个晶体管塞进一块指甲大小的芯片而不烧掉。

NAND 门则是在 NOT 门基础上扩展。NAND 门只需 4 个晶体管:下拉网络用 2 个 NMOS 串联(两个输入都为 1 才能导通到地,输出 0),上拉网络用 2 个 PMOS 并联(任一输入为 0 就导通到电源,输出 1)。串联和并联的对偶关系正好对应德摩根定律,这不是巧合,而是数学结构在物理电路中的直接映射。相比之下,AND 门需要先 NAND 再加一个 NOT(反相器),总共 6 个晶体管,效率反而更低。NAND 是 CMOS 工艺的「原生产物」,AND 反倒是派生出来的。 这就是 NAND 门在制造层面称霸的物理原因,也解释了为什么它能成为功能完备的万能积木。

▶晶体管的指数级增长

从 1971 年 Intel 4004 的 2,300 个晶体管,到 2025 年 Apple M3 Ultra 的 1,840 亿个,54 年增长了约 8,000 万倍。NVIDIA Blackwell B200 GPU 更是达到了 2,080 亿晶体管。至于摩尔定律是否已死,业界争论不休。一个客观事实是 Dennard 缩放定律在 20072012 年已经失效,频率在 34 GHz 后基本停滞,产业被迫转向多核和架构创新。

从加法器到 ALU:用逻辑门搭出计算器

加法是一切算术运算的起点。

半加器处理 1 位加法,用 1 个 XOR 门算出和(Sum = A⊕B),1 个 AND 门算出进位(Carry = A·B)。但它不能处理来自低位的进位输入。全加器在此基础上增加了 Cin 输入,完整公式是 Sum = A⊕B⊕Cin,Cout = (A·B) + (Cin·(A⊕B))。

把 N 个全加器串联起来,前一级的 Cout 接后一级的 Cin,就得到行波进位加法器。简单粗暴,但进位必须逐级传播,32 位加法延迟约 9.6ns。超前进位加法器(CLA) 通过提前并行计算所有进位信号,把延迟压缩到约 3.3ns,时间复杂度从 O(n) 降到 O(log n)。这是时间换空间(更多硬件)的经典案例。

ALU(算术逻辑单元) 是 CPU 的计算核心,它把加法器、逻辑门、移位器等功能单元整合到一起,通过操作码(opcode) 控制多路选择器来切换运算类型。补码设计在这里展现了极致的优雅:减法只需在加法器的 B 输入端加 N 个 XOR 门,当控制信号 Sub=1 时,XOR 门把 B 每位取反,同时 Sub 连到最低位 Cin(等效 +1),于是 A−B = A + NOT(B) + 1 = A + (B 的补码)。一套硬件同时完成加法和减法。

ALU 运算后还会产生标志位:Z(零标志)、N(符号标志)、C(进位标志)、V(溢出标志)。你代码里写的 if/else、for 循环,在硬件层面就是靠这些标志位实现条件跳转的。

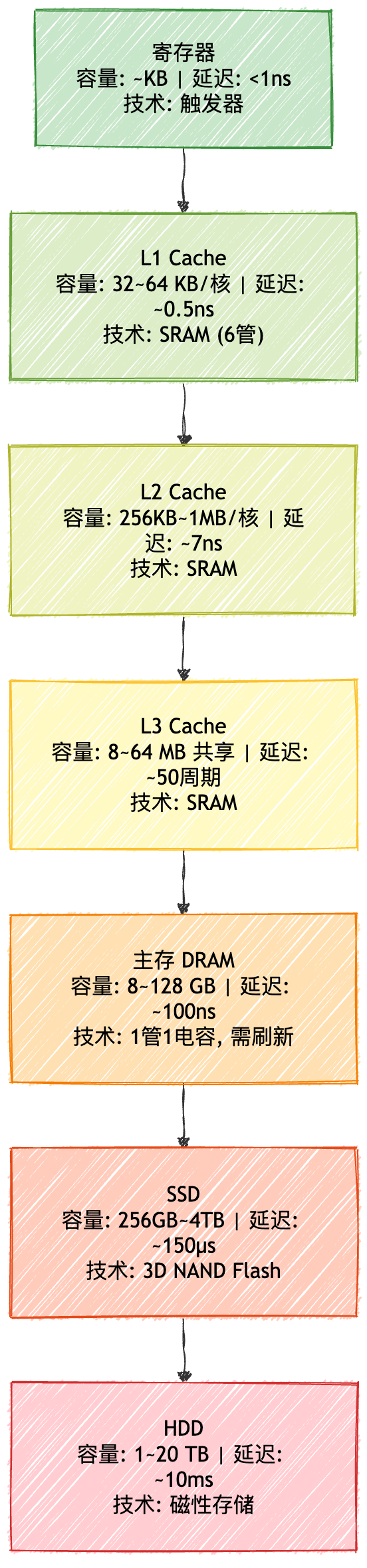

存储的层次:速度和容量的永恒博弈

存储 1 位信息的核心器件是 D 触发器。两个交叉耦合的 NOR 门构成反馈回路,创造双稳态(两个稳定状态),这就是「记忆」的物理本质。D 触发器在此基础上加入时钟控制,数据只在时钟上升沿被捕获,之后即使输入变化,输出也锁定不动。64 个 D 触发器并联共享时钟,就是一个 64 位寄存器。

计算机面临一个根本矛盾:快的存储贵且小,便宜的存储慢且大。解法是存储器层次结构,利用程序的局部性原理(刚访问的数据可能再次被访问,相邻数据可能依次被访问)做分层缓存。

SRAM 和 DRAM 的结构差异直接决定了它们的分工。SRAM 用 6 个晶体管构成双稳态触发器,读取非破坏性,速度极快但密度低、成本约 5000/GB,所以只能用在缓存这种「小而快」的场景。DRAM 用 1 个晶体管 + 1 个电容,电荷代表 0 和 1,读取是破坏性的(电荷共享后必须回写),需要定期刷新,但密度极高、成本仅 1~3/GB,适合做大容量主存。

一个直观感受:遍历 int[10000][10000] 的二维数组,按行序访问(利用空间局部性)比按列序(每次跳 10000 个 int)快约 200 倍。这完全是缓存局部性的力量,跟算法本身没有关系。

CPU 指令周期:计算机的「心跳」

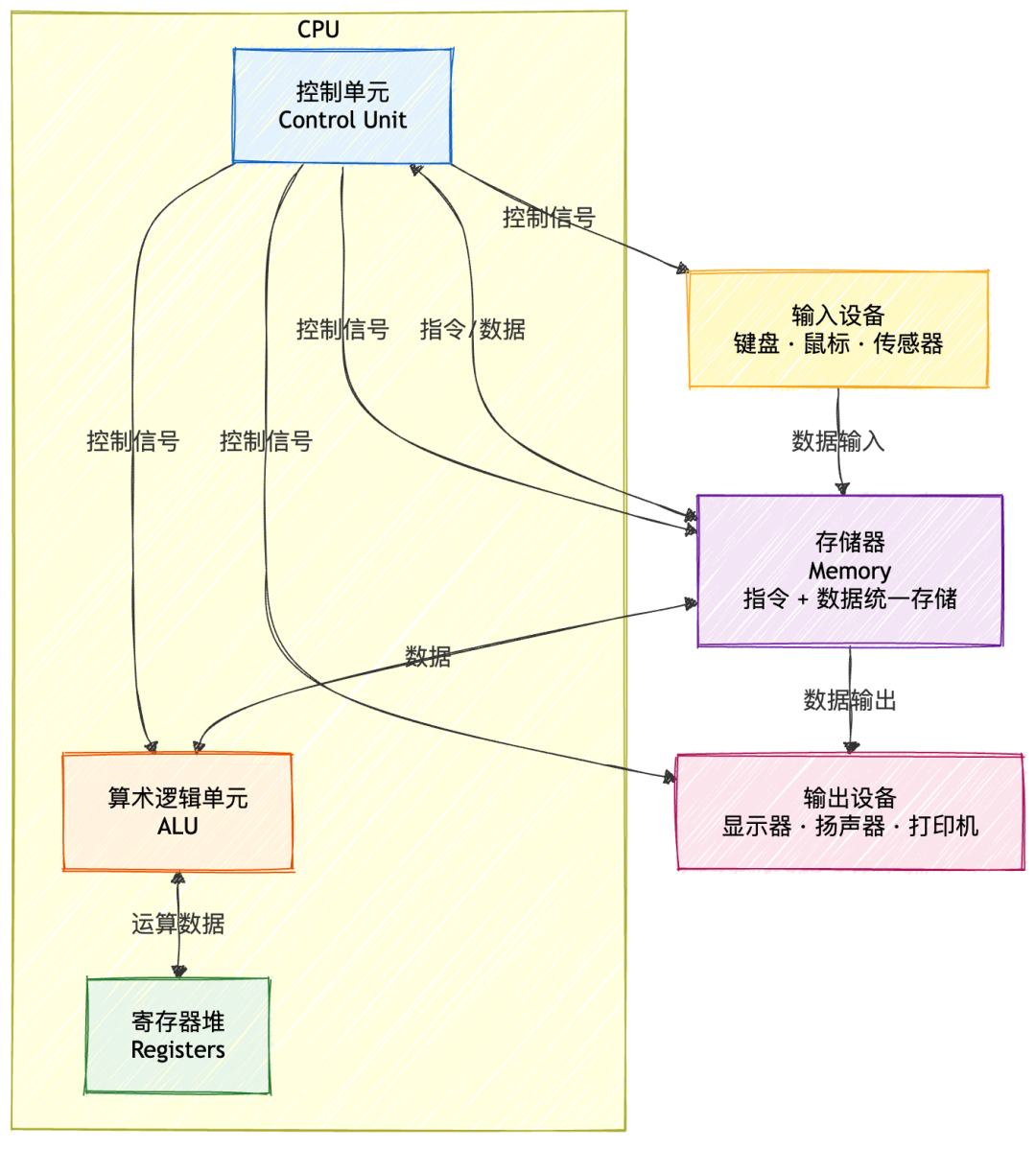

1945 年冯·诺依曼在 EDVAC 报告中提出了存储程序概念:程序指令和数据存在同一个内存里,CPU 从内存依次取出指令并执行。这让计算机从「固定用途机器」变成「可编程通用机器」,影响延续至今。冯·诺依曼架构的五大部件关系如下:

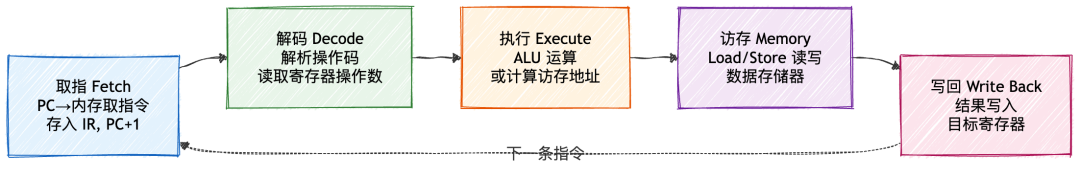

每条指令经历的经典流程如下:

拿 ADD R1, R2, R3 这条指令来说:Fetch 阶段从内存取回 32 位指令编码;Decode 识别出是 ADD 操作,从寄存器堆读取 R2 和 R3 的值;Execute 阶段 ALU 计算 R2+R3;MEM 阶段无操作(这不是访存指令);WB 阶段把结果写入 R1。

时钟信号是这个流程的节拍器。1 GHz 时钟意味着每个周期 1ns。但性能并非只看频率,CPU 性能公式是指令数 × CPI(每指令周期数)÷ 时钟频率。Intel Pentium 4 当年用 31 级超深流水线追求高频率,结果因为热问题翻车,标志着「频率竞赛」时代终结。

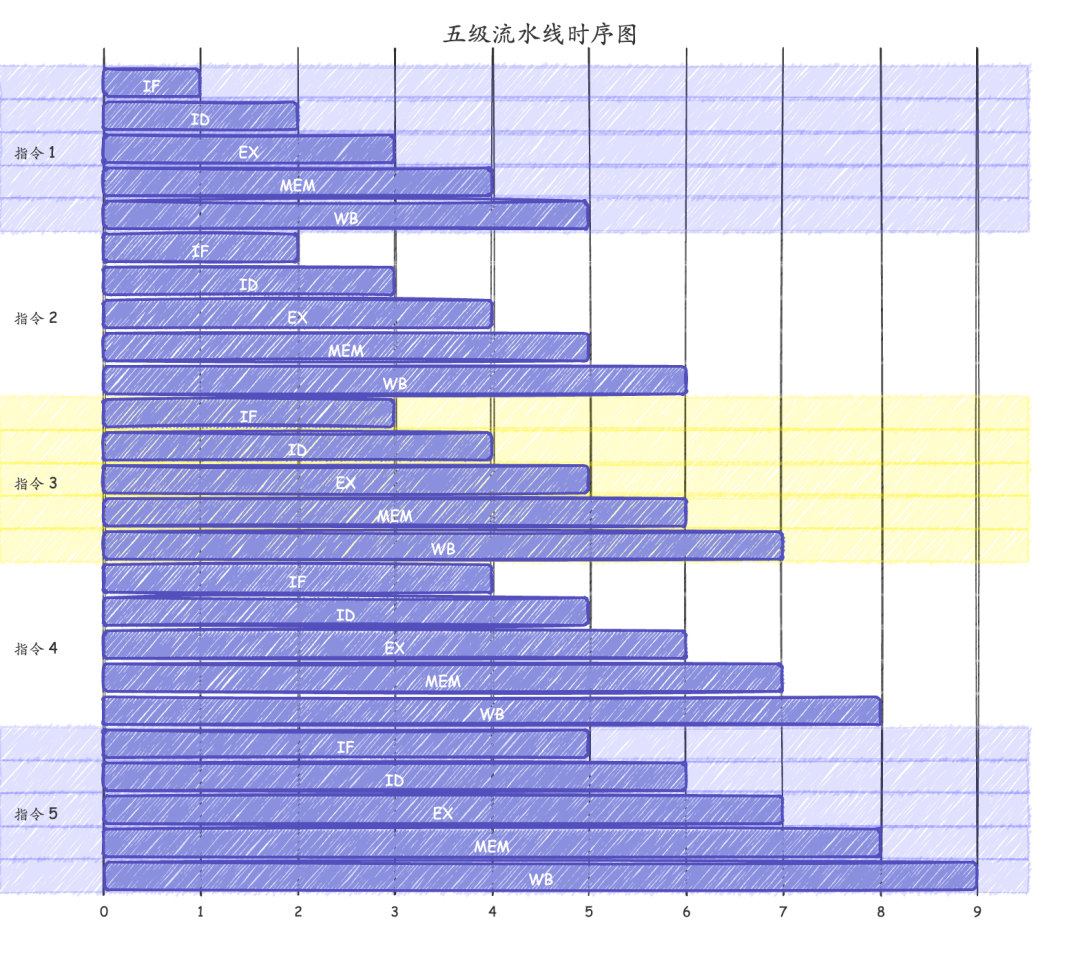

▶流水线:像工厂装配线一样工作

**流水线**的核心思想像工厂装配线:指令 1 在 Execute 时,指令 2 同时 Decode,指令 3 同时 Fetch。理论上 5 级流水线吞吐量可达每周期 1 条指令。下面这张时序图展示了流水线的精髓,没有流水线时 5 条指令需要 25 个周期,有了流水线只需 9 个周期:

但流水线不是免费午餐,它会遇到三种「冒险(Hazard)」:

结构冒险(Structural Hazard):多条指令同时需要同一个硬件资源。最典型的例子是哈佛架构之前的冯·诺依曼瓶颈——指令 1 在 MEM 阶段访问内存读数据,指令 4 同时在 Fetch 阶段也要访问内存取指令,但内存端口只有一个,打架了。解法很直接:把指令缓存(I-Cache)和数据缓存(D-Cache)分开,各走各的通道。现代 CPU 的 L1 缓存几乎都是指令/数据分离设计,就是为了从物理上消灭这类冲突。

数据冒险(Data Hazard):后续指令依赖前面指令还没算出来的结果。比如连续两条指令 ADD R1, R2, R3 和 SUB R4, R1, R5,第二条要用 R1,但第一条还在流水线里没写回。解法是转发/旁路(Forwarding/Bypassing):ALU 算完的结果不等写回寄存器堆,直接从流水线中间「抄近道」送给下一条指令。硬件上就是在流水线各级之间加旁路通路。但有些情况转发也救不了,比如 LOAD R1, [addr] 紧接着 ADD R2, R1, R3,内存数据在 MEM 阶段才拿到,而 ADD 在 Execute 阶段就需要——这时候必须插入一个流水线气泡(Pipeline Bubble/Stall),强制等一个周期。编译器优化时会尝试在 LOAD 和依赖它的指令之间插入无关指令来填充这个「空档」,这就是所谓的指令调度。

控制冒险(Control Hazard):分支指令(if/else、循环跳转)导致的问题。当 CPU 遇到 BEQ(相等则跳转)时,分支条件要到 Execute 甚至 MEM 阶段才能确定,但后面的 Fetch 早已预取了后续指令——如果分支真的跳转了,这些预取的指令全部作废,流水线必须**冲刷(Flush)**后重新填充。

分支预测技术应运而生。最简单的策略是静态预测:永远猜「不跳转」或「向后跳转」(循环通常如此)。但现代 CPU 用的是动态预测,核心思想是「历史会重演」。从最早的 1 位预测器(记录上次是否跳转),到 2 位饱和计数器(需要连续两次猜错才改主意,避免循环末尾的一次性误判),再到如今的 TAGE(Tagged Geometric History Length)预测器——它同时维护多张不同历史长度的模式表,短历史捕捉简单循环,长历史捕捉复杂的嵌套模式和关联分支。现代高端 CPU 的分支预测准确率超过 95%,Apple M 系列甚至报告过 99%+ 的命中率。

但误预测的代价很高。1020 级流水线意味着每次误判要冲刷 1020 个周期的工作。对于热循环(tight loop)里的关键分支,1% 的误预测率就足以造成显著性能下降。这也是为什么写高性能代码时要注意「分支友好」——比如用无分支的位运算替代 if,或者用 likely/unlikely 提示编译器调整代码布局。(这些我基本没用过)

2018 年曝光的 Spectre/Meltdown 漏洞就是分支预测与推测执行(Speculative Execution)的安全副作用。CPU 在预测分支走向后会「先斩后奏」地执行推测路径上的指令,虽然误预测后结果会被丢弃,但执行过程中留下的缓存侧信道痕迹(某些内存地址被加载进缓存,访问速度变快)可以被攻击者利用来窃取敏感数据。这个漏洞影响了几乎所有主流 CPU,修复补丁一度导致部分工作负载性能下降 5%~30%。

▶现代 CPU 的并行技术

现代 CPU 在流水线基础上还叠加了多项技术,把指令级并行性(ILP)榨到极致:

乱序执行(Out-of-Order Execution):传统流水线按程序顺序执行指令,一条指令被卡住(比如等缓存未命中的数据),后面所有指令都得干等。乱序执行打破了这个限制——CPU 内部有一个保留站(Reservation Station),所有已解码的指令在这里等待操作数就绪;一旦操作数到齐,无论原始程序顺序如何,立刻发射执行。执行完毕后,结果进入重排序缓冲区(ROB, Reorder Buffer),按原始程序顺序提交,确保外部可见的行为仍然和顺序执行完全一致。打个比方:你在食堂排队打饭,虽然轮到你时鱼香肉丝还没做好,但宫保鸡丁已经好了,窗口阿姨先给你打鸡丁,不用傻等——最终你端走的托盘上菜的「排列顺序」还是你点单的顺序。Robert Tomasulo 在 1967 年为 IBM System/360 Model 91 发明了这套算法,至今仍是所有现代乱序处理器的理论基础。Apple M4 的 ROB 深度据报道超过 600 条指令,意味着 CPU 可以同时「记住」600 条指令的执行状态。

超标量(Superscalar):流水线让每周期「完成」一条指令,超标量则让每周期同时「发射」多条指令。CPU 内部配备多个执行单元(多个 ALU、多个浮点单元、多个 Load/Store 单元),硬件调度器在每个周期从指令窗口中挑出多条互不依赖的指令并行发射。现代高性能 CPU 通常是 6~8 发射宽度——理论上每周期可以同时执行 68 条指令。Apple M4 的性能核(Everest)据称达到了 10 发射宽度。当然,实际 IPC(每周期指令数)受限于数据依赖和资源冲突,通常达不到理论峰值,典型值在 24 左右。

SMT/超线程(Simultaneous Multithreading):即使有了乱序执行和超标量,单线程程序中的指令级并行性终归有限,执行单元经常出现「空档」。SMT 的思路是让一个物理核心同时维护多个线程的架构状态(各自独立的程序计数器、寄存器组),当线程 A 的指令在等缓存数据时,线程 B 的指令可以填补空闲的执行单元。Intel 称之为 Hyper-Threading,一般每个物理核跑 2 个逻辑线程,在多线程工作负载下可以带来 15%~30% 的吞吐提升。但注意,SMT 不是变出了两个核心——两个线程共享同一套执行资源和缓存,如果两个线程都是计算密集型的,反而会因为资源争抢而相互拖累。Apple 在 M 系列芯片中选择完全不用 SMT,转而靠更宽的超标量和更大的乱序窗口来榨取单线程性能,这是一种不同的设计哲学。

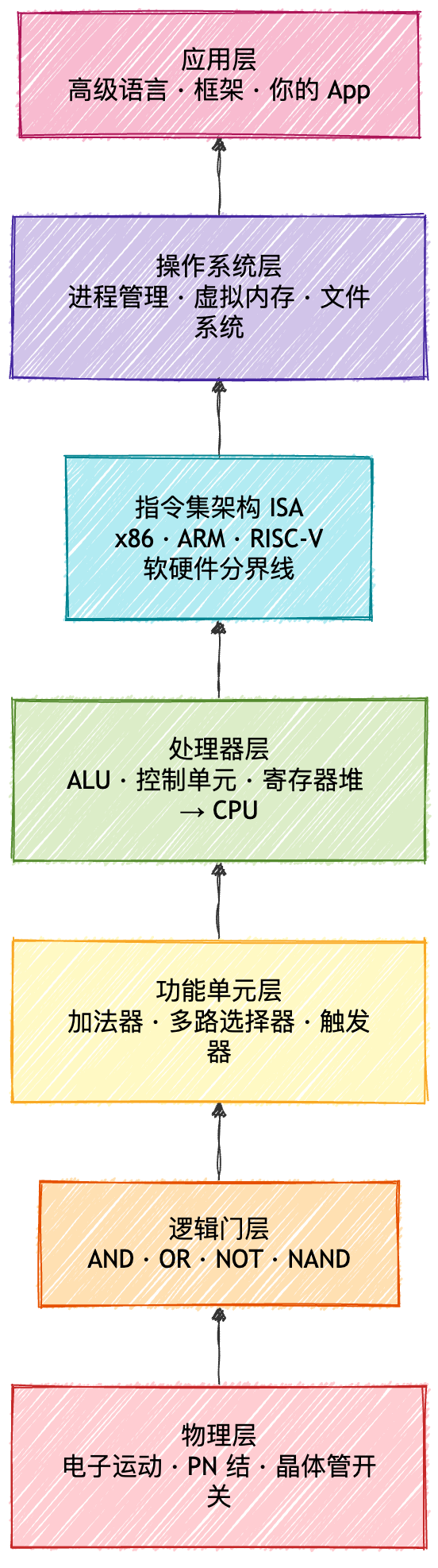

七层抽象:从沙子到 App 的宏伟阶梯

计算机系统最深刻的设计哲学是抽象。每一层隐藏下层的复杂性,只暴露简化接口给上层。

这里面最关键的分界线是 ISA(指令集架构)。它是一份契约,定义了处理器支持哪些指令、数据类型、寄存器和寻址模式,但不规定硬件怎么实现。同一套 x86 ISA,Pentium 4 和 Core i7 的微架构完全不同,但跑的软件一样。当前三大 ISA 生态分别是 x86(Intel/AMD 主导 PC 和服务器)、ARM(占据 99% 智能手机,Apple M 系列证明它可以硬刚桌面性能)、RISC-V(2010 年 UC Berkeley 开源,免授权费,NVIDIA GPU 内部已用了多达 40 个 RISC-V 核心)。

一行 C 代码 a = b + c; 要变成电信号,需要经过预处理→编译(生成汇编)→汇编(生成机器码)→链接(合并目标文件)四步。最终每条机器指令就是一串 0 和 1,CPU 的控制单元解码这些比特模式,驱动 ALU 和寄存器完成运算。

操作系统则是硬件之上的「大管家」。进程调度、虚拟内存、文件系统,通过系统调用为上层提供统一接口。正是操作系统让程序员不用关心物理内存地址或磁盘扇区,只需调用 read()、malloc() 就够了。

超越冯·诺依曼:GPU、AI 芯片和未来

冯·诺依曼架构有个根本限制:CPU 和内存物理分离,数据搬运的能耗是浮点运算的 100 倍。在 AI 时代,这个瓶颈越来越明显。

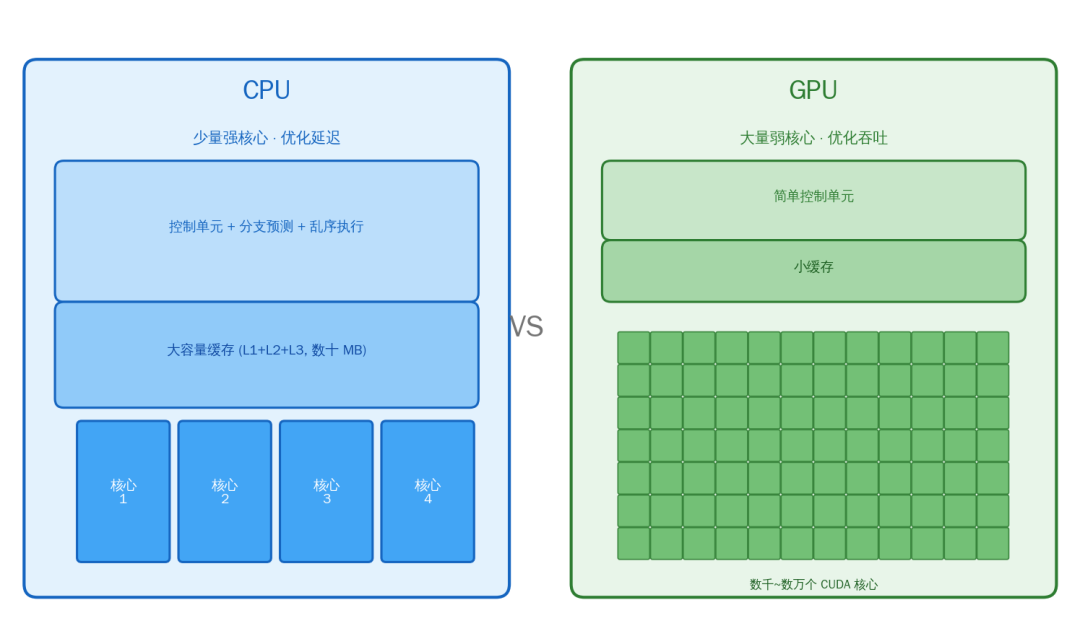

GPU 走的是「用数千弱核心换吞吐量」的路线。CPU 是几十个复杂核心优化延迟,GPU 则是数千个简单核心优化并行吞吐。

NVIDIA H100 有 16,896 个 CUDA 核心,Blackwell B200 更达 2,080 亿晶体管。深度学习的核心操作就是大规模矩阵乘法,天然适合 GPU 的 SIMT 并行模型。

Google TPU 的核心是 256×256 脉动阵列,包含 65,536 个乘加单元。数据像心脏搏动一样有节奏地流过处理单元网格,每个单元做一次乘加后把结果直接传给邻居,最大化数据复用、最小化内存访问。

更前沿的方向包括**存内计算(把计算搬到数据所在位置,用忆阻器交叉阵列天然实现矩阵-向量乘法)、类脑计算(事件驱动的脉冲神经网络,IBM NorthPole 2023 年展示了比传统架构高数个量级的能效)、以及量子计算**(Google Willow 2024 年实现指数级纠错里程碑)。

思维拓展:AI 的发展是不是同一个故事?

回头看这篇文章的主线——晶体管→逻辑门→加法器→ALU→CPU→操作系统→应用——你会发现一个反复出现的模式:极其简单的基本单元,通过大规模组合和层层抽象,涌现出远超单个单元能力的复杂行为。晶体管不「懂」数学,但数十亿个晶体管组成的 CPU 能解微分方程。

AI 的发展,本质上是同一个故事的翻版。

一个人工神经元做的事情简单到可笑:接收若干输入,乘以各自的权重,求和,过一个激活函数,输出一个数。就这样。它比一个 NAND 门复杂不了多少。Frank Rosenblatt 在 1958 年造出的感知机只能做最简单的线性分类,连 XOR 问题都解决不了——Marvin Minsky 1969 年的证明直接把 AI 送进了第一个「寒冬」。

但把这些简单单元堆叠起来,情况就不一样了。多层感知机解决了 XOR;卷积神经网络(CNN)学会了「看」图像;循环神经网络(RNN)学会了处理序列;2017 年 Google 的 Transformer 架构用纯注意力机制取代了循环结构,从此打开了大语言模型的大门。每一步都是在前一层抽象的基础上搭积木,跟从 NAND 门到 CPU 的路径如出一辙。

对照关系如果你有兴趣可以看看,会发现惊人的相似:

计算机硬件 | AI / 深度学习 |

|---|---|

晶体管(开/关) | 人工神经元(加权求和 + 激活) |

逻辑门(AND/OR/NAND) | 网络层(全连接层、卷积层、注意力层) |

ALU / CPU | 深度学习架构(CNN、Transformer) |

指令集架构(ISA) | 框架 API(PyTorch、TensorFlow) |

操作系统 | 基础模型(GPT、Claude) |

应用程序 | AI 应用(对话、代码生成、图像生成) |

两条路径上都存在同样的涌现现象。CPU 的晶体管数量从 2300 增长到 2000 亿,带来的不只是「更快」,而是从计算器到智能手机的质变。类似地,当语言模型的参数从百万级跨到千亿级,突然出现了训练目标里从未明确要求的能力——推理、翻译、写代码、角色扮演。这种「涌现能力」让研究者自己都感到意外,就像没人设计 NAND 门的时候预想到它最终能跑出一个操作系统。

甚至连撞墙的方式都如出一辙。前面讲过,CPU 在 20072012 年撞上了 Dennard 缩放定律的墙——频率卡在 34 GHz,再往上提功耗和散热就扛不住了,「频率竞赛」宣告终结,产业被迫转向多核、异构和架构创新。AI 领域现在正在经历几乎一模一样的剧情。2020 年 OpenAI 提出的 Scaling Law 曾是行业信仰:模型越大、数据越多、算力越强,性能就越好,简单粗暴地「堆规模」就行。但到了 2024~2025 年,越来越多的迹象表明这条路也在撞墙——高质量训练数据逐渐枯竭、万卡集群的算力成本已经高到令人咋舌、而模型能力的提升曲线开始明显放缓。单纯加参数带来的边际收益在递减,就像当年单纯提频率一样。

CPU 撞墙后的出路是架构创新:多核、乱序执行、超标量、GPU 加速。AI 撞墙后的出路也在向类似方向演化:混合专家模型(MoE) 让每次推理只激活部分参数,用更少的计算量换等效大模型的能力;测试时计算(Test-time Compute) 把算力从训练阶段转移到推理阶段,让模型在回答前「多想一会儿」,类似 CPU 的推测执行——先花时间探索多条路径,再选出最优解;蒸馏和剪枝则像芯片设计中的功耗优化,用更小的模型逼近大模型的性能。本质上都是同一个转向:从「堆规模」转向「提效率」,从暴力扩展转向精巧设计。

历史不会简单重复,但押韵得惊人。

还有一个更深的相似点:两者都「不理解」自己在做什么。晶体管不知道自己在做加法,CPU 不知道自己在播放视频。同样,Transformer 不知道自己在「理解」语言——它只是在根据上文的 token 序列预测下一个 token 的概率分布。但从外部观察,这种大规模的简单操作叠加产生的行为,跟「理解」已经越来越难以区分。这也是为什么「AI 是否真的在思考」这个问题如此难以回答——我们其实对「思考」本身的定义就不够清晰。

从这个角度看,前面整篇文章讲的「从 0 和 1 到复杂计算」,不只是计算机硬件的故事,更像是一种普遍的工程哲学:找到正确的基本单元,设计正确的组合规则,然后让规模去创造奇迹。Shannon 用布尔逻辑桥接了数学和电路,Rosenblatt 用感知机桥接了神经科学和计算,Vaswani 等人用注意力机制桥接了序列建模和并行计算。每一座桥都遵循同样的原则:简单、可组合、可扩展。

写在最后

回到这个问题本身。计算机不「思考」,它只是在以人类难以想象的速度翻转数十亿个开关。但正是通过层层抽象,从晶体管到逻辑门,从加法器到 ALU,从 CPU 到操作系统,人类把最简单的 0 和 1 堆叠成了能跑大语言模型、能渲染 3D 世界的系统。Petzold 说得好,计算机具有「与生俱来的层次结构」。

这条从沙粒到智能的路径,Shannon 在 1937 年建立的那座桥(布尔逻辑与物理电路的映射)仍然是地基。无论架构怎么演变,NAND 门、加法器、指令周期这些最底层的积木并没有被推翻,只是被更高效地组合和堆叠。理解这些底层原理,对写好上层代码确实有帮助。你会更清楚为什么数组按行遍历比按列快、为什么浮点比较不能用 ==、为什么分支预测失败会拖慢热循环。知其然更知其所以然,代码才能写到骨头里去。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-05,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录