瓜大三哥

作者相关精选

桶形移位寄存器(二)

前往小程序,Get更优阅读体验!

立即前往

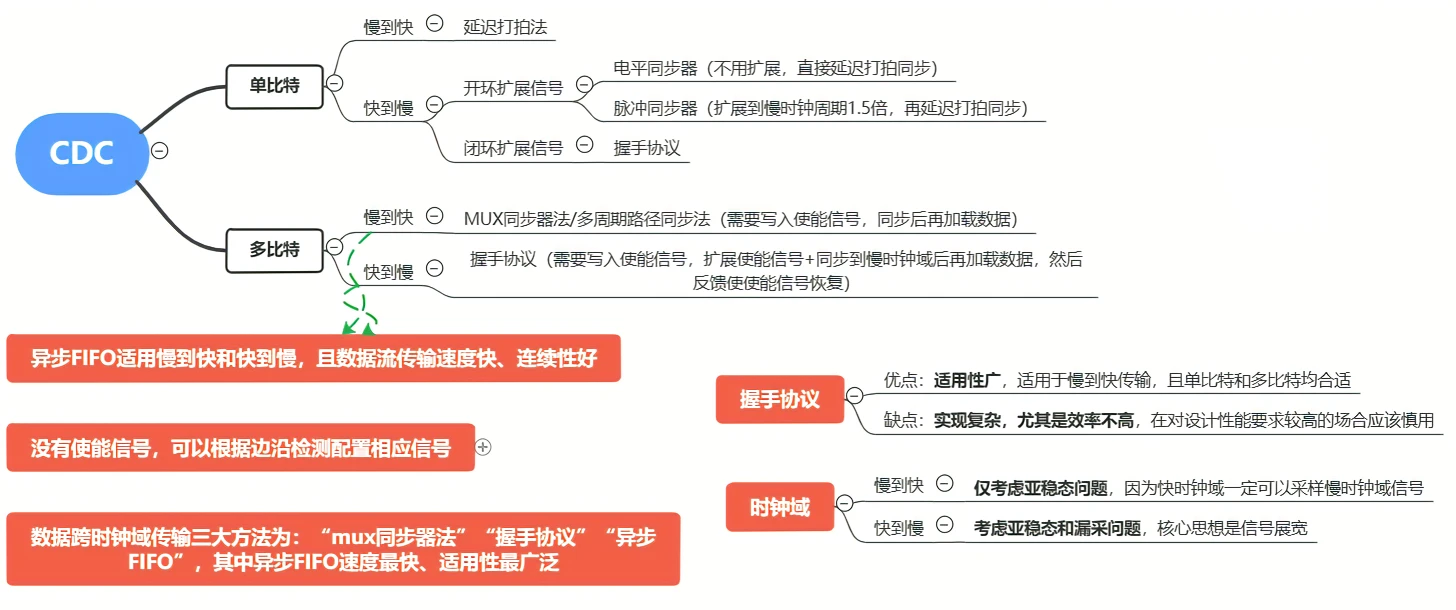

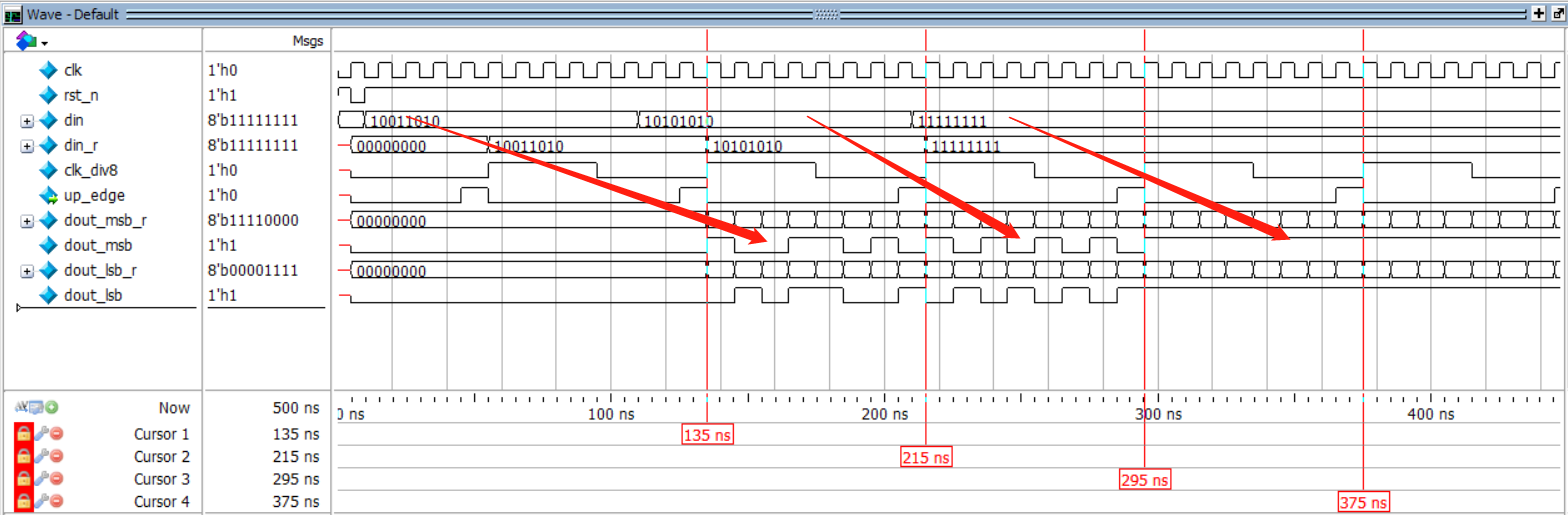

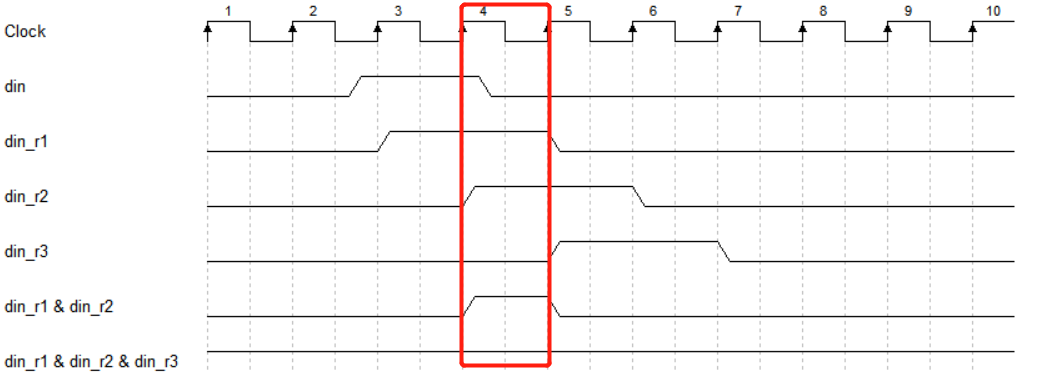

桶形移位寄存器即循环移位寄存器,在浮点加减运算、压缩/解压缩和图像处理算法中有应用,常用的是组合逻辑实现的桶形移位寄存器。

从面积的角度来说,这种设计方式的确可以节省资源,但是在高速时序电路中,这样的设计就很不合理了。

代码语言:js

AI代码解释

复制

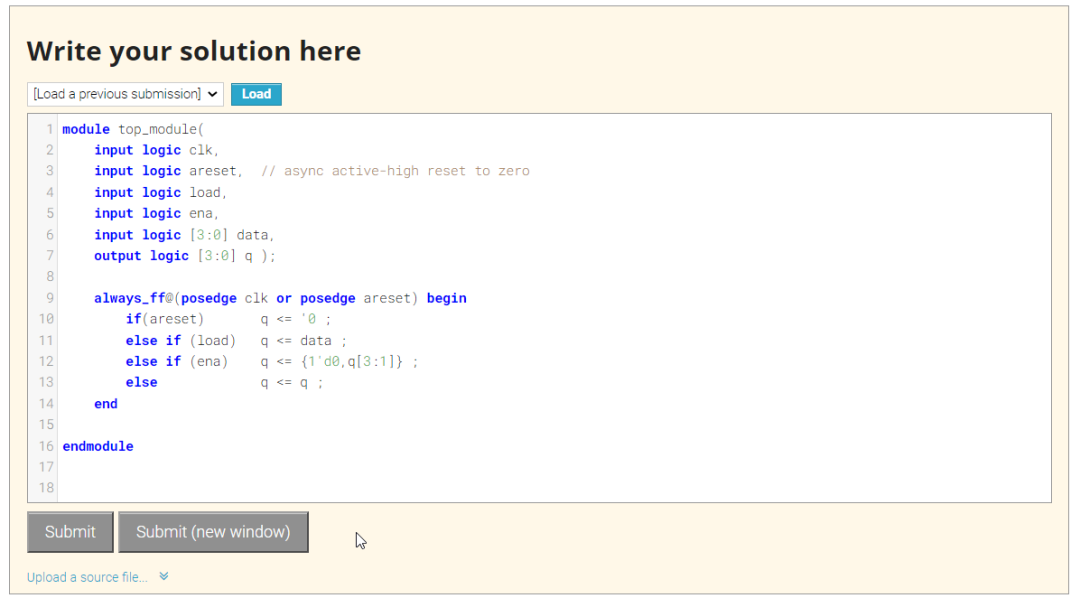

module bshift(

clk,

rst,

din,

rotate_cnt,

dout

);

parameterWIDTH = 8;

parameterCNT_SIZE = 3;

inputclk,rst;

input [CNT_SIZE -1 : 0] rotate_cnt;

input [WIDTH - 1 : 0] din;

output [WIDTH - 1 : 0] dout;

reg [WIDTH - 1 : 0] dout;

wire [WIDTH - 1 : 0] barrel,temp;

wire [2*WIDTH - 1 : 0] bar_temp;

assign bar_temp = {din,din}<<rotate_cnt;

assign {barrel,temp} = {din,din}<<rotate_cnt;

always @(posedge clk or posedge rst)

begin

if(rst)

dout<='b0;

else

dout<=barrel;

end

endmodule

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2017-08-08,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

暂无评论

登录 后参与评论

推荐阅读

编辑精选文章

换一批

相关推荐

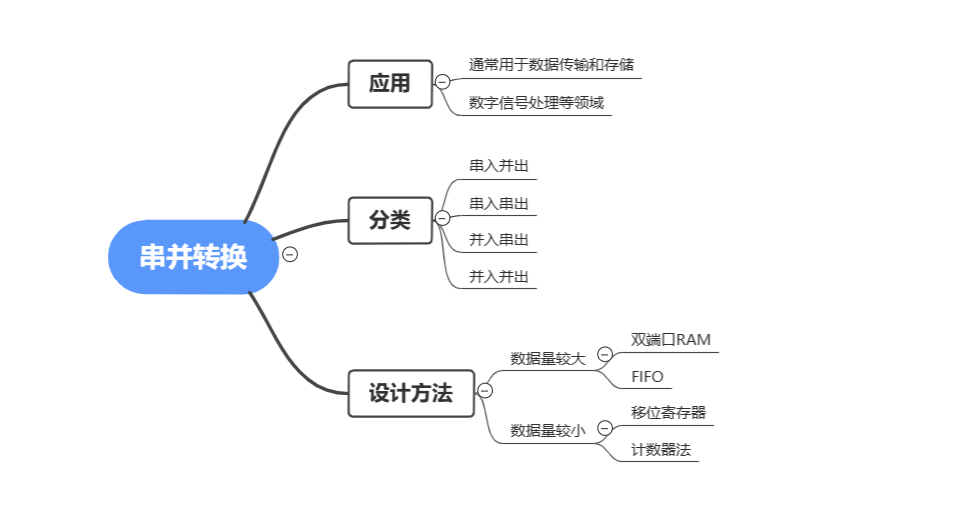

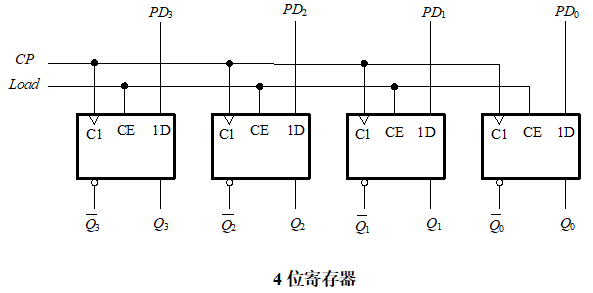

九种移位寄存器原理与设计(循环(左、右、双向)移位寄存器、逻辑和算术移位寄存器、串并转换移位寄存器、线性反馈移位寄存器LFSR)

更多 >领券

社区富文本编辑器全新改版!诚邀体验~

全新交互,全新视觉,新增快捷键、悬浮工具栏、高亮块等功能并同时优化现有功能,全面提升创作效率和体验

腾讯云开发者

扫码关注腾讯云开发者

领取腾讯云代金券

Copyright © 2013 - 2025 Tencent Cloud. All Rights Reserved. 腾讯云 版权所有

深圳市腾讯计算机系统有限公司 ICP备案/许可证号:粤B2-20090059 深公网安备号 44030502008569

腾讯云计算(北京)有限责任公司 京ICP证150476号 | 京ICP备11018762号 | 京公网安备号11010802020287

Copyright © 2013 - 2025 Tencent Cloud.

All Rights Reserved. 腾讯云 版权所有

登录 后参与评论

9

![verilog序列生成器最少移位寄存器实现[通俗易懂]](https://ask.qcloudimg.com/http-save/yehe-8223537/e22ee4ee703ad5515b5c29eb5cfc56af.jpg)

![08【Verilog实战】4bit移位寄存器设计与功能验证(附源码)[通俗易懂]](https://ask.qcloudimg.com/http-save/yehe-8223537/aca87c7de1e7a026ca6103edf2811400.jpg)