使用多少个CUDA核心来处理CUDA偏差?

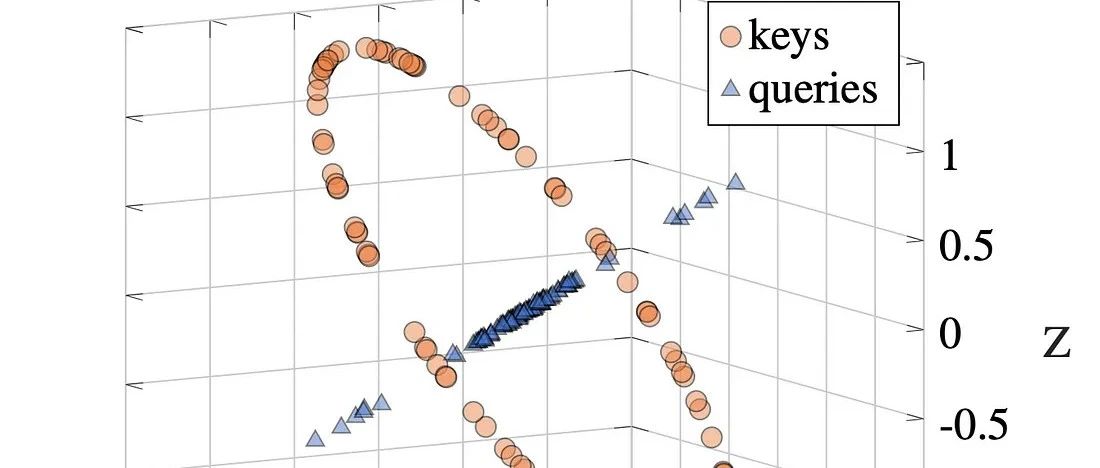

我正在寻找答案,但有一些冲突的想法:在这个链接https://www.3dgep.com/cuda-thread-execution-model/中,两个warps (64个线程)可以在SM (32个CUDA内核)上同时运行。因此,据我所知,warp上的线程被拆分并在16个CUDA内核上进行处理。这个想法对我来说很有意义,因为每个CUDA核心都有1个32bitALU。

然而,在其他链接中,他们声称1CUDA核心能够处理32个并发线程(与warp大小相同) (https://cvw.cac.cornell.edu/GPU/simt_warp)。因此,1个CUDA warp只能由一个CUDA内核处理。这也是有意义的,因为所有线程在相同的曲轴上使用相同的PC计数器。

那么,我的问题是如何将CUDA偏差映射到CUDA核心?

回答 1

Stack Overflow用户

发布于 2020-06-02 20:31:43

Inside a CUDA GPU,有称为短消息(流多处理器)的计算单元。每个SM具有各种硬件资源(warp调度器、指令获取/解码、寄存器文件、执行/功能单元、共享存储器、L1高速缓存等)。它们用于支持CUDA执行线程。

无论何时发出指令,它都是在warp范围内发出的。因此,发出的任何指令都需要该类型指令的32个功能单元。CUDA低级指令(SASS)可以分为多个类别,并且有一个功能单元类型来处理该指令或该类别中的指令。例如,从内存加载指令(例如LD)将由LD/ST单元(加载/存储)处理。有许多不同种类的这些指令处理单元。

一些额外的particular kinds of units are SP and DP units。SP单元可以处理单精度浮点乘法、加法或乘加指令。DP单元类似,只是它处理双精度浮点类型的指令。

因此,为了发出指令,warp调度器最终将需要32个适合于该指令类型的单元类型。对于单精度浮点乘法运算,需要在该周期内有32个SP单元可用来接收发出的指令。

其他类型的指令(最终)仍需要32个单元,但SM中可能没有32个给定类型的单元。当特定类型的单元少于32个时,warp调度器将跨多个时钟周期调度单个指令。例如,假设特定的GPU SM设计是这样的,即只有4个DP单元。然后,当warp调度器有例如DP乘法运算/指令要发出时,它将在总共8个时钟周期(4x8=32)中使用这4个单元,以便在考虑每线程、warp宽度时为每个指令提供功能/执行单元。每个线程最终都需要一个功能单元。每个功能单元可以为每个时钟处理一个线程的一条指令。为了处理在warp范围内发布的指令,将需要32个功能单元,以便可以在单个时钟周期中发布指令,或者将在多个时钟周期上将指令发布到较少数量的功能单元。

CUDA中的术语“核心”通常用于指如上所述定义的SP单元。鉴于此,我们可以立即确定:

- 一个CUDA“核心”真的不像CPU核心。

- 仅涉及相对较少的指令类型的指令处理,包括SP浮点加法、乘法和乘法加法。任何其他指令类型都将需要不同类型的功能单元来处理该指令。并且仅仅因为SM包含例如128个CUDA核心(即SP单元),并不意味着它还包含128个DP单元、或128个LD/ST单元、或特定数量的任何其他功能单元类型。SM中的功能单元的数量可以而且确实随功能单元类型而变化。不同的图形处理器架构(Maxwell,Pascal,Volta)和架构内的不同计算能力,可能具有不同的混合或数量的这些功能单元类型。

https://stackoverflow.com/questions/62147624

复制

![aws s3 java SDK使用[通俗易懂]](https://ask.qcloudimg.com/http-save/yehe-8223537/ea304075b3a916f8da1505f2862d9a9c.jpg)