故障安全RAM驱动解决方案

我正在寻找一个生产解决方案,以创建一个RAM驱动器,将安全地与HDD同步。

我有一个带有大量I/O负载的定制软件(这是一种专用的面向文档的DB),我需要大大加快它的速度。我不能修改或摆脱软件本身,所以必须做水平或垂直缩放。这个软件不支持水平搜索框,所以我首先看垂直缩放。

其主要思想很简单--我们购买大量的RAM (96 we ),并把整个东西放在一个RAM驱动器上。但是它必须是故障安全的,在服务器重新启动时丢失任何数据都不是一种选择。因此,我正在寻找的解决方案,将保持透明的同步之间的RAM驱动器和硬盘。

脏的解决方案,如通过bash脚本复制文件不是一个选项,需要一些更可靠的东西。

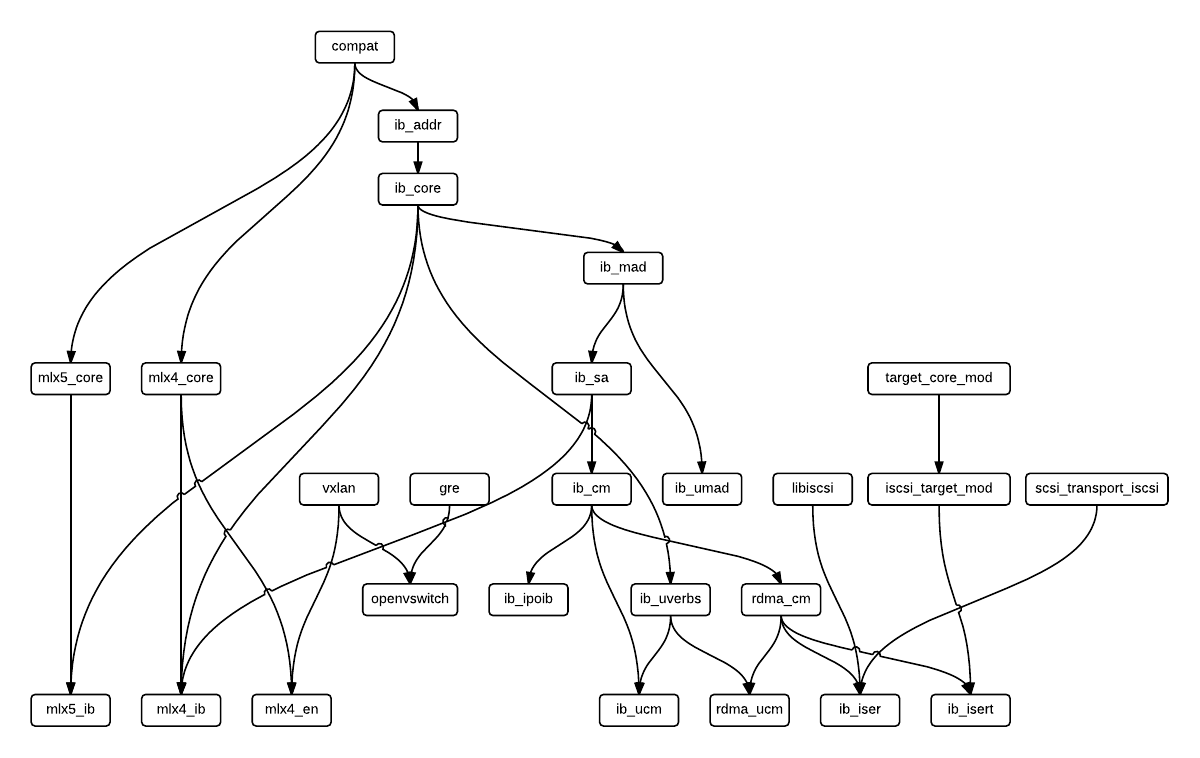

在理论上,正如我所看到的,某种类似于描述的这里的分布式FS可以以一种奇怪的方式使用--同步同一台机器上的两个分区。但我怀疑这是否会在实践中奏效,但我从未尝试过。

那么,对于具有透明同步硬盘的RAM驱动器的现成解决方案,有什么想法吗?

数据UPD:

- 估计我需要在RAM中保存的数据量约为50 in。

- 服务器是专用的HP DL320,8 CPU,16 HP内存(高达96 HP)。

- I/O配置文件类似于数据库应用程序--大量的随机访问读取,更少的写入。

回答 2

Server Fault用户

发布于 2012-11-01 06:12:05

我询问了您可以使用的硬件,因为可以获得低延迟和高IOPS设备来克服磁盘的限制。

但是,您没有提供对工作数据集大小的估计。这就产生了很大的不同。我们目前没有足够的信息。应用程序的I/O配置文件是什么?有写作偏见吗?有阅读偏见吗?当前的存储设置是什么?

一般的建议是使用一系列SSD驱动器。另一种方法是使用PCIe加速器,比如FusioIO驱动器。

甚至可以考虑异步模式下的DRBD .

一个更深奥的解决方案是使用共享存储,这种存储具有一定的层次,可以将常用的数据保存在内存或SSD中。ZFS文件系统及其使用的齐尔写加速和L2ARC读缓存就是一个很好的例子。

更深奥的解决方案是一种基于软件的缓存方法,比如最终持久Ram磁盘(EPRD)。这会在FUSE文件系统中创建一个磁盘支持的RAM磁盘,并且对于加速应用程序的I/O可能是一个很好的选择。

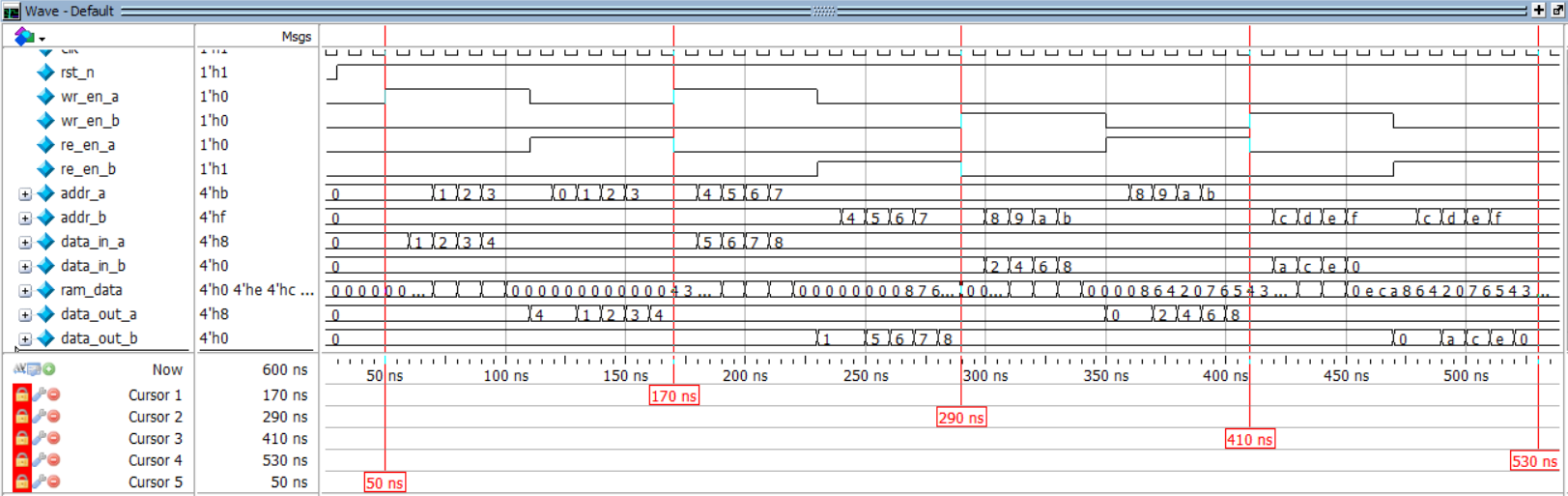

在配置文档中:

You can however also create a ramdisk that will have it's

changes flushed to disk every N seconds and instead of keeping

everything in ram it only allocated 512M for caching.

./eprd_setup -f /data/saverimg -s 10G -m 3 -c -p512M

In this example the data is flushed to disk every 3 seconds.编辑:

如果这些是HP ProLiant DL320系统,我假设它们是G6模型。您是否安装了智能阵列P410控制器和电池支持或闪存缓存?如果不是,这是在使用RAM磁盘安装之前应该采取的第一步。这就不一样了!

Server Fault用户

发布于 2012-11-01 05:43:21

你不想有一个实际的RAM磁盘与硬盘同步-你想要的是一个基于RAM的PCIe卡与电池备份和NV缓存。基本上是一张FusionIO卡。

https://serverfault.com/questions/444362

复制